10.5运用FPGA完成A/D、D/A转化器接口

10.5.1A/D、D/A转化器接口的特色

A/D、D/A转化器是FPGA体系规划中的常用器材,常常用来完成模拟信号和数字信号的彼此转化。根据运用场合的不同,A/D、D/A转化芯片的功能指标参数不同比较大,因而接口格局也无法统一。

10.5.2A/D、D/A转化器接口的完成办法

1.规范接口的A/D、D/A转化器与FPGA的接口规划

在一些典型的运用范畴,需求处理的信号单一,芯片厂家规划的芯片一般会遵从一些职业规范接口。例如音频信号处理范畴,许多厂家的音频A/D、D/A转化芯片都支撑SPI接口。

FPGA完成这些规范的接口,如SPI接口,能够通过网络或许FPGA厂家取得一些参阅代码。FPGA芯片的生产厂家会在其开发工具软件里边集成一些常用接口的IP核,规划者能够免费运用,降低了开发难度。

别的,有一些开源的网站,如http://www.opencores.org等,也供给了免费的接口IP核的源代码下载服务。规划者能够下载代码后,通过仿真验证或许恰当修改后,运用到自己的体系中去。

2.特别接口的A/D、D/A转化器与FPGA的接口规划

还有许多信号处理范畴,如通信体系规划范畴,需求处理的信号很杂乱。这种情况下,A/D、D/A的芯片厂家一般会根据处理的精度和采样的速度要求来规划接口时序。

规划者要根据厂家供给的芯片手册给出的时序来规划接口。

有些高速的A/D或许D/A芯片会选用LVDS差分信号电平规范。这样的情况下,FPGA的管脚也要选用对应的LVDS形式。

需求留意的是,FPGA上每一组LVDS管脚是成对呈现的,不是恣意分组的。并且,假如一个BANK被设定为LVDS,那么这个BANK的一切管脚都是LVDS形式的。

10.5.3AD/DA转化器接口的留意事项

1.挑选正确的时钟采样边缘

关于一个边缘采样的数据收集模块,常常需求确认选用上升沿仍是下降沿来采样数据。那么,挑选的根据便是确保数据采样的安稳、牢靠。

为了确保同步,FPGA的采样时钟一般选用A/D转化芯片的输出时钟,这个时钟和数据是同步的。这个时钟和数据的联系与A/D转化芯片的具体型号有关。

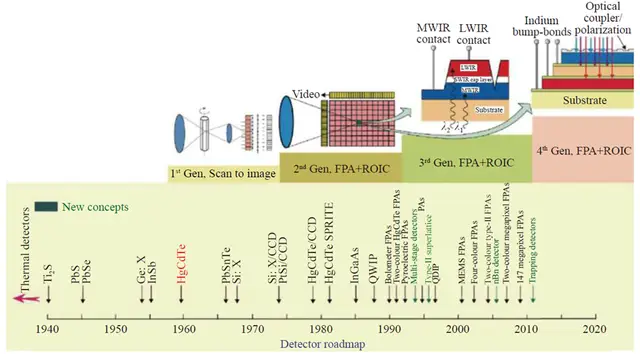

图10.20A/D芯片的部分输出信号时序联系

例如,在如图10.20所示的时序图中,每逢时钟的上升沿数据发生改变。那么这样的情况下,在时钟的下降沿的时分,数据是最安稳的,合适采样。

2.挑选合适的同步头检测办法

A/D芯片的输出数据一般都是打包数据,以数据帧的格局输出。数据帧的同步格局分为两种:外同步形式和内同步形式。

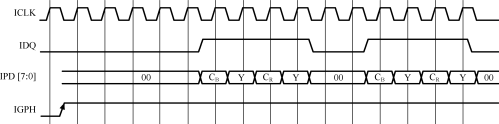

图10.21A/D芯片的部分输出信号时序联系

外同步形式:是指除了时钟和数据信号外,还有同步指示信号。同步指示信号能够是脉冲信号,指示一帧有用数据的开端;也能够是电平信号,指示一帧有用数据的持续时刻。

内同步形式:是指输出信号中只要时钟和数据信号,同步头躲藏在数据之中,如表10.7所示是ITU656规范的数字视频信号。

表10.7 ITU656规范的数字视频信号

|

帧结构 |

||||||||||||

|

BlankingPeriod |

… |

80 |

10 |

|||||||||

|

TimingReferenceCode |

FF |

00 |

00 |

SAV |

||||||||

|

720PixelsYUV4:2:2Data |

Cb0 |

Y0 |

Cr0 |

Y1 |

Cb2 |

Y2 |

… |

Cr718 |

Y719 |

|||

|

TimingReferenceCode |

FF |

00 |

00 |

EAV |

||||||||

|

BlankingPeriod |

80 |

10 |

… |

|||||||||

其间,“FF0000EAV”和“FF0000SAV”便是帧同步头,其效果也是用来指示有用数据开端和完毕。其格局为:“FF0000XY”,XY的界说如下。

SAV_EVEN=8H80

EAV_EVEN=8H9D

SAV_ODD=8HC7

EAV_ODD=8HDA

3.挑选有用的缓存战略

在数据收集体系中,缓存结构的规划直接影响体系的功能。关于简略的规划,能够选用一个FIFO或许双口RAM来完成缓存。假如单缓存不能满意体系的功能要求,能够选用乒乓结构的缓存。

在有些特别情况下,收集模块后边数据处理模块的处理时刻不固定,和数据内容相关。这时分选用乒乓结构的缓存战略就不能满意要求了,由于乒乓结构的切换时刻一般是固定的,并且和数据内容是无关的。

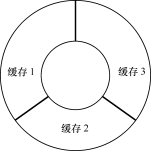

还有一种比乒乓结构更杂乱的缓存办理战略,那便是三缓存环形结构。如图10.22所示,这样的结构尽管比乒乓结构供给了更好的缓存功能,可是办理的杂乱度大大提高了,体系的推迟也增加了。

图10.22三缓存的环形缓存区示意图

无论是单缓存,双缓存仍是三缓存结构,只要能满意体系的实时收集要求便是有用的缓存战略。