彩灯作为一种景象,装置在建筑物的恰当当地一是作为装修添加节日气氛,二是有一种广告宣传的效果,也可用在舞台上增强晚会灯光效果。完结彩灯操控的计划许多,不同的操控计划,其规划办法和思路也不一样。本文介绍一种彩灯操控器的规划办法。该体系依据可编程逻辑器材CPLD(Complex Programmable Logic Device)芯片,运用VHDL硬件描绘言语规划体系中心部件,再配以恰当的外围电路构成。输出为32路数字信号,操控32路彩灯输出,上电后,彩灯体系无需外加输入信号,能主动循环演示十六莳花型,彩灯明暗改换节拍为0.25秒和0.5秒,快慢两种节拍主动替换运转。该体系较曾经的传统规划,选用硬件电路简略、花型容量大,体积小,功耗低,可靠性高,特别是能够在运用一段时间后,不修正硬件电路的基础上,仅经过更改软件就可完结修正花型的编程操控计划。

1、 体系组成

该彩灯操控器体系组成框图如图1所示。体系作业原理:彩灯操控器是以高、低电平操控灯的亮灭,按节拍改动送给各路的高、低电平,即l、0编码,就可操控彩灯按预订的规则亮灭,然后显现花型。彩灯操控器包含下列几部分。振动器:供给体系作业的主时钟。节拍发生器:发生体系要求的快、慢节拍脉冲PH、PL,并依据体系运转状况,供给相应节拍,使彩灯明暗改换以快、慢两种节拍主动替换运转。地址码发生器:为编码发生器供给适宜的地址码,以确保按节拍读出规则的编码,复现预订的花型,并依据体系运转状况,送节拍发生器反应信号,操控节拍按快慢两种主动替换运转。编码发生器:依据花型要求按节拍输出32位状况编码信号,以操控彩灯按规则亮灭。缓冲驱动器:为彩灯供给需求的作业电压和电流,阻隔负载对体系作业的影响。

2、体系各单元规划

2.1 振动器

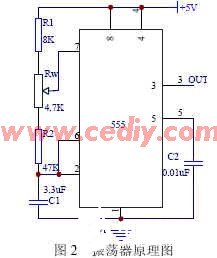

振动器供给体系作业的主时钟。因彩灯操控器对守时要求不高,故选用简略易行的555守时振动器。体系彩灯明暗改换节拍为0.25秒和0.5秒,咱们使振动器振动频率为f = 4Hz,电路原理图如图2所示。图中电阻R1=8K,Rw=4.7K, R2=47K,电容C1=3.3 uF,振动频率输出端OUT送“节拍发生器”的输入端。

2.2节拍发生器

其效果发生体系要求的快、慢节拍脉冲,快节拍PH=0.25秒、慢节拍PL= 0.5秒。快节拍频率直接由振动器的频率传入,慢节拍频率将振动器输出的频率进行二分频得到。节拍挑选信号Pc由地址码发生器发生,若第一轮花型循环输出为慢节拍,Pc为低电平,则第二轮花型循环,Pc为高电平,第三轮花型循环,Pc又为低电平,如此重复。节拍发生器输出节拍脉冲PP由PL和PH组成,![]() 。输出节拍频率PP送地址码发生器。

。输出节拍频率PP送地址码发生器。

该模块VHDL程序如下(省略声明部分):

ENTITY jpxz IS –节拍发生器

PORT ( clk: IN STD_LOGIC; –传入振动器频率

Pc : IN STD_LOGIC; –节拍挑选信号

PP : out STD_LOGIC);–输出节拍频率

end;

ARCHITECTURE jiep OF jpxz IS

signal PPL: STD_LOGIC;

signal PH: STD_LOGIC;–快节拍信号

signal PL: STD_LOGIC;–慢节拍信号

begin

fenp: process(clk) — 将clk时钟二分频,得到节拍为0.5秒的慢节拍

BEGIN

IF clk‘EVENT AND clk = ’1‘

THEN PPL 《= NOT PPL;

END IF;

END PROCESS;

PH 《= clk;– 快节拍的频率等于振动器输出的频率

PL 《= PPL; — 慢节拍

pp 《= (not Pc and PL) or (Pc and PH);

— PP为输出节拍信号,Pc为高电平输出快节拍,Pc为低电平输出慢节拍

end;

2.3 地址码发生器

其效果一是为编码发生器供给适宜的地址码,二是为节拍发生器供给节拍操控信号。

该部分首要电路,一部分为地址计数器,运用进程p01: process(ppclk)依据节拍发生器供给的节拍频率PP发生地址码,完结地址累加,完结预订花型的循环显现,一起运用jiep信号记载体系运转状况,该32路彩灯操控器演示花型共16种,花型循环一周共243拍,地址计数器将地址码累加到244,jiep值为‘1’,地址码为其它值时,jiep值为‘0’;另一部分内容为运用进程P02:process( jiep )将jiep信号进行二分频,使输出花型在第一轮循环时, 节拍挑选信号Pc为低电平,则第二轮花型循环时,Pc为高电平,第三轮花型循环,Pc又为低电平,如此重复。该模块VHDL程序如下(省略声明部分):

ENTITY cai_lizi IS –地址码发生器;

PORT ( ppclk: IN STD_LOGIC; –节拍脉冲信号,由节拍发生器传入

dzout : out integer range 0 to 245;– 地址码输出,16莳花型运转一次共243拍

Pc: out STD_LOGIC);–节拍挑选信号,送节拍发生器

end;

ARCHITECTURE lizi OF cai_lizi IS

signal count: integer range 0 to 245;

signal jiep: STD_LOGIC;

begin

p01: process(ppclk) –发生地址码

begin

if count=244 then count 《= 0; jiep 《= ’1‘; –16莳花型运转一次共243拍

elsif rising_edge(ppclk) then count 《= count + 1; jiep 《= ’0‘;

end if;

end process;

P02:process( jiep ) –将jiep信号进行二分频,发生节拍挑选信号Pc值

VARIABLE Count2 : STD_LOGIC;

BEGIN

IF jiep’EVENT AND jiep = ‘1’

THEN Count2 := NOT Count2;

END IF;

IF Count2 = ‘1’ THEN Pc 《= ‘1’;

ELSE PC 《= ‘0’;

END IF;

END PROCESS;

dzout 《= count;

end;

2.4 编码发生器

地址码发生器将输出的地址码送入编码发生器,编码发生器依据高、低电平操控灯的亮灭,即l、0编码,依据花型要求按节拍输出32位状况编码信号,以操控彩灯按规则亮灭。

该模块VHDL程序如下(省略声明部分):

ENTITY cai_bmq IS

PORT ( dzout: IN integer range 0 to 245;– 由地址码发生器传入地址码

qout : OUT STD_LOGIC_VECTOR(31 DOWNTO 0));– 输出32位状况编码

END;

ARCHITECTURE bianma OF cai_bmq IS

begin

process(dzout)

begin

case dzout is

when 0 =》 qout 《= “10000000000000000000000000000000”;

when 1 =》 qout 《= “11000000000000000000000000000000”;

when 2 =》 qout 《= “11100000000000000000000000000000”;

……

when 241 =》 qout 《= “10010010010010010010010010010010”;

when 242 =》 qout 《= “01001001001001001001001001001001”;

when 243 =》 qout 《= “00100100100100100100100100100100”;

when others =》 qout 《= “10010010010010010010010010010010”;

end case;

end process;

end;

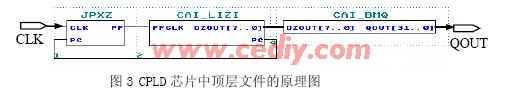

2.5 在CPLD芯片中顶层文件的原理图,如图3所示。

图中JPXZ模块为节拍发生器,输入端CLK接振动器的输出时钟,频率为4Hz,Pc为节拍挑选信号,PP为输出节拍。CAI_LIZI模块为地址码发生器,CAI_BMQ模块为编码发生器,输出端QOUT[31..0] 输出32位状况编码信号, 接缓冲驱动电路。

2.6 缓冲驱动电路

该模块为彩灯供给需求的作业电压和电流,阻隔负载对体系作业的影响。首要依据每路彩灯的功率挑选继电器或双向可控硅,再依据继电器或双向可控硅所需驱动电压和电流规划驱动电路。具体规划此处不再介绍。

3、体系仿真测验与什物测验

在依据MAX+PLUSⅡ软件渠道,对该体系程序各模块进行仿真测验,图4所示为彩灯操控器顶层文件仿真波形图。

图中CLK为振动器发生体系的主时钟,周期为0.25秒,qout[31..0]为彩灯操控器输出的32路数字操控信号(32位状况编码),图中所示当体系以慢节拍(0.5秒,2个周期一拍)输出最终一组编码后,立刻以快节拍(0.25秒,1个周期一拍)开端下一轮花型循环,到达规划要求。

将该体系程序下载到MAX7000S系列的EPM7128SLC84-15方针芯片上,并配以外围电路进行什物测验( 以LED灯替代彩灯),满意到规划要求。

4、结束语

本文作者立异点:以VHDL 硬件描绘言语进行规划,将彩灯操控器的中心部分集成在可编程逻辑器材CPLD芯片上,大大简化了外部电路,较曾经的传统规划,既削减了所用芯片的品种和数量,缩小了体积,降低了功耗,提高了体系的全体功能,对体系在运用中的故障率大为削减。特别是,对花型规划计划的修正、添加花型数量都很便利,能够在不修正硬件电路的基础上,仅经过更改软件就可完结,具有宽广的使用远景。

责任编辑:gt