0 导言

现在,正交频分复用(OFDM)技能成为多媒体传感器网络信息传输的干流研讨方向,并越来越遭到人们的重视。OFDM关于符号守时非常灵敏,守时差错会形成符号间搅扰(ICI),所以符号守时算法的研讨在OFDM技能中是至关重要的。

守时同步算法一般分为根据非辅佐数据的同步算法和根据辅佐数据的同步算法。现在使用最广泛的根据导频的守时和频偏估量算法是由Schmidl提出的。这种算法选用相同的两段练习序列进行守时,该办法选用递推公式进行核算,完结复杂度很低,在OFDM体系中被广泛选用,可是这种办法的守时断定函数存在一个差错渠道,会引起很大的守时差错。为了减小守时断定函数的差错渠道形成的影响,Minn对Schmidl的办法做出了必定的改善。Minn的守时断定函数是一个尖峰,在必定程度上消除了差错渠道的影响;Park提出了一种守时断定函数愈加尖利的波形。可是因为循环前缀的存在,这种办法的断定函数有很大的旁瓣,在循环前缀较长时,简直与主瓣的高度相同,在信噪比较低的情况下,很难得到正确的守时成果。选用练习序列与本地PN码相互关有显着的单峰值,但在频偏较大的情况下,守时断定函数会严峻变形,引起较大的守时差错。

本文针对一种长短序列相结合的符号守时算法,给出了准确守时的FPGA设汁计划,并对该办法进行了FPGA完结。在完结的过程中,选用状态机、流水线等规划办法,优化了体系的资源和运算速度,增强了本规划的使用价值。

本文首要介绍了OFDM体系的帧结构,然后介绍了精同步的FPGA完结结构,并对完结结构进行了剖析,最终对相关Matlab仿真成果进行了剖析,并给出精同步FPGA的完结资源损耗报表。

1 OFDM数据帧结构

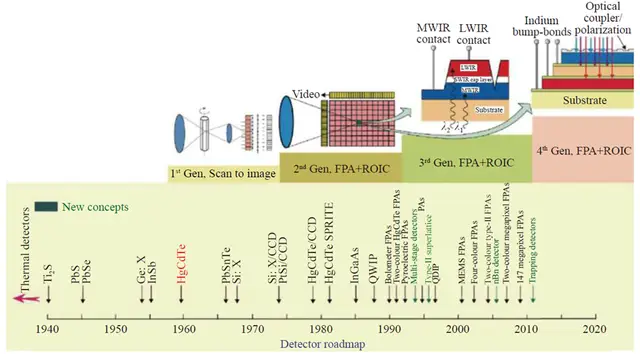

本文中OFDM体系参照现在广泛使用于无线局域网中的IEEE 802.11a规范,以突发形式传输数据,其数据帧前端的前导码用作同步,AGC,频偏估量。它的前导码结构如图1所示。前导码包含长练习序列和短练习序列两个部分。短练习序列分为10段,每段长度为32个抽样点;长练习序列分为2段,每段长度为128个抽样点,加上维护前缀,总长度为640个抽样点。前导码之后是数据部分。

2 精同步FPGA规划及剖析

2.1 精同步FPGA规划

精同步用于信号的准确守时。本文假定体系现已完结粗频偏估量,体系的频偏在精同步能够忍受的范围内。该规划选用本地序列地与长练习序列相关的办法,因为本地序列不受噪声的影响,相关运算后,断定函数存在显着的单峰值,可进行准确守时。体系后续数据帧还有循环维护前缀和信道估量的处理,精同步的现已能够到达体系功能的要求。

本文从资源耗费视点动身,对传统办法进行了改善,在不下降体系功能的前提下优化了体系资源耗费。

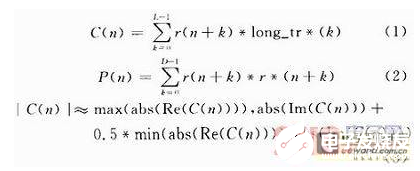

精同步首要由本地相关器、累加器和阈值断定器三个模块组成,规划选用流水线的办法,完结结构如图2所示。

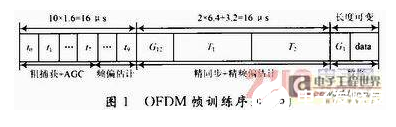

式中:r(n)标明输入数据;C(n)是与本地序列相关的相关值;P(n)标明信号的功率,用作信号能量的归一化。

本地相关器的完结是精同步的要害部分,本地相关器的完结中需求用到复数乘法器,本文选用的复数乘法算法如式(5)所示:

因为精同步是与本地序列相关,不存在递推公式,为了下降资源损耗,在选取本地序列时,仅截取实部和虚部的符号位,即每个本地序列的实部和虚部仅用-1,0,1标明,这样每个复数乘法能够转换成加法。

本文对断定函数的核算办法进行了改善,式(3)是对|C(n)|进行一阶泰勒打开,只取0次项与1次项作为|C(n)|的近似成果。

在峰值检测时,本文选用乘法替代除法进行门限断定,门限断定函数如式(6)所示:

|C(n)|》gate*P(n) (6)

到达门限断定条件时,精捕获成功,并通过计数的办法找到FFT窗的方位,完结守时同步。

2.2 FPGA规划计划资源耗费剖析

与传统办法比较,本文提出的计划在资源耗费上大大下降,首要体现在以下几个方面:

(1)在本地相关器的完结上。式(5)标明,每次复数乘法运算只需求进行3个乘法运算,节省了1个乘法资源。在进行相关运算时,传统办法在核算每个相关值时需进行384个乘法运算,在本文中,因为实部和虚部都只用符号位标明,乘法器能够用数据挑选器与加法器完结,大大节省了乘法器资源。

(2)在断定函数的核算上。传统办法每核算一个断定函数的值,需求进行4个乘法,2个加法核算。本文提出的近似办法中,每次断定函数的核算只需求2次乘法,2次加法,1次比较与1次移位操作,节省了乘法器资源。

(3)在硬件完结时。除法器对资源耗费非常大,本文用比较简略完结的乘法替代传统办法中的除法运算,节省了体系资源。

当然,本文对资源的优化是因为采取了必定的近似处理和截位处理,会带来必定的量化差错,在必定程度上会下降体系的功能,但仿真成果标明,这种功能的丢失在可接受范围内。

3 仿真及完结

3.1 仿真成果

使用本地序列截取符号和断定函数的近似对改善计划进行了仿真。该体系中,给定子载波数为N=128,码速率定为Rb=5 Mb/s,子载波距离为19.2 kHz,数字调制选用QPSK,信道模型选用AWGN模型,设定信噪比为5 dB。

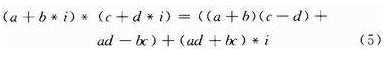

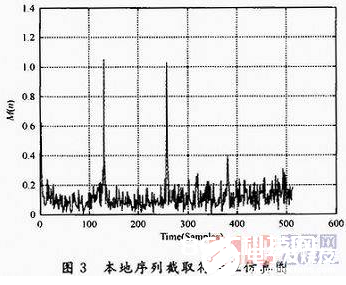

图3是选用本地序列截取2 b的断定函数M(n)的Matlah仿真图;图4是选用本地序列截取4 b的Matlab仿真图。检测峰值时,第一个峰值是因为循环前缀存在的影响,峰值检测时检测第二个峰值。

从图3,图4中能够看出,截位虽然会损耗算法的功能,可是断定函数存在显着峰值,挑选恰当的阈值时,依然能够准确守时同步,可见削减本地序列的精度对功能并未形成很大的影响。

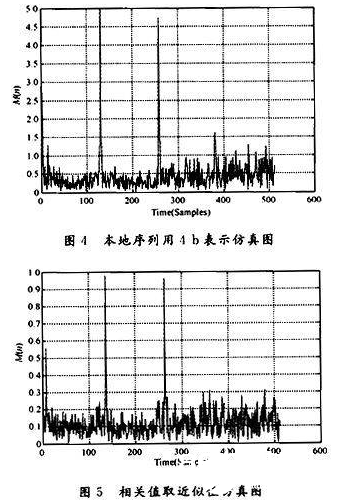

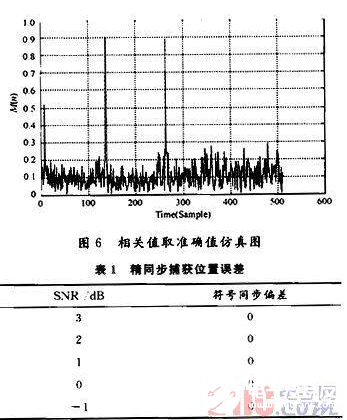

图5是选用断定函数取近似值的Matlab仿真图,图6是断定函数取确认值的Matlab仿真图。检测峰值时,第一个峰值是因为循环前缀存在的影响,峰值检测时检测第二个峰值。从图5,图6中能够看出,在断定函数近似处理虽然会损耗算法的功能,可是断定函数依然存在显着峰值,挑选恰当的阈值时,依然能够准确守时同步,可见削减对断定函数的近似对功能并未形成很大的影响。

表1是在AWGN环境下精同步方位的仿真成果,每个信噪比下通过5 000帧的仿真。符号同步差错标明每个信噪比下的精同步均匀过错长度,可见在体系的功能并未显着下降。

3.2 精同步模块实践完结

硬件规划是根据XLINX公司的SPRTAN6系列中的XC6SLX150-2FGG484芯片,选用Verilog HDL言语,仿真软件是ISE自带的ISIM,开发环境是ISE。

整个OFDM体系同步的ISIM仿真波形如图7所示。其间:clk_i标明时钟信号;reset_i标明同步复位信号;clk5M_en_i标明5 MHz时钟使能信号;nrst_j标明异步复位信号;acq_val_o标明粗捕获指示信号;dataI_o,dataQ_o标明通过粗捕获和粗频偏估量的输出信号;

sync_val_o标明精同步指示信号。

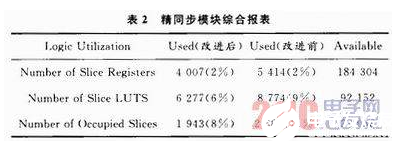

通过ISE归纳后,改善前和改善后精同步占用资源散布如表2所示。

由表2可见本文对体系资源优化的作用非常显着。

4 结语

本文剖析了一种OFDM体系精同步算法的原理,给出了FPGA硬件完结计划和成果剖析,该计划在选用经典算法的一起,对算法进行了改善,在不下降精同步功能的前提下大大下降了核算复杂度,而且规划结构简略,易于完结,具有较好的工程实用价值。