OSC是用无源晶振,EXT是用有源晶振或外部时钟2440的12M是Oscillator 是有源的呀!

2440的12M是Oscillator

| Crystal 无源晶体 Oscillator 有源晶体(里边有有源器材) |

| 无源晶振内只要一片按必定轴向切开的石英晶体薄片,供接入运放(或微处理器的XTAL端)以构成振动.有源晶振内带运放,作业在最佳状况,电源后,可直接输出必定频率的等幅正弦波,一般至少有4引脚,体积稍大. |

预备先不跑体系,把S3C2440和周边硬件了解一下再说。

关于任何一个单片机,要运用它首要就要弄理解他的时钟体系,MCU的时钟就像人的心脏,跳动的快慢,决议着体系的作业速度。S3C2440的datesheet上说,能够到达400M,可是也不是说,有必要在400M的频率下作业,主时钟晶振来自于外部晶振(XTIPLL)或者是外部时钟(EXTCLK)。时钟生成器包含了一个振动器(振动放大器),其衔接外部晶振,而且还有2个PLL,能够发生需求的高频。

经过引脚OM[3:2]来决议时钟源是Crystal仍是EXTCLK,不过我用的开发板将OM[3:2]固定接地了,都是用外部晶振。有一点值得留意,在对MPLLCON写入有效值之前,体系运用外部晶振或外部时钟源的时钟。即运用户不预备改动MPLLCON的值,也应当从头写一次。

简略说一下,S3C2440的时钟构成。

S3C2440具有2个PLL(Phase Locked Loop:用来发生高频的电路),一个是MPLL, 用于发生FCLK, HCLK, PCLK三种频率, 这三种频率别离有不同的用处:

FCLK是CPU供给的时钟信号,假如说到CPU的主频是400MHz,便是指的这个时钟信号。

HCLK是为AHB总线供给的时钟信号, Advanced High-performance Bus,首要用于高速外设,比方内存操控器,间断操控器,LCD操控器, DMA 以及USB host 。

PCLK是为APB总线供给的时钟信号,Advanced Peripherals Bus,首要用于低速外设,比方WATCHDOG,IIS, I2C, SDI/MMC, GPIO,RTC ,UART,PWM,ADC and SPI等等。

别的一个是UPLL,专门用于驱动USB host/Device。而且驱动USB host/Device的频率有必要为48MHz。

在体系复位之后,假如没有设定PLL,则选用外部晶振的频率作为FCLK,一起FCLK:HCLK:PCLK的比例联系为1:1:1。

下面说一些跟时钟有关的寄存器设置:经过改动CLKDIVN能够改动FCLK,HCLK,PCLK的分频比。

确定时刻计数寄存器LOCKTIME(0x4c000000):一般运用默许就能够。

锁相环操控寄存器[MPLLCON(0x4c000004)&UPLLCON(0x4c000008)]:

MPLL=(2*m*Fin)/(p*2^s) UPLL=(m*Fin)/(p*2^s)

其间m=(MDIV+8),p=(PDIV+2),s=SDIV

P,M规模:1<=P<=62,1<=M<=248

留意:MDIV[19:12],PDIV[9:4],SDIV[1:0],当设置MPLL和UPLL值的时分,需求先设置UPLL再设置MPLL。

例如:MPLLCON = (92<<12) | (1<<4) |(1);//FCLK=400M

这儿MDIV=92,PDIV=1,SDIV=1,那么m=100,p=3,s=1,且Fin=12M,所以FCLK=400M

再设置CLKDIVN=0x03;//FCLK:HCLK:PCLK=1:2:4

这儿CLKDIVN(0x4c000014)用于决议三者的分配比例

一般设置这两个就能够了。还有一个时钟操控寄存器CLKCON(0x4c00000c)向相应位写1使能相应时钟,不过一般默许为1.

关于时钟方面根本便是这么多了。

S3C2440 clock 作业原理

overview

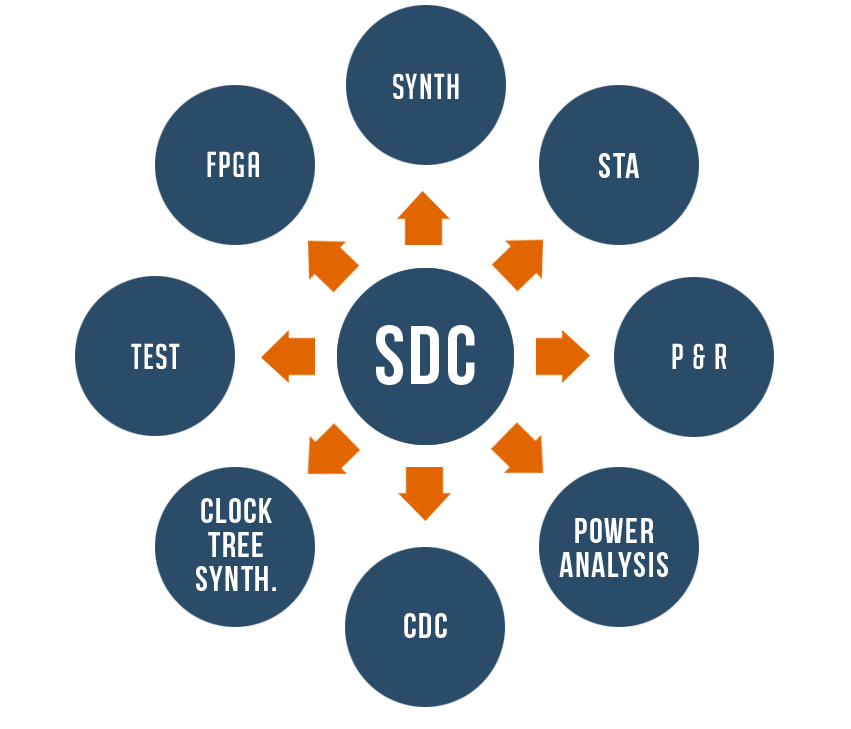

时钟和电源办理这一块内容包含三个部分:时钟操控, USB操控, 电源操控

在s3c2440a的CPU上,时钟操控逻辑能够发生需求的时钟信号,包含给CPU用的FCLK, 给AHB总线外设用的HCLK以及给APB总线外设用的PCLK.S3C2440A含有两个锁相环:一个是FCLK, HCLK和PCLK, 还有别的一个专门用于USB单元(48Hz).时钟操控逻辑能够在没有PLL的时分使时钟变慢,而且能够用软件的办法使时钟与周边设备衔接与断开, 这个功用能够节约功耗.

弥补:

AMBA总线

先进的微操控器总线体系结构AMBA标准界说了三种总线:

(1)AHB(Advanced High-performance Bus):用于衔接高功用体系模块。它支撑突发数据传输方法及单个数据传输方法,一切时序参阅同一个时钟沿;

(2)ASB(Advanced System Bus):用于衔接高功用体系模块,它支撑突发数据传输形式;

(3)APB(Advance Peripheral Bus):是一个简略接口支撑低功用的外围接口。

关于电源操控逻辑,S3C2440A有不同的电源办理的主题,来对某一项使命来优化电源功耗.S3C2440A中的电源办理单元能够有四种形式: 一般形式, SLOW 形式, IDLE形式, SLEEP形式.

功用描绘

时钟架构

时钟发生器包含一个衔接在外部crystal上的晶振,而且有两用于发生S3C2440A所需求的高频信号的锁相环.

时钟源的挑选

下表显现了芯片形式操控引脚(OM3和OM2)的挑选与S3C2440A时钟源的联系.

留意:

1) 虽然重启后,MPLL会发动,可是直到软件正确设置了MPLLCON寄存器后,MPLL的输出才作为体系的时钟.在正确的设置被设置前,来自外部的crystal或extclk源直接作为体系时钟.即运用户并不想改动MPLLCON寄存器的默许值,用户应该在MPLLCON的寄存器中设置相同的值.

2) OM[3:2]用于决议测验形式,当OM[1:0]是11的时分.

锁相环

在时钟发生器中的MPLL,作为一个电路,作用是在频率与相伴上同步输出信号与一个参阅输入信号.

时钟操控逻辑

时钟操控逻辑决议运用的信号源,PLL时钟或外部时钟. 当PLL装备成一个新的频率时,时钟操控逻辑间断FCLK的运用,直到运用PLL锁时刻的PLL的输出安稳后. 这种时钟操控逻辑在通电重启或从节电形式中醒来都起作用.

通电重启(XTIpll)

在一般形式中改换PLL的设置

USB时钟操控

FCLK, HCLK, PCLK

FCLK 用于ARM920T

HCLK 用于AHB总线,AHB总线被ARM920T用于,内存操控器,间断操控器,LCD操控器,DMA和USB host block.

PCLK 用于APB总线,APB总线是用于周边设备的,如是WDT,IIS, I2C, PWM 计数器, MMC接口, ADC, UART, GPIO, RTC 和SPI

留意:

1) CLKDIVN有必要当心设置,不要超越HCLK和PCLK的答应规模.

2) 假如HDIVN不是0,CPU总线形式有必要从快速总线形式转化到异步总线形式,经过运用下面的指令来到达.(S3C2440不支撑同步总线形式)

MMU_SetAsyncBusMode

mrc p15, 0, r0, c1, c0, 0

orr r0, r0, #R1_nF:OR:R1_iA

mcr p15, 0, r0, c1, c0, 0

假如HDIVN不是0, 而且CPU总线形式是快速总线形式,那么CPU将会在HCLK下作业.这种特功用够用来在不影响HCLK和PCLK的情况下改动CPU频率成本来的一半或更多.

电源办理

在S3C2440A中,电源办理模块经过软件来操控体系时钟以到达削减电源功耗的功用.这些主题跟PLL,时钟操控逻辑(FCLK,HCLK,PCLK)和唤醒信号有关.

S3C2440A有四种电源形式.下面的部分描绘各种形式.各种形式之间的转化并不是随意的.

FCLK的值怎么得到?

FCLK= Fout = 2 * m * Fin / (p*2^s), Fvco = 2 * m * Fin / p where : m=MDIV+8, p=PDIV+2, s=SDIV

MPLLVal [M:7fh,P:2h,S:1h] bootloader打印出来的信息.

code

mov r1, #0x4c000000

ldr r2, =0x7f021

str r2, [r1, #0x04]

与BOOTLOADER里打印出来的相同.

^ 代表幂

So, FCLK =2* (127+8)*12M/4*2=405M

关于HCLK, PCLK的值,取决于CLKDIVN的值.

代码如下:

mov r1, #0x4c000000

ldr r2, 0x5

str r2, [r1, #0x14]

所以CLKDIVN=5, HDIVN=10, PDIVN=1, 再看CAMDIVN

10: HCLK = FCLK/4 when CAMDIVN[9]=0

HCLK = FCLK/8 when CAMDIVN[9]=1

PCLK = HCLK /2

CAMDIVN代码中没有进行设置,就用初始值.0

故

HCLK = FCLK/4

PCLK = FCLK/8

至此, clock部分设置完毕.

MCLK:405MHz

HCLK:135MHz

PCLK:67.5MHz

在这儿定时器时钟频率为PCLK/8=67.5/8=8.4375MHz

定时器0示例代码:

转载请注明出处,谢谢!

2 {

3 rTCFG1 &= ~(0x0F<<4);

4 rTCFG1 |= (2<<4);

5 rTCNTB1 =(S3C2440PCLK)/8/1000000;

6 rTCON &= ~(0x0F<<8);

7 rTCON |= (1<<11)|(1<<9)|(1<<8);

8 rTCON &= ~(1<<9);

9

10

11 while(t–)

12 {

13

14 while(rTCNTO1!=(rTCNTB1-1));

15

16 }

17

18 rTCON &= ~(1<<8);

19

20 }

21

22

23 void T1DelayNms(UINT16 t)

24 {

25 rTCFG1 &= ~(0x0F<<4);

26 rTCFG1 |= (2<<4);

27 rTCNTB1 =(S3C2440PCLK)/8/1000;

28 rTCON &= ~(0x0F<<8);

29 rTCON |= (1<<11)|(1<<9)|(1<<8);

30 rTCON &= ~(1<<9);

31

32

33 while(t–)

34 {

35 while(rTCNTO1!=(rTCNTB1-1));

36 }

37

38 rTCON &= ~(1<<8);

39

40 }

特别是要留意rTCNTOn与rTCNTBn的联系。

2 {

3 rTCFG1 &= ~0x0F;

4 rTCFG1 |= 2;

5 rTCNTB0 =(S3C2440PCLK)/8/1000000; //时钟频率为PCLK/8

6 //除以1000000表明进行微秒级延时

7 rTCON &= ~0x0F;

8 rTCON |= (1<<3)|(1<<1)|(1<<0);

9 rTCON &= ~(1<<1);

10

11

12 while(t–)

13 {

14 while(rTCNTO0!=(rTCNTB0-1));

15 }

16

17 rTCON &= ~(1<<0); //中止定时器0

18

19 }

20

21 void T0DelayNms(UINT16 t)

22 {

23 rTCFG1 &= ~0x0F;

24 rTCFG1 |= 2;

25 rTCNTB0 =(S3C2440PCLK)/8/1000; //时钟频率为PCLK/8

26 //除以1000表明进行毫级延时

27 rTCON &= ~0x0F;

28 rTCON |= (1<<3)|(1<<1)|(1<<0);

29 rTCON &= ~(1<<1);

30

31 while(t–)

32 {

33 while(rTCNTO0!=(rTCNTB0-1));

34 }

35

36 rTCON &= ~(1<<0); //中止定时器0

37 }