跟着数字年代的到来,越来越多的范畴选用集成电路来规划电路,FPGA/CPLD等EDA规划更为广阔硬件工程师所承受。其模块化规划为规划人员带来了许多便利,节省了体系的开发时刻,使规划人员只需求调用这些模块或许IP核,然后组合起来就能够完成一个简略的功用。全数字锁相环(DPLL)便是其间一个典型的比如。可是DPLL在运用时存在许多缺点,例如锁相时刻长、捕捉带窄等。为了防止这些缺点,本文规划了一种全新的相位盯梢倍频体系,有用地改进了DPLL的这些目标,并在项目中得到了杰出的运用。

1 全数字锁相环的概念

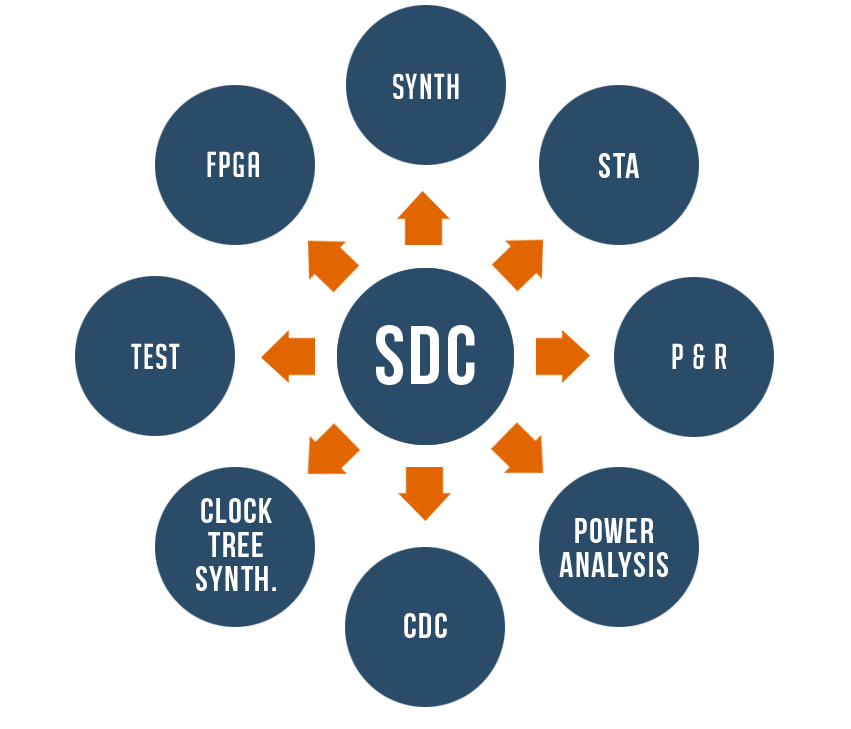

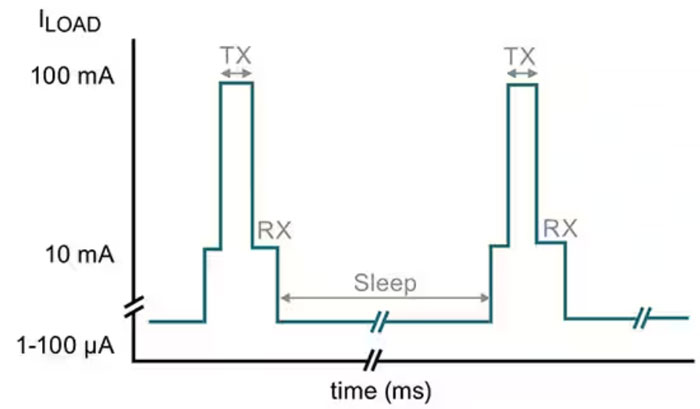

所谓全数字锁相环路,便是环路部件悉数数字化,选用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成锁相环路。典型全数字锁相环的结构如图1所示。它选用的鉴相器是导前-滞后型数字鉴相器。鉴相器在每一个周期内得到输入时钟的相位比本地预算时钟相位超前或滞后的信息,这样鉴相器的相位差错输出只需超前或滞后两种状况。将差错相位的超前或滞后信息送到序列滤波器后,发生对DCO的“加”或“减”脉冲操控指令去改动DCO的时钟周期,使本地预算时钟的相位与输入时钟相位挨近。

环路滤波器选用了K计数器。其功用便是对相位差错序列计数即滤波,并输出相应的进位脉冲或借位脉冲来调整I/D数控振荡器输出信号的相位,然后完成相位操控和确认。可是相位确认时刻与相位颤动之间是一对对立体,K值获得大,对遏止噪声有利,因为K值大,计数器对少数的噪声搅扰不可能计满,所以不会有进位或借位脉冲输出。但这样捕捉带会变小,并且加大了环路进入确认状况的时刻。反之,K值获得小,能够加快环路的入锁,但K计数器会频频地发生进位或借位脉冲,然后导致相位颤动,增大了同步差错,相应地对噪声的按捺才能也随之下降。因而关于一般的DPLL,挑选恰当的K值很重要。

关于倍频电路,现在大部分都是依据锁相环技术开发的,因而不可防止地也会将锁相环中规划存在的对立带入倍频规划中。即便体系倍频的规模很宽,但因为PLL的本身缺点所带来的频谱纯度差、颤动显着、噪声大等缺点是不可防止的。

2 新计划的提出

近几年来,越来越多的科研机构致力于开发新式的锁相倍频体系,不管在数字仍是模仿范畴,都有了簇新的打破。在模仿方面,Fordahl开发了一种如图2所示的新倍频模仿办法。该办法在高频和低频段作业杰出,一起有用地改进了在锁相环规划中所带来的缺点。在数字方面,一种全新构架的无类比全数字锁相倍频电路现已由某科研机构研制开发成功,并现已投入运用,其结构如图3所示。该规划彻底依据FPGA/CPLD规划开发而成,锁相时刻短(只需求一个体系时钟周期tpd的延时),一起具有无类比电路、无颤动、无内部振荡器、功耗低一级长处。

本文结合上述两种办法,依据FPGA流水线的操作思维,规划了一种全新的相位确认倍频体系。在具有上述两个倍频电路长处的一起,增强了倍频的精度,扩展了倍频规模,在体系资源答应的规模内,合理地运用芯片面积与速度的联系,以较少的逻辑单元,规划出高速倍频体系。

3 原理及算法

这种全新相位确认倍频体系由四大模块组成:同步预处理模块、计数器模块、算法模块、挑选输出模块。其结构如图4所示。

3.1 原理

首要,对输入参阅时钟(CLK_IN)进行同步处理,对输入信号进行仿制,使得输入信号与大局时钟(SYSCLK)到达同步(即便仿制后的信号与输入参阅时钟存在差错,差错也小于一个SYSCLK周期),然后以SYSCLK为基准对CLK_IN进行计数。假如信号CLK_IN颤动很小或许周期稳定,则以n(n》1)个周期为单位进行计数;假如颤动很大(一般与外部环境及物理要素有关),则以一个周期为单位进行计数,并将计数值作为输入传送给算法模块。算法模块通过一系列算法流程后,得到一个使能信号(/EN)。最终运用树立时刻(Tsu)和坚持时刻(Th)的特性,以使能信号/EN低有用对SYSCLK挑选输出,得到所需求的倍频信号。

从PLL倍频的原理动身,输入参阅时钟倍频后的频率不可能大于体系时钟频率,因而对输入时钟的倍频问题归根到底便是对体系时钟的分频问题。体系时钟分频后,一方面作为信号输出,一方面作为反应信号。频率除以N(倍值)后,得到本地预算信号,通过DPLL环路,使之与参阅时钟同相,这样就得到了与输入参阅时钟的同相N倍频输出信号。从这儿能够看出,依据DPLL的倍频电路是体系相位确认与时钟倍频一起进行的。因而倍频进程中,必定遭到DPLL本身要素的限制。而本文规划的倍频体系,体系同步进程和倍频进程是两个独立的进程,相互之间不存在依靠联系,因而能够将两个进程别离做优化处理。

(1)锁相问题。能够把它转化为“同步”问题来考虑。同步进程中最重要的概念便是“参照系”,关于锁相环而言,本地预算信号是以输入参阅时钟为参照进行运算得来的;而若以体系时钟作为参照,本地仿制信号必定与体系时钟同步,且与输入参阅时钟同相。这样做的长处是相位确认快,提高了芯片体系速度(频率)。

(2)倍频问题。已然本地仿制时钟是与体系时钟同步的,而全部与体系时钟同步的信号必定与仿制信号同步,那么对本地仿制信号的倍频问题,就能够简化为对体系时钟的分频问题。例如,假定输入参阅信号的频率为64kHz,体系时钟的频率为64MHz,现要求规划一个电路,其输出信号与输入参阅信号同相,且频率为9.6MHz时钟。通过运算可得到输出信号是输入参阅信号的1 500倍,是体系时钟频率的20/3分频。因而只需规划出20/3分频电路,就可得到输出信号是输入参阅时钟1 500倍的倍频信号。其算法思维如图5所示。

3.2 算法

以SYSCLK作为累加器的体系时钟,累加器的位宽依据分频的精度而确认,累加操作在体系时钟的上升沿有用,累加器的初始值为0。因为是20/3分频,所以累加器在时钟的上升沿时添加0.15,一起判别0.15和1的巨细,因为0.15《1,所以/EN=1。在时钟的第二个上升沿到来时,在累加0.15等于0.3后,一起判别0.3和1的巨细,因为0.3《1,所以/EN=1。依此类推,在时钟的第七个上升沿到来时累加器的值应该是1.05,因为1.05》1,所以/EN=0。再将1.05减去1的差0.05作为累加器的初始值进行下次运算,顺次进行下去就能够得到/EN信号。

在FPGA的规划中,一般常常用到的是时钟的上升沿,依据FPGA的树立时刻Tsu和坚持时刻Th,虽然在树立时刻不能采到SYSCLK的上升沿,但在坚持时刻却能够采到第八个上升沿。这样就能够得到频率为9.6MHz的输出信号。

4 功能剖析

4.1 相位确认时刻

因为本规划以体系时钟为参照,所以本地仿制信号与输入参阅信号的相位差错最大为一个SYSCLK周期,本规划运用的是Altera公司的Cyclone系列EP1C3T144-8芯片,体系时钟频率最高能到达105.65MHz,因而最大差错为9.465ns。假如再通过优化,能够到达在7ns以内。

4.2 倍频规模及其精度

本规划选用恣意数分频算法,倍频后输出信号的频率规模能够从0Hz到体系时钟的最高频率。因而,关于精度,能够做到小数点后恣意值,可是故意地寻求精度,是以糟蹋芯片面积为条件的,所示挑选精度值还要依据芯片的逻辑单元多少来决议。

5 仿真成果

仿真的部分波形图如图6所示,扩大作用图如图7所示。

本文提出的全新锁相倍频体系计划现已在项目中得到运用,并在实践中得到查验,功能彻底到达预期要求,作用杰出。