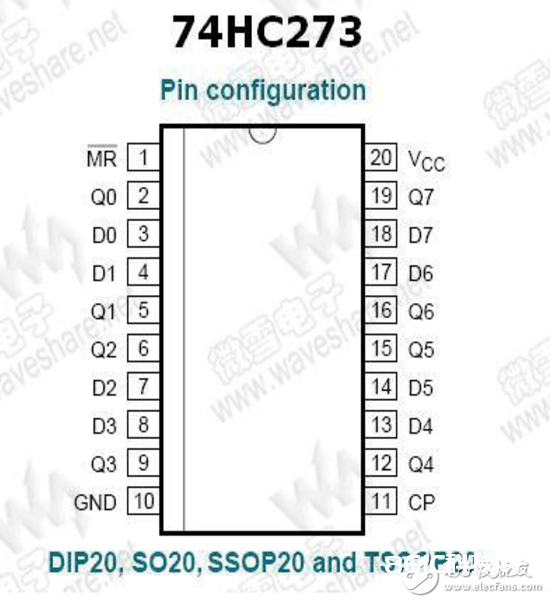

74HC273是一款高速CMOS器材,74HC273引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC273具有八路边缘触发,D 型触发器,带独立的D输入和Q输出。74HC273的公共时钟(CP)和主复位(MR)端可一起读取和复位(清零)一切触发器。每个D输入的状况将在时钟脉冲上升沿之前的一段安排妥当时间内被传输到触发器对应的输出(Qn)上。

一旦MR输入电平为低,则一切输出将被强制置为低,而不依赖于时钟或许数据输入。

74HC273适用于要求原码输出或许一切存储元件共用时钟和主复位的使用。

74HC273 封装与引脚

SO20, SSOP20, DIP20, TSSOP20

74HC273 特性

用于MOS微处理器或存储器的抱负缓冲器

共用时钟和主复位

八路上升沿触发D 型触发器

兼容JEDEC规范no.7A

ESD维护

HBM EIA/JESD22-A114-C超越2000 V

MM EIA/JESD22-A115-A超越200 V

可选多种封装类型

温度规模

-40~+85 ℃

-40~+125 ℃

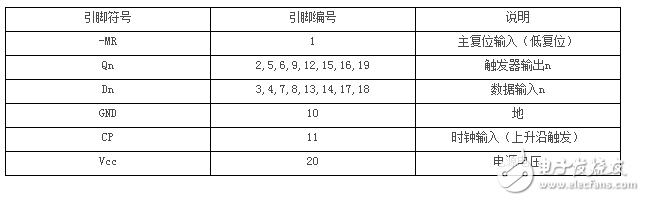

各个引脚的效果如下(参照图1阐明):

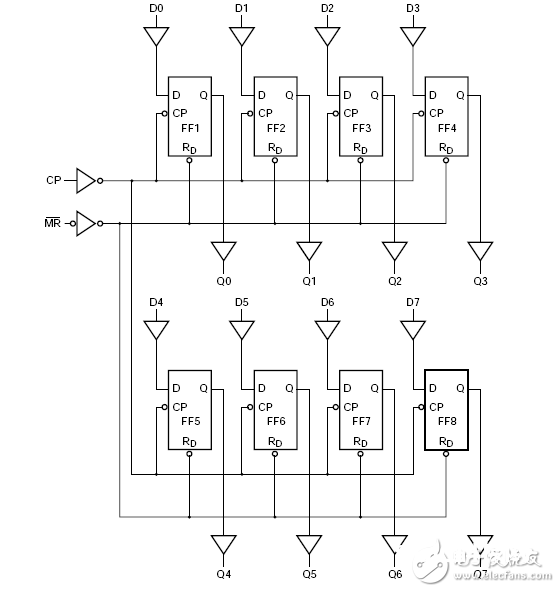

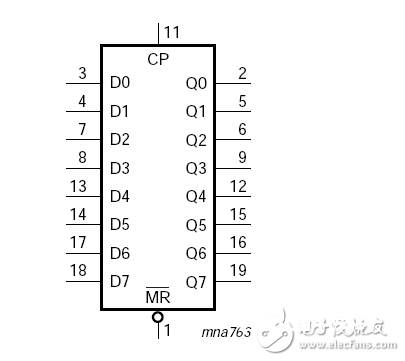

为了能够明晰地表达它的首要引脚的效果,下面是它的逻辑符号图(图2):

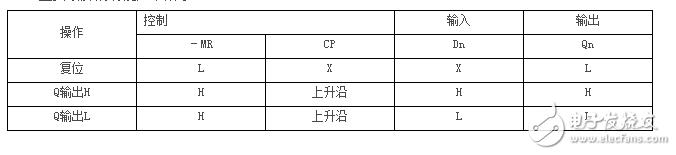

首要引脚的功用如下所示:

-MR为高的使能所用的触发器,Dn脚的输入会在CP的上升沿触发后传送给对应的Qn输出脚

为了更好的了解,咱们来看一下它的内部原理图: