0 导言

数控体系的中心技能是运动操控技能,跟着机电一体化的深入开展,运动操控技能已经成为推进机电一体化进程的重要环节,是推进新的产业革命的关键技能码。

现代高速数控技能对运动操控器的速度和精度要求日益进步,与运用软件完结的操控器相比较,依据FPGA规划的插补操控器具有操控便利、插补速度快、精度高、通用性好、可移植性的特色,并具有可运用硬件描绘言语完结软硬结合等多种长处。为了进步伺服电机的准确度,本文规划了一个依据数字积分法并选用多轴联动技能的插补操控器,该操控器可完结三轴的直线插补和两轴的圆弧插补。

1 插补操控器的总体规划

该操控器的中心部分是DDA插补模块,整个插补模块可分红直线插补模块和圆弧插补模块两部分。每个插补模块内都由数据缓存器、插补积分器和方位计数器3个部分组成。下面别离介绍各个模块的规划及仿真。

插补操控器具有三轴直线插补及两轴圆弧插补的才干,2种插补均选用数字积分法完结。数字积分法(DDA)具有逻辑才干强、可完结多轴联动操控,且输出脉冲均匀的特色。如图1所示,插补操控器接纳到外部处理器的操控信号和数据,经过译码及装备存放器模块的译码和装备后,依据需求挑选进行直线插补或圆弧插补,输出指脉冲和方向信号。脉冲用于经过伺服电机驱动操控伺服电机的滚动,方向信号则操控伺服电机的滚动方向。

2 依据FPGA的模块规划

该插补操控器选用Altera公司的CycloneⅢ-EP3C16Q240C8,运用Verilog HDL完结程序规划,在QuartusⅡ渠道进行编译、归纳及下载,运用Modeisim进行程序的仿真和调试,终究完结整个操控器的规划(如图1所示)。

2.1 译码及装备存放器模块

译码及装备存放器模块首要担任译码和完结各存放器间数据的分配,并且挑选需求进行的插补方法。以下为各个输入端口的界说和作业方法:cs为片选信号。

低电平有用,外部处理器选中插补操控器,使其进入待命状况;rest为复位信号。低电平有用,整个操控器处于复位状况,操控器内部各个模块做初始化操作;wr为写信号,低电平有用,向插补操控器写入需求完结插补的初始点坐标和结尾坐标的数据;start为插补开端信号,高电平有用,插补操控器开端进行插补;A3~A0为4位地址信号,经过地址指针的方法,将处理器数据分配给插补模块各轴的数据缓存器。其间,高位A3具有挑选插补方法的功用;A3位为“0”时,插补操控器做三轴直线插补;A3位为“1”时,做两轴圆弧插补;data为16位数据总线端口。

2.2 DDA插补模块

DDA插补模块有直线插补和圆弧插补两部分,两种插补方法在一次插补进程中,只能有一种处于作业状况。直线插补可以完结3个轴的脉冲输出,完结二维或三维的直线轨道,而圆弧插补是完结两轴的脉冲输出,完结二维的圆弧轨道。

2.2.1 直线插补模块

中选中直线插补模块时,该模块进入作业状况。直线插补模块由数据缓存器、插补积分器和方位计数器3个部分组成。下面别离介绍各部分的规划及其功用。

(1)数据缓存器

数据缓存器共由6个16位存放器构成,它们别离存储x,y,z三个轴的初始点坐标值及结尾坐标值。数据缓存模块将直线插补的数据进行主动加载,以便于直线插补积分器调用模块内的数据。进行缓存的意图是为了坚持数据的流畅性,保证直线插补不由于数据的改动而呈现中止的状况。这样大大地进步直线插补的功率,一起削减由于时序问题所带来的差错。当积分器加载缓存器中的数据完毕今后,积分器接纳到start信号,积分器开端进行数字积分直线插补。当数据缓存器接纳到rest信号时,缓存器中所有数据悉数做复位操作。

(2)方位计数器

方位计数器有3个存放器,别离对应于三个轴。其初始值为需求插补的脉冲数目。当积分器每输出一个脉冲,计数器便做减“1”。当方位计数器为零时,则表明抵达结尾坐标方位,插补完毕。

(3)插补积分器

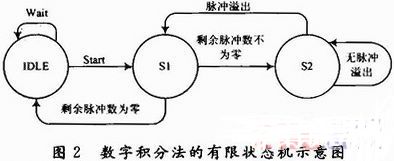

插补积分器是直线插补的中心模块,由余数存放器和被积函数存放器构成。被积函数存放器中存放由数据缓存器供给的结尾坐标值,每逢脉冲源宣布1个插补迭代脉冲时,被积函数存放器与余数存放器的值累加1次,并将累加成果存放余数存放器中,当累加成果超出余数存放器容量(216)时,溢出1个脉冲。经过N=216次累加后,每个坐标轴的溢出脉冲总数就等于该坐标的被积函数值。在余数存放器的容量必定的状况下,其输出脉冲频率与结尾坐标值的巨细成正比。操控器选用三轴联动,则一起有3个积分器一起进行插补运算。在该插补操控器的规划中,选用有限状况机的原理完结直线插补的完结,如图2所示,共有3个状况存在:

(1)状况IDLE:闲暇状况,等候插补信号;

(2)状况S1:剩下插补脉冲数存放;

(3)状况S2:积分累加状况。

其作业进程为:当没有发动信号时,体系持续坚持在闲暇状况IDLE;当有发动信号start时,体系则从数据缓存器中读入初始数据,将插补脉冲数存放在状况S1中,若插补脉冲数不为零则转至积分累加状况S2中,在此状况中将被积函数存放器的值与余数存放器的值进行累加,成果送余数存放器,若有脉冲溢出,则转入状况S1,此刻输出插补脉冲,且状况S1中剩下脉冲数减“1”;若无脉冲溢出,则状况S2持续进行积分累加。终究,状况S1中的剩下脉冲为零时,回来闲暇状况,插补完毕。

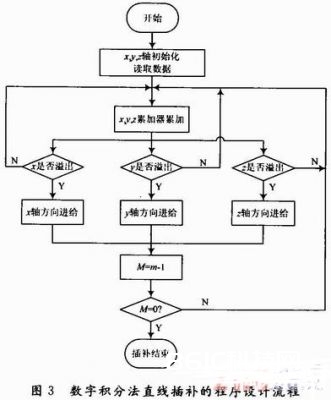

数字积分法直线插补运用硬件描绘言语VerilogHDL进行程序编写的流程图如图3所示。

在本插补操控器中,选用了“半加载”的方法完结输出脉冲的均匀分配。半加载就是在插补运算前,在余数存放器中预置该存放器容量一般的值,这样可以使在插补数据远小于插补器位宽的状况下,使积分器更快地输出溢出脉冲,从而使脉冲更为均匀。

积分器做插补时,不管被积函数的巨细,都必须经过216次累加才干抵达结尾,因而各轴输出脉冲速度受被积函数巨细影响,被积函数越大,脉冲输出速度越高。为了让积分器溢出速度到达最快且均匀,在插补时,把各轴被积函数存放器中的数据一起进行左移规格化处理,使其间一轴的最高位为“1”。左移1位,相当于各轴乘2,左移2位各轴则一起乘22,以此类推。这样,在不改动各轴数据比值的状况下,进步了各轴的脉冲溢出速度。规格化后,每累加运算2次必有1次脉冲输出,很好地处理了小进给量输出不均匀的问题,插补的功率和质量大为进步。

2.2.2 圆弧插补模块

圆弧插补模块与直线插补相同,也由数据缓存器、插补积分器和方位计数器构成。两模块的数据缓存器和方位计数器功用相同,这儿不再论述。

圆弧插补积分器与直线插补积分器相同选用状况机的规划完结,但它们之间有两点差异:一是x,y轴相应坐标值存入被积函数存放器的对应联系与直线不同,恰好是方位互调的,即y轴的被积函数存放器中存入x值,x轴的被积函数存放器中存入y值;二是存入的坐标值不同,直线插补时存放的结尾坐标是常数,而圆弧插补时存放的是动点坐标,在插补进程中依据其方位的改变应更改被积函数存放器中所存的内容。当y轴每溢出1个脉冲,x轴的被积函数存放器加“1”;反之,当x轴每溢出1个脉冲,y轴的被积函数存放器减“1”,减“1”的原因是x向负方向进给,动坐标不断削减。

3 仿真试验

为验证规划的正确性,仿真试验完结了二维的直线插补和圆弧插补。

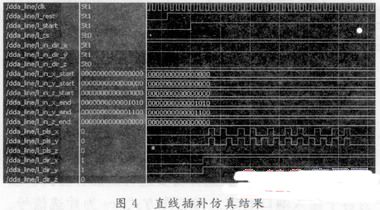

(1)直线插补仿真。当给定一向线段的起点坐标为(0,0,0),结尾坐标为(10,12,0),则该直线在xOy平面内完结直线插补的仿真信号波形如图4所示。

现别离给出了在xOy平面内,该直线与别的两条直线构成三角形的多视点的直线插补轨道(如图5所示),三角形的极点坐标别离为(0,0),(10,12)和(15,6)。由插补轨道图可见,各个视点的直线插补轨道(各点连线)与实践直线(实线)的拟合度杰出,直线交界处彻底符合,完结了预期的关闭图形。

(2)圆弧插补模块仿真如图6所示为坐落榜首象限,在xOy平面内,起点坐标为(15,0),结尾坐标为(0,15)的逆时针圆弧的插补仿真成果。

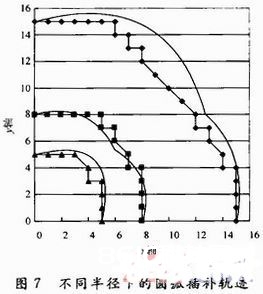

图7展现了在xOy平面内,起点坐标别离为(5,0),(8,0)和(15,0)的逆时针圆弧的插补轨道(各点连线)与实践圆弧(实线)的比较。由图可见,跟着轨道点的添加,圆弧轨道与实践圆弧的拟合度越高。

4 结语

依据数字积分法和多轴联动技能规划的伺服电机插补操控器,其在直线插补中不只完结了直线的准确步进,并且经过不同方位的运动很好的得到了原点的回复。在圆弧运动中,跟着精密的插补,圆弧的拟合精度进步。跟着运动操控体系朝着通用化、智能化、微型化的方向开展的趋势,插补操控器是运动操控体系飞速开展的重要柱石。本文研讨的插补操控器不只完结三轴直线插补及两轴的圆弧插补,并且选用多轴联动,插补精度得到进步,脉冲输出均匀。这种规划优化了结构,易于操作,便于与外部处理器扩展和链接,以构成完好的运动操控体系。