(来历:微计算机信息 ,作者:张学志, 魏友国,涂望明,田 璋,侯彦宾)

导言

跟着深亚微米工艺的开展, FPGA的容量和密度不断添加,以其强壮的并行乘加运算(MAC)才能和灵敏的动态可重构性,被广泛运用于通讯、图画等许多范畴。但是在杂乱算法的完结上,FPGA不如嵌入式处理器便利,所以在规划具有杂乱算法和操控逻辑的体系时,往往需求和嵌入式处理器结合运用,这便是 SOPC(System on a Programmable chip,可编程片上体系)技能。 SoPC是 SoC和 FPGA结合的产品,由单个可编程重构的芯片完结整个体系的首要功用。SoPC规划灵敏多变,能够用原理图,硬件描绘言语乃至是 C/C++高档言语进行规划;一起还具有可重构、可削减、可扩大等特色,晋级便利。 SoPC兼备 SoC和 FPGA二者的长处,具有如下特色:

●丰厚的 IP核资源,包含通用 IP核和专用的 IP核

●在体系可编程,规划、编译、下载与调试简略便利

●内置嵌入式软核处理器,存储器,外设接口操控器

●很多可编程重构的逻辑资源

●功用强壮的时钟办理电路

●支撑多种 I/O接口规范

此外,因为减小了处理器和存储器之间的传输线距离,SoPC不管在速度,仍是信号完好性,电磁兼容等方面,比板级体系都有显着的优越性。

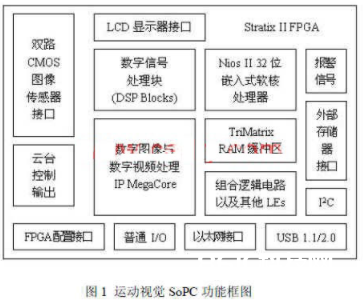

1 、功用框图

在数字视频视觉收集与处理板级体系开发的基础上,本文选用 SoPC完结运动视觉处理与操控体系的规划方案。硬件选用 Altera公司 StratixII系列 FPGA,软件开发东西包含 QuartusII,NiosII5.1 IDE,DSP Builder,MegaCore IP Library5.1和 Matlab7.0等。整个 SoPC体系作业原理为:摄像头收集的视频图画数据由图画传感器接口进来;数字信号处理块和数字图画与数字视频处理 IP核完结视频图画的处理,如运动检测、切割、特征提取、紧缩等; Nios II嵌入式处理器首要完结整个体系的操控功用;I2C总线用于拜访 CMOS图画传感器的内部寄存器;PC机能够经过 USB接口拜访 SoPC,假如间隔较远的话,能够经过以太网口进行数据的传输;视频图画及其处理后的成果既能够经过外部存储器接口寄存在 CF卡, FLASH等存储介质中,也能够经过 LCD显现器接口在液晶显现屏上直接显现。该运动视觉 SoPC的功用框图如图 1所示:

该模块首要担任视频图画的收集,摄像头参数的设置和云台步进电机的操控。其间,经过 I2C总线能够设定摄像头内部操控寄存器。在 FPGA中,完结 I2C总线操控器的途径有两种:一种是在 Nios II顶用软件模仿完结;另一种是选用第三方,比方 Sciworx,CAST,Digital Core Design等公司供给的 IP核。这些 IP核具有作业参数,能够依据需求进行设定。以 CAST公司供给的 I2C总线操控器为例,传输速率最高为 100Kbps,能够作业在 4种形式下,别离是主发送器形式、主接收器形式、从发送器形式和从接收器形式。双路 CMOS图画传感器接口操控视频图画收集的时序,帧同步和行同步;云台操控信号是依据视频图画处理后的成果,操控云台的两个步进电机的滚动。这两个模块需求自己开发,构成具有自主知识产权的 IP核。

2、 视频图画处理模块

该模块包含 NiosII 32位嵌入式处理器,数字信号处理块,数字图画与数字视频处理 IP

MegaCore,以及其他一些逻辑电路,这是运动视觉处理与操控 SoPC规划的要点和中心,别离分以下几个部分介绍。

(1) Nios II嵌入式处理器

Nios II嵌入式处理器是一款通用的 RISC结构的 CPU,它定坐落广泛的嵌入式运用。在 Nios II IDE集成开发环境中,依照操作提示添加、设置相关参数,在几分钟之内就能生成一个 Nios II嵌入式处理器。其硬件开发进程为:

① 剖析体系所要完结的功用、到达的功用

② 发动 SOPC Builder,选取详细的 FPGA类型

③ 界说 CPU,外围器材,存储体系等模块

④ 为各个模块分配基地址和中止请求号(IRQ)

⑤ 生成 Nios体系模块,引脚确定,编译软件开发进程为:

① 在 SOPC Builder中发动 Nios II IDE

② 创立 C/C++软件工程,并指定方针硬件

③ 运用工程模本编写相应的程序

④ 编译后,即可下载到硬件中运转

Nios II IDE中能够选用 C/C++或许汇编言语进行程序的编写,其文件扩展名别离为 .c和.s。一个独自的 Nios II/f CPU大约需求占用 1800个 LEs,假如再添加一些定时器,外围器材等,那么占用的逻辑单元会进一步添加。

(2)数字信号处理块

StraTIx II系列 FPGA内部具有数字信号处理块( DSP Blocks,DSP块)。数字信号处理块能够支撑不同数据宽度的乘法器( 9×9、18×18、36×36)和操作形式(乘法运算、复数乘法运算、乘加运算和乘法累加运算),每个 DSP块供给了 2.8 GMACS的 DSP数据吞吐量。最大 StraTIx II器材 EP2S180内部含有 96个数字信号处理块,能够供给了 284 GMACS的吞吐量,能够支撑 384个 18×18乘法器。此外,数字信号处理块添加了新的舍入和饱满支撑,便于将 DSP固件代码导入 FPGA。一些运用如话音处理,因为寄存数据的存储缓冲是固定宽度,能够运用舍入和饱满。现在选用了支撑舍入和饱满的数字信号处理块,能够很便利地将根据 DSP处理器的规划导入到 FPGA中进行完结。

在 Altera的可编程器件上进行 DSP体系规划,需求有一起支撑高档的算法和硬件描绘言语的开发东西。MathWorks的 MATLAB和 Simulink体系级的规划东西具有了算法开发、仿真、验证才能。Altera的 DSP Builder将这些东西与 Altera的开发东西组合在一起,供给了一个体系规划、算法规划和硬件规划同享的 DSP开发渠道。

(3)视频图画处理 IP核第三方供给有许多运用于通讯、图画编解码、视频处理的可定制 IP核。合理地运用这些 IP核,在确保功用与牢靠性的一起,能够大大缩短开发时刻。下面介绍的是颜色空间转化 IP。

CSC(Color Space Convertorr)是 Altera公司供给的 MegaCore IP库文件中的一个专门用于图画颜色空间转化的 IP核,与软件转化比较,其具有显着的速度优势和灵敏性:

● 每个时钟周期完结一个像素点的转化

● 在 StraTIx系列 FPGA中,时钟频率大于 200MHz

● 支撑 RGB和 YCbCr、YUV之间的交换

● 用户能够自界说转化矩阵的相关系数

● 支撑有符号数和无符号数

输入输出的数据宽度为 2~32b 4 RAM数据缓冲区 StraTIx II系列 FPGA最多包含有 9Mb的片上 RAM。这些 RAM选用 TriMatrix存储结构,包含三种巨细的嵌入式存储器块,别离为: 512b的M512块,4Kb的M4K块和512Kb的M-RAM块,每个都能够装备支撑各种特性,如单端口 RAM,双端口 RAM,FIFO等,为大存储量运用供给处理方案。

3、 外部存储器和外设接口

Stratix II系列 FPGA为外部存储器的牢靠数据传送而进行了优化规划,支撑最新的存储接口拜访片外存储器。开发人员运用 Stratix II先进的器材特性和可定制的 IP核,能够快速和便利地将各种大容量存储器材集成到杂乱的体系规划中。Stratix II支撑各种最新的存储接口。Stratix II系列 FPGA片内处理器与外设之间是经过 Avalon交换式总线衔接的。 Avalon交换式总线是 Altera开发的一种专用内部连线技能,运用最少的逻辑资源来支撑数据总线的复用、地址译码、等候周期的发生、外设的地址对齐、中止优先级的指定等。外设接口可定制的 IP核有 USB、I2C、Ethernet、PCI等操控器,这些 IP核大多是由第三方供给的,能够免费试用,也可付出部分费用购买。本体系选用的 USB2.0操控器和以太网接口操控器均由 Mentor公司供给。

4、时钟办理电路

Stratix II系列 FPGA具有多达 48个高功用的低偏移大局时钟,它能够用于高功用功用或大局操控信号;多达 12个可编程锁相环( PLL),具有齐备的时钟办理和频率组成才能,包含时钟切换、PLL重装备、扩频时钟、频率归纳、可编程相位偏移、可编程推迟偏移、外部反应和可编程带宽。Stratix II有两类通用的 PLL:增强型 PLL和快速型 PLL。增强型 PLL功用丰厚,支撑外部反应、扩频时钟、可编程带宽等;快速型 PLL针对高速差分 I/O接口进行了优化,具有动态相位调整( DPA)功用。这些高速时钟网络和丰厚的 PLL结合起来,为体系在最小的时钟偏移下作业供给有力的确保。

5、 SoPC的其他组成部分

FPGA装备接口用于 SoPC的装备、编译和在线调试; LCD显现接口能够外接液晶显现屏;报警信号是在检测和辨认出运动方针时,宣布的声响或光电信号,可用于安防;规范

I/O口则是预留的,用于日后的晋级扩展。

立异点:SoPC概念提出曾经,电子体系的集成规划首要以板级为主,这种规划办法跟着体系时钟频率的不断提高和电路功用的日趋杂乱,完结的难度越来越大,电磁搅扰和信号完好性问题日益突出。仅靠优化 PCB的布局和布线,现已不能满意高速信号的传输和处理要求。跟着半导体工业的不断开展,可编程片上体系以其较高的功用、牢靠性,较低的功耗、本钱和杰出的便携性将成为未来电子产品开发规划的干流。而运动视觉 SoPC更好地处理了板级电路的一系列问题,并可广泛运用于安防监控、视觉导航、智能交通等很多范畴,必定会有杰出的市场前景。