1 导言

DP(DisplayPort)接口规范旨在寻求替代核算机的数字视频接口DVI(Digital Visual Interface)、LCD显示器的低压差分信号LVDS(Low Voltage Differential Signal),作为设备间和设备内的工业规范,并在若干范畴跃过DVI和高清晰多媒体接口HDMI(High Definition Multimedia Interface)这两种接口规范。DP运用现在沟通耦合电压差分的PCI Express电气层,有1~4个作业速率为217 Gb/s的数据对(Lanes),最高可获得4条通道一共多达10.8 Gb/s的带宽。时钟不是别离的,而是内置于Lanes。传输指令和操控的辅佐数据通道是双向的,最高传输比特率可达1 Mh/s。DP支撑的最大传输间隔为15 m,而其作业电平比DVI更低。

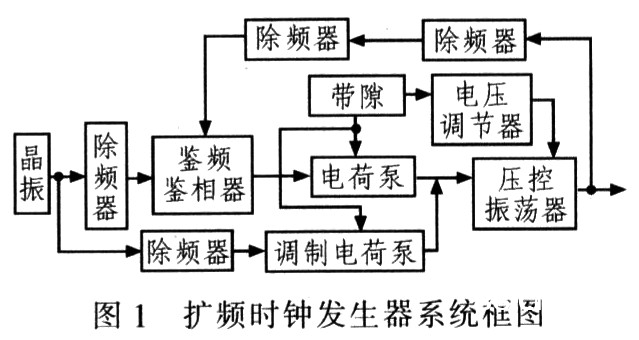

电子产品的功用不断提高,其微处理器的频率也在不断添加,由此发生的电磁搅扰会影响电子产品的正常运用。为按捺电磁搅扰,研究者们先后开宣布屏蔽、脉冲整形、滤波、低电压差分时钟、特别地图布局、扩频时钟发生器等办法,其间扩频时钟发生器可有用减小峰值和谐波功率,且可经过电路规划去完成,然后得到了广泛应用。这儿扩频时钟的完成办法是直接对操控电压进行调制,然后线性影响输出时钟的频率。调制信号关于输出是带通的,调制频率应在带通规模内:该信号经分频器后作为鉴频鉴相器的输出,需使调制信号的频率小于环路带宽K。

2 体系参数规划

该规划的主要任务是在合理规划锁相环路的基础上运用外加电荷泵对压控振荡器的操控电压进行三角波调制,得到所需的扩频时钟。图1为扩频时钟发生器体系框图。

2.1 锁相环作业原理

作为一种集成电路模块,锁相环在电气测控或功率改换体系中用来对输人信号进行处理后输出一个时钟信号,并使该时钟信号与指定频率信号(一般为基频信号)具有相同的频率和相位信息,即便这两个信号具有同步性(或称相干性)。锁相环的根本组件包含鉴相器、环路滤波器和压控振荡器,三者构成一个负反应环路结构,如图2所示。鉴相器用于判别压控振荡器的输出信号与输入信号之间的相差起伏,输出至低通滤波器进行滤波和滑润,以消除高频搅扰和其他不安稳要素的影响,并以此作为压控振荡器的操控信号。压控振荡器依据相位差错信号,自适应地调理内部时钟输出信号,使其频率和相位与输入信号保持一致,完成锁相功用。

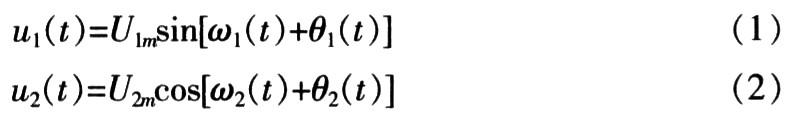

设锁相环的输入信号为u1(t),压控振荡器的输出信号为u2(t),且可表明为:

式中,ω1和ω2为信号角频率,θ1和θ2为信号相位。

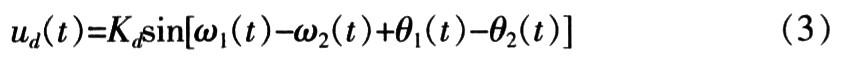

关于乘法型鉴相器,其输出的低频重量为:

式中,Kd为相差放大系数。

经反应调理后,鉴频鉴相器的输出相差将很小,式(3)可近似为:

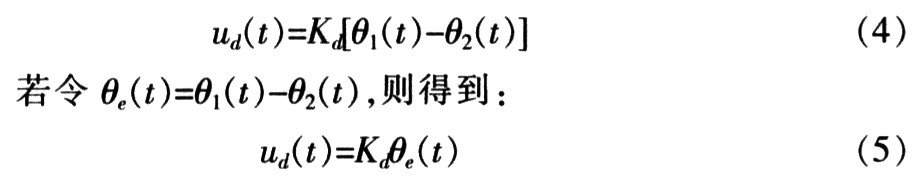

环路滤波器具有多种方式,这儿以一阶低通滤波器为例,如图3所示。

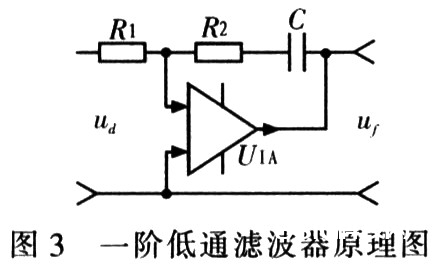

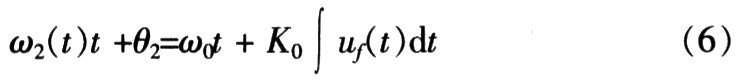

压控振荡器也具有多种方式,一般地,其输出信号的相位信息与输入电压uf之间满足:

式中,ω0为压控振荡器的中心频率,K0为积分系数。

经负反应调理后,鉴相器输出信号的频率ω2与ω0相差很小,因此得到:

当输入信号频率ω1(t)由于某种原因此发生改变时,必定引起相位信息的改变,该相位改变将直接反映在鉴相器输出与相位差错成份额的电压ud(t)上,再经低通滤波器取出的其间缓变量,进一步调理压控振荡器的输出信号与输入信号同步。可见,锁相环完成的是一种有差的相位负反应操控。

从信号加至锁相环的输入端开端,直到环路进入确认稳态的全进程,称为捕获时刻(亦称过渡时刻)。捕获时刻的巨细不只取决于环路的参数和开始状况,还与输入信号的方式密切相关。关于给定的环路设置,锁相环能否进入同步,还取决于开始频率差,若开始频率差超越某一规模,环路就不再具有捕获功用,难以完成对输入信号的同步盯梢。这个有用频率规模称为环路的捕获带。捕获带的宽度与环路的增益有关,增益越大,捕获带越窄。同步状况即经捕获使环路的状况安稳在|θe (t)|≤ε1和|θe(t)-2nπ|≤ε2,其间θe(t)表明相位差的改变速率,ε1和ε2为两个很小的正数。若输入信号的频率安稳不变,则环路进入同步状况后,输出信号与输入信号之间的频率差为零,相位差为2nπ,即|fe(t)|=0且θe(t)=2nπ;若输入信号的频率处于接连瞬变状况,即便其频率改变处于环路的捕获带内,也会呈现动态的盯梢差错,这是由于环路关于不同频率信号的捕获时刻(过渡进程)有所不同。

2.2 体系参数设定

锁相环路的体系参数在安稳时刻、功耗、噪声等方面存在折衷联系,所以设定参数需优先考虑某些要素,再优化。

(1)压控振荡器的电压灵敏度KV

在不清楚输入电压的情况下,首要假定压控振荡器的线性规模为1.1~2.4 V。为使其在各个工艺角下均能线性掩盖810 MHz和1 350 MHz两个频率点,线性规模略缩小。则:

Kv≈2(1 350-810)/(2.4-1.1)=830 MHz/V

此值在对应详细压控振荡器时需考虑相位噪声、线性度、功耗等要素进行折衷。这儿选用的双差分环形振荡器实践仿真得到KV=970 MHz。

(2)调制滤波器电流IS和调制频率f

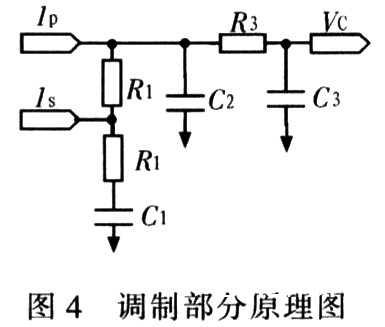

为便于剖析,分解出其调制部分,如图4所示,IP表明环路滤波器的电流,IS是调制滤波器的电流

当环路进入安稳状况后,Ip近似为0,得到传递函数:

当满足R1C1=R2C2时,近似得到:

因此发生三角波调制操控电压的作用,其电流比值可由式(2)推导出:

式中,f是调制波形的频率,△f是输出频率的调制起伏。

把f=30 kHz,△f=8.1/2 MHz(或13.5/2 MHz),KV=970 MHz代入式(3),得到,IS/(C1+C2)=250 A/F(或417 A/F),考虑到滤波器电流安稳性及电容巨细,取Is=2.5μA,C1+C2=10 nF(或6nF),这儿的电容值表明实践应取电容量级,不是最终值。

(3)确认环路带宽K

环路带宽需归纳考虑噪声按捺和确认时刻等要素。这儿的调制滤波器可形象地认为是人为的在压控振荡器的输入端参加一个噪声源,这个噪声尽管关于时钟输出是有必要的,但经环路后在鉴频鉴相器的输入端却是需要被滤去的,否则将影响锁相环环路的安稳性。滤波器只考虑R1,C1,经简略推导,得到传递函数如下:

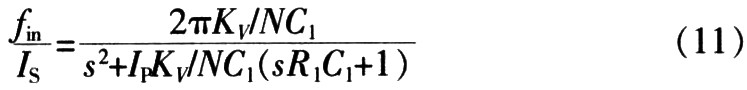

式中,fin是鉴频鉴相器的输入,IS是调制滤波器的电流。

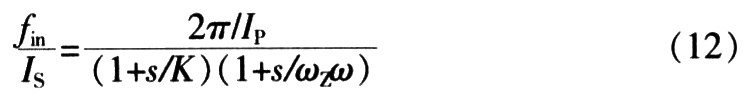

式(4)简略描绘鉴频鉴相器的反应输入与调制滤波器电流的联系。该传递函数具有低通特性,有s1和s2两个极点,经过假定s1>>s2得到s1=K,s2=1/R1C1=ωz,式(11)可表明为:

为按捺调制滤波器对环路的影响,除增大充电电流减小直流增益外,经过减小带宽K和锁相环的零点ωZ也能得到必定作用。但一起还需考虑关于压控振荡器的高频噪声。经过行为级仿真,带宽K取75 kHz。

(4)相位裕度取值

相位裕度取60°,对应γ=4,零点ωZ应处于K/4的方位,即37.5πkHz,而极点ωP1应处于4 K的方位,即600π kHz。在选用三阶滤波器时,需考虑引进的极点对相位裕度的影响,故γ一般取为5~6。

(5)滤波器中电流的挑选

滤波器充电电流IP=500μA。该电流值受限于滤波器电容的取值。

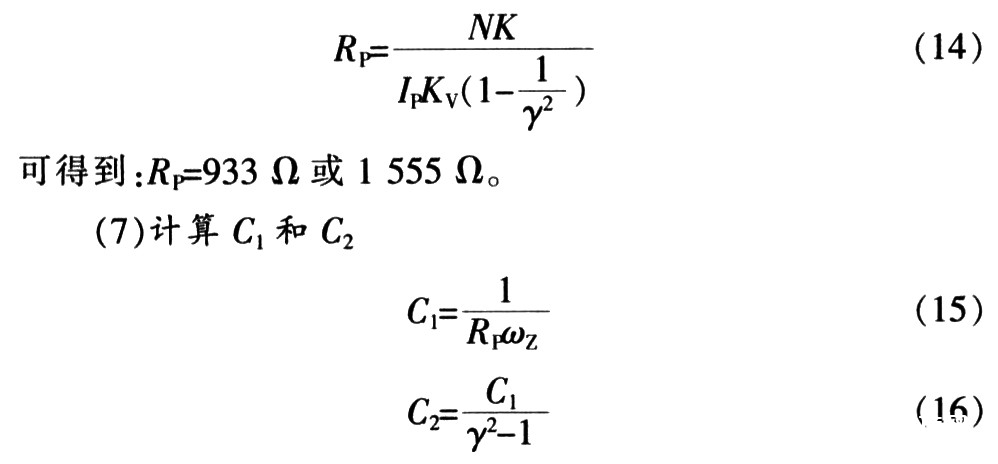

(6)核算RP(R1+R2)

对应于810 MHz和1 350 MHz的输出频率,别离取,N值为900和1 500。

核算C1=9.1 nF或5.4 nF,C2=0.6 nF或0.364 nF。

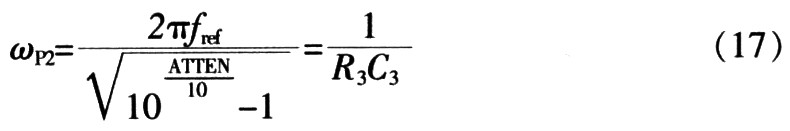

(8)R3和C3的取值

挑选适宜的R3和C3值以对毛刺进行滤波衰减。

由相位裕度的影响可知,R3和C3有必要满足:R3>2RP,C31/10C1。其间,fref是输入参阅频率,是额定的衰减值(dB)。取ATTEN=10 dB,fref=900 kHz,得到R3=3 kΩ,C3=174 pF。

以上核算所得参数还需满足使调制滤波器可进行三角波调制的条件,别的还需考虑削减用来操控滤波器参数的传输门及安稳性等要素。

3 体系仿真

这儿选用的体系参数规划带有必定的经历性,但其理论依据是线性反应操控体系理论,图5、图6、图7和图8列出了运用PLLsim软件对环路进行仿真的成果。

4 结束语

依据DP规范的发射端扩频时钟发生器的功用依赖于初始参数。依据线性反应操控体系理论并结合实践经历,对该组体系参数进行剖析,在归纳考虑数模混合电路的功耗、面积、功用等要素的基础上,规划锁相环的全体参数及各模块的功用参数。给出一组功用较优的参数值,该组参数为电荷泵和压控振荡器供给了安稳的电流和电压。别的,选用三角波调制压控振荡器操控电压的办法减小电磁搅扰。最终,运用PLLsim软件对环路进行仿真,得到了较满足的作用。