消耗数月精力做出的规划却无法满意时序要求,这的确十分令人悲伤。可是,企图正确地对规划进行束缚以确保满意时序要求的进程简直相同令人费心。找到并承认时序束缚自身一般也是十分令人头痛的问题。

时序问题的恼人之处在于没有哪种办法能够处理一切类型的问题。因为客户关于和现场运用工程师同享源代码一般十分灵敏,因而咱们一般都是经过将东西的潜力发挥到极致来协助客户处理其时序问题。当然好消息便是经过这种办法以及优化RTL代码,能够处理大多数时序问题。

但在深入探讨之前,咱们首要需求对时序问题进行一点底子剖析。这儿的方针是首要扫除显着的问题,如将时钟引脚置于器材的上部、在器材下部驱动数字时钟管理器(DCM),然后再在器材上部驱动大局缓冲(BUFG)。

有时,此类引脚布局会导致底子没有办法满意时序要求。经过调查时序陈述中的推迟,一般能够发现这些显着的时序问题。在这些状况下,为了处理这些显着的问题,都需求运用底层规划东西“floorplanner”将形成问题的部分承认在恰当的方位。底层布局规划东西还能够协助以可视的办法来了解时序问题。

用最新东西进行时序剖析

假定问题并非这么显着,那么为了承认问题所在,需求了解所运用的器材系列以及软件版别。一般,每种器材系列对应一种最优的软件版别。如Xilinx Virtex-4器材对应的最佳软件是ISE软件9.2i版,而对Virtex-5 FPGA则是ISE软件10.1版。

归纳东西的版别也很重要,因而当选用最新的器材架构时,下载并运用最新版软件十分重要。软件开发简直总是滞后于硬件功用,因而我不发起运用旧版软件进行依据新器材的规划。

可是,有些客户因为忧虑新的和不知道的软件缺陷而不愿意晋级软件。可是,在运用最新的器材时,假如期望更好地处理时序应战,强烈建议下载最新版软件。

具有了最适用于方针器材系列的软件,还需求承认最佳的完结选项。惋惜,并没有适用于一切状况的超级选项组合。关于规划完结东西来说,有不计其数种不同的完结选项组合。依据所运用的完结选项不同,时序分数(即一切存在过错的时序途径与时序要求的差异总和,以皮秒表明)也会有很大不同。

赛灵思的几款东西可协助承认适用于特定规划的最佳完结选项。ISE软件现在包含两个东西:Xplorer以及最近发布的SmartXplorer。SmartXplorer可充分发挥多处理器长处,能够以不同选项组合运转多个施行实例。

SmartXplorer需求Linux支撑,但运用十分简单。其命令行很简单:smartxplorer designname.edn -p xc5vlx110t-1ff1136.

只需用户束缚文件(UCF)和网表束缚文件(NCF)文件名相同,SmartXplorer会主动运用正确的选项。仅有需求做的是修改主机列表文件。

SmartXplorer能够经过SSH/rsh安全shell登录到其他机器。只需求在名为smartxplorer.hostlist的文件中将每台机器一即将机器姓名增加进去就能够了。假如机器有两个处理器,请将机器列出两次。

PlanAhead软件也包含了与SmartXplorer相似的称为ExploreAhead的功用。ExploreAhead支撑一起在多台 Linux机器上分布式运转布局布线使命。一切这些东西的意图都是相似的:承认完结东西的最佳选项组合,以取得最好的时序得分。

请注意选项的不同组合关于时序得分和运转时刻的巨大影响。细心调整归纳选项也十分重要。例如,在归纳选项中封闭结构层次(hierarchy)一般会大大提高功用。归纳进程中的束缚条件好坏在满意时序方面的作用也很杰出。

用PlanAhead剖析时序

在了解完结选项对最佳时序分值的影响之后,现在能够开端有效地剖析时序问题了。这时候,PlanAhead是一款十分有价值的东西,能够视觉化显现布局布线后的规划。运用它,还能够导入时序束缚并在已布局窗口穿插探查(cross-probe)时序失利的途径。

当东西自身的决议计划欠好时,则能够经过平面布局模块或经过手艺布局部分组件的办法来纠正。这一进程一般需求重复屡次,才能够承认时序优化的最佳规划布局办法。PlanAhead软件的可视化功用的确使这一作业的完结更简单了。

运用PlanAhead软件,首要创立项目(project),然后将HDL或网表文件导入东西中。一旦创立了一个项目,就能够挑选 “File→Import Placement”。挑选时序优化作用最佳的布局布线后(ncd)文件,将布局布线信息导入PlanAhead软件项目。

软件会将PlanAhead项目组织到几个不同的窗口。左上窗口是物理分层窗口,描绘了规划中的当时区域组。选定窗口在下面,包含了当时选定的数据详细信息。中心窗口是网表窗口,给出了整个网表的分层结构。最右侧窗口是器材调查窗(Device view),里边现已充满了规划施行完结后的逻辑。

然后,将时序剖析陈述(TWR/TWX)导入到PlanAhead东西中。挑选“File→Import TRCE Report”。这一步将时序陈述数据增加到底部窗口。依照时序余量(timing slack)对这一窗口进行排序能够将焦点首要集中于违背时序要求最多的当地。常常的状况是处理了这些时序误差最大的当地所存在的问题也就处理了整个规划的时序问题。

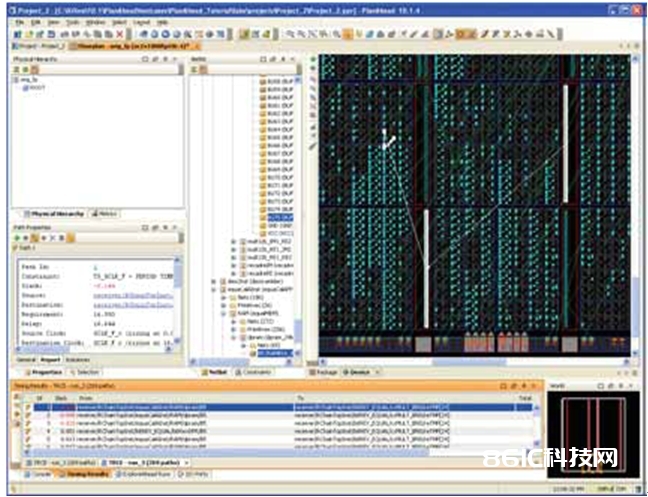

图1. PlanAhead 10.1版显现出已施行的规划,一条时序失利途径高亮显现。

一旦挑选了一条时序失利的途径,PlanAhead软件就会选定时序失利途径上的实例和衔接。按F9键扩大显现选定的部分。

这儿的工作显得有些杂乱。有必要进行必定的检查和考虑才能够显着布局布线东西将底子单元(primitive)放在某个当地,以及为什么关于当时的特定规划来说还有更好的办法。

能够扩大显现任何高亮的底子单元。鼠标点击一个底子单元并拖动,能够更好地调查其衔接状况。在网表窗口,还能够移动到包含了所选实例的顶层模块。鼠标右击模块称号并为选定的实例挑选色彩,这样就能够显现出这一模块在芯片中的布局,以及组内单元是接近仍是散开的。

或许发现有时需求更好地承认特定的底子单元。Block RAM和DSP模块的主动布局是导致时序失利的常见原因。很简单发现布局布线东西将Mult18组织的方位很欠好。时序失利途径中的块RAM输出衔接到 Mult18,后者的输出又馈送到进位链。块RAM在上部、Mult18在下部,而逻辑部分又坐落上部。假如布线不需求上上下下、边边角角地来缭绕,该途径应当能够满意时序要求。

时序问题不同,在PlanAhead软件中处理这些时序问题的处理方案也跟着改变。在PlanAhead规划东西中处理时序问题需求不断实践。该处理方案表现以下操作进程中:

1. 挑选高亮显现失利的时序途径。

2. 右击途径上的某个实例,挑选“Highlight With →color of choice”。

3. 在左边栏中,将底部第二个Mult18开释。右击“Unplace。这将为时序失利的块RAM腾出空间。

4. 点击拖动底部的Mult18向左上移动一个方位。

5. 点击拖动右边的块RAM到底部左边的自在块RAM方位。

6. 选定失利的时序途径,承认途径看起来是优化的。

7. 挑选“Tools→Clear PlacementConstraints”。点击第一个选项中的“Next”。

8. 挑选“Unplace All But SelectedInstances”。在余下的导游进程点击“Next”。

9. 假如期望在“PlanAhead软件外运转施行流程,挑选“File →Export Floorplan”。

10. 东西会输出一个新的文件名为“top.ucf”的UCF文件。你可直接运用这一文件,或许将文件中的束缚加入到原始UCF中。

11. 另一个挑选是在PlanAhead软件内运转施行东西。

挑选“Tool→Run ISE Place Route with ExploreAhead。

ExploreAhead供给了许多很好的功用,包含:主动从器材调查窗导入束缚到UCF;简化了从ExploreAhead中运转的布局和时序成果的导入。

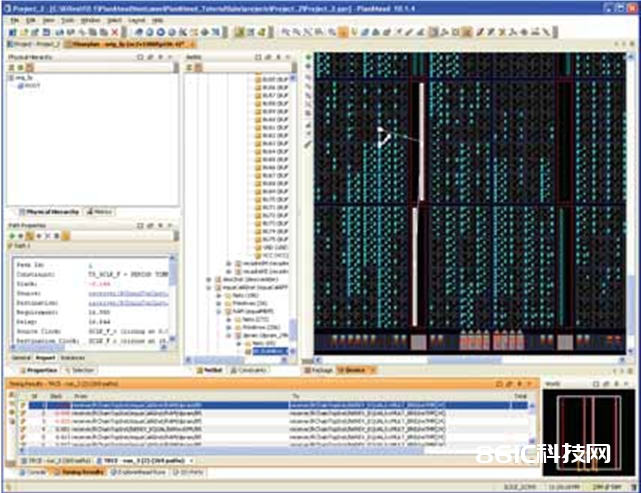

图2. PlanAhead 10.1版软件显现出将DSP48和块RAM承认后的正确途径。

Pblock和底层规划

假如发现布局中有许多时序失利途径,手艺布局调整一般无法处理问题。反过来,应当创立区域组。创立区域组(Pblock)的办法之一是在网表窗口中右击模块姓名并挑选“Draw Pblock”。然后在器材调查窗中期望放置区域组的当地画一个长方形。

东西会创立一个Pblock,一起会显现有关的详细信息。特点窗口会显现Pblock需求的逻辑资源以及画出的长方形区域组中可用的资源。

规划的底层规划是一个需求深度交互的进程。你或许会发现需求重复屡次调整区域组才能够到达方针。请记住有时创立的区域组越小越少越好。你并不是总需求将整个模块固定为区域组。集中于时序失利的底子单元,将它们组合为区域组并独自为其进行底层规划。

在此进程中,应当运用Pblock目标(Metrics)来更好地了解有关功用,如区域组中可装备的逻辑块(CLB)的运用状况如何(能够在 PlanAhead软件左上窗口中点击Metrics标签来检查可用的目标)。这可协助承认是否某个特定区域中太拥堵致使阻碍布线。假如的确比较拥堵,或许需求经过平面规划将规划逻辑放得散开一些。

一旦运用PlanAhead软件取得尽或许好的时序分数,最终的使命便是优化代码。PlanAhead规划东西现在支撑HDL源文件。依据你导入的源文件不同,你能够从时序问题动身经过穿插探查功用回查到网表或HDL。

运用原理图调查窗(Schematic view),能够调查整个时序途径。只需求从时序成果中挑选时序途径并按F4。细心调查从其他模块扇入扇出的逻辑。因为外部接口要求,东西或许常常需求将模块在芯片上散开布置。假如是这样,或许需求运用流水线。

Block RAM和DSP输出时序是引起时序问题的常见原因。经过在这些模块的输出进行存储,一般能够康复一纳秒乃至更多的时刻。