在测验中,意图是要赶快确认芯片是否以较高的安稳性正常作业,而不是肯定的安稳性。现在芯片规划团队遍及认识到,这需求在芯片上增加DFT(可测验规划)电路。第三方东西和IP (知识产权)企业可协助完结此方针。

而调试则彻底不同了。调试的意图并不只仅简略地确认芯片呈现了毛病,而是要找出毛病的原因。这种查看并不限于在测验台上的几秒钟,或许要继续数周时刻。它并不是主动进行的,而是需求芯片规划团队的参与。它呈现在规划周期中的离散点上:在第一个芯片规划阶段、在可靠性研讨阶段和现场毛病剖析阶段。

依据这种状况,可以幻想,出色的DFT 战略应可以满意芯片调试的需求,并且,实践上也往往是如此。跟着SoC(单片体系) 规划越来越杂乱,一流的规划团队表 示,他们将对支撑调试而不是测验的电路供给更多的方案、完结作业以及芯片面积。

“十年前在规划3层金属层时,这并不是什么大问题,”Bay Microsystems 工程部的高档副总裁Tony Chiang说。“假如芯片有问题,应该直接研讨金属层来调查电路,而关于聚集离子束体系则应该从头布线。现在,关于9层金属层和0.2mm金属距离,问题就不是

那么简略了。有必要将电路规划成具有从芯片外部能操控和能调查的,而在本钱和时刻预算上不超出咱们的方针。”

这种状况,简略扼要地描绘了调试规划界的状况。

技能概览

调试与DFT并不是彻底脱离的。Broadcom公司的测验开发工程高档总监Kris Hublitz举例介绍说,Broadcom有一个由70多名工程师组成的公司级团队,他们与公司其它的芯片规划团队一同从事调试和测验。Hublitz一再声称DFT厂商LogicVision是Broadcom芯片调试战略的首要协作伙伴。

其他人也赞同这种观念。“调试规划与出产测验并不是毫无关系,” CSR (Cambridge Silicon Radio) 的副总裁David McCall说。“两者的起点差不多。”

许多规划司理着重,这一同点便是探寻电路的能控性和能观性。调试与出产测验相似,底子问题是将电路设置在一个已知的状况,然后开端运转,调查其行为。在中等规划的集成中,鸿沟扫描技能可有用地完结此使命。因为芯片内部状况较少,可以全面地对其进行测验:将输入通过已知的一系列状况,对电路进行时钟同步,然后调查输出。

跟着微处理器的呈现,作业变得愈加杂乱了。微处理器有许多内部状况,所以只将输入施加给一个已知矢量并调查输出并不是特别有用。前期,业界尝试了多种技能使微处理器完结可调试,从对寄存器间的每群逻辑进行扫描到依靠同类的盯梢、断点及微机用于进行软件调试的单步函数等。将两种办法结合起来才干起效果。

现在规划人员对SoC的数字部分运用相同的东西套件。还有一些技能用于混合信号的模仿电路。但没有独自一种办法可以包含整个杂乱的SoC。所以,调试的规划流程包含将体系切割成独立的可调试模块,对每个模块施行一个调试战略,并将这些战略整合到一个完好芯片的方案中,使单个模块的用户接口相似并尽量削减电路需求的芯片资源。最终,规划师有必要运用这些调试资源从头查看,使彻底集成的芯片的运转既可操控又可调查,因为你不能只依据阻隔功用模块就能判别某些问题。

数字SoC

最底子的SoC 方法是由简略的往往是可编程的外设模块和内存所围住的CPU 核。大都状况下,CPU 核为第三方的IP,至少有一个内部调试内核的选项。软件开发团队常常着重这一点。此内核与规范的DFT 电路相结合,这种电路是规划团队为外设所施行的,以完结能观性和能控性来阻隔毛病。可以在CPU 核中运用这种调试内核,模仿核的非同步部分,以捕捉成果。通过让CPU 读写外设寄存器,此内核也可模仿并调查外设,一般答应规划师在可以处理的等级上确认扫描链中的毛病。

但现在并没有多少这么简略的SoC(图 1)。更多的状况下,芯片有几个或一群CPU 核和几种不同的处理器内核。某些外部操控器十分杂乱,只用CPU对其进行模仿来调查成果,并不能对其有用确诊。还有多个时钟域,它们之间一般相互并不同步。这样的芯片需求更有用的办法来调试。

在这种状况下,有几种战略可用。Broadcom的Hublitz介绍的一种简略办法是使一切首要功用模块的输入和输出可以拜访芯片的针脚。这种办法需求很多的多路复用。在有很多I/O 和内存接口的规划中,在引进任何额定拜访进行调试之前,芯片针脚数现已限制了,规划人员有必要复用针脚进行调试拜访。只将输入输出简略引出每个杂乱模块,或许比将其在主CPU 核上履行更有用,规划师或许需求引出内部信号。

一切这些多路复用和输入输出传送一同效果,或许并不太实践。并且,成果的额定互连会形成虽然一切模块可从针脚进行实践拜访,但其拜访速度底子达不到要求。这是一个严峻的问题。“咱们有必要要以全速测验电路,特别是模块间的互连,”Hublitz 说。“这关于65 nm工艺的芯片更是如此。否则会产生芯片中的毛病。”

Hublitz 着重,由ATE (主动测验设备) 支撑的出色的DFT 战略,可极大地有助调试进程。“咱们第一轮调试在ATE 体系上进行,”他说。“在咱们清楚了芯片不会消融后,把它交给规划人员,与他们一同协作。”Hublitz一起标明,芯片或许会不断地返回到 Broadcom的测验台,以使 ATE 体系收集很多的数据或进行速度查看。“自己内部有ATE 才干的真是很有用,”他表明。“咱们有28 个体系,大约每季度就增加一个新的,首要是用于调试,调试新芯片是咱们配备设备最首要的意图。”

虽然有了ATE 体系,某些信号和 状况仍是不能通过勘探卡的查看。需求选用其它的战略:内部仿真和逻辑剖析。有时,对模块进行快速仿真和捕捉其行为的仅有有用途径是将电路构建到模块内部。据Chiang介绍,Bay将其网络处理芯片安排成一串独立的处理器,并广泛运用这项技能。重要的模块可以有其自己的调试内核,包含单步和断点才干及盯梢缓冲器实时捕捉内部状况。Bay 的逻辑规划总监Jun-wen Tsong将这种办法描绘为多阶段验证流程。

“首要,咱们在模块级完结芯片。在这种形式下,每个模块都被阻隔开来:咱们可以注入满足的状况发动其运转,然后调查其独立运转特色。”这些测验有必要在最大时钟速度下进行,以确保精度。这样,规划师就可完结对一串处理器每级的调试。此刻,规划师还将I/O 环与内部模块阻隔,使输入可直接进入输出FIFO中。Bay 的规划师在独立验证I/O 环和内部模块后,再将两者结合起来全体地测验芯片。

以整个芯片全速运转收集数据,需求拟定全面的方案。单个处理器中的调试内核有必要不只可以辨认本地指令和数据字,并且大的图画数据对芯片运转也是十分重要的:如数据包和数据封包。别的,36位总线贯穿整个芯片,可实时将要害信号从任何模块传输到封装脚。使芯片以全速处理包时,调试工程师可以调查模块的运转。此外,硬件实时监测特定的断语,如FIFO full/empty 断语。Broadcom 也有相似的办法。Hublitz告知咱们,他们公司的无线局域网芯片有满足的内部调试硬件,工程师可以在整个芯片上盯梢向量起伏,从输入到基带直到输出。

在一个模块内一旦将问题阻隔到一个功用上时,依据相似DFT 的战略,调试工程师可运用初级确实诊东西。Bay 出色的工程师兼芯片架构师Barry Lee 说:“咱们在模块中有对触发和单步的时钟操控,并可扫描咱们以为重要的信号。抱负状况下,咱们可以切当地了解一个特别的流水线怎么履行到针脚和寄存器等级。”

模仿应战

当触及模仿电路时,一切都不一样了。“咱们将模仿部分与数字电路切割开来进行调试”Lee 解说道。“对两者的调试技能是不一样的。在模仿范畴,要打开环回途径,或许要将一切的调试拿到封装脚之外进行。因为在模仿电路中活动基元并不与时钟同步,因此无法对其进行捕捉。”

模仿电路与数字电路相似,跟着几许尺度的缩小,规划师现已看到了勘探和实验规划的才干,Analog Devices的Paul Ferguson 以为。“咱们习惯了将激光切割器用于勘探台来修正电路。后来,跟着几许尺度的减小,咱们搬运到了聚集离子束体系。关于250 nm 或更大的距离十分有用。这标明,实践上说,假如选用65nm 工艺,只能改动上面的两个金属层。”

这种状况引发了模仿规划风格的一个风趣的改动, Ferguson说。“最近咱们在做一项90nm 规划的PLL,咱们发现有必要首要完结VCO(压操控振动器),才干树立适宜的模型。所以,咱们引进了一些线路,将增益和其它参数调整到所能到达的上部金属层。这关于调试进程确实很有好处。”

Matt Ball 是单芯片无线电厂商Jennic公司的混合信号项目工程师,他也着重要将要害模仿信号置于可取方位的重要性。“咱们加入了尽量多的可编程性和数字调整功用,”他说。“有些东西有必要为金属微调的, 咱们将那些方位变成单一的掩模层等级完结可拜访性。”

除了将实时信号引到上部金属层或封装脚上,今日的模仿规划师还有其它兵器设定及调查电路的状况。最重要的是在微细几许尺度上进行,模仿电路与校准和监测它们的数字电路间要有亲近的协作。

CSR的McCall 说在其规划中,ADC监测器可确认模仿电路中数字监督电路的多个点。这些点通过将转化器的输出接到封装的外部,为调试工程师供给了拜访模仿部分行为的时机。“一般重要的模仿信号在某些点进行数字化处理了”Ball说。“为什么不进行采样,以片上DSP进行滤波,输出咱们可以看到它的成果呢?”

规划滤波器或放大器以便数字电路可以调理一切重要电气特性,这好像有些大动干戈了。可是在初次作业的芯片和在调试前有两层新金属掩模层的芯片之间产生的不同乃至可以发动规划的数字部分。并且,在小于90nm的工艺中,规划师有必要面临越来越强的可变性,这些由数字调整就成了有必要,这样才干出产满足数量的有用芯片。

怎么进行调整?关于无线电芯片上信号的精度和频率,IF (中频)信号,在测验形式中可以只用布线和模仿多路复用将信号引出封装之外。“在中频部分,缓冲器十分有用。”Ball 说。“从重要的节点获得信号送到针脚,就可以看到需求看的成果。”Analog Devices的Ferguson也赞同此观念。“就调试而言,往往不需求比模仿多路复用器所能供给的精确度高多少,就可以看到振动或20% 的增益差错。”

假如不能将信号引到封装之外,有时可以将 信号路由到片上数据转化 器。“芯片上一般有一个隶属ADC监测芯片温度,电池电压等等,”Ferguson 解说说。“在调试中咱们将巨大的多路复用器置于其前面,用来查看模仿部分的其它节点。但要当心:额定的丈量电路会损坏其它部分。例如,接通多路复用器调查节点,会进步安稳电路的振动才干。假如调试信号无意中跨过电源域,可以引进没有遇到过的寄生电流途径。”

Ball 也赞同这种正告,有必要挑选恰当的办法,他说:“缓冲模仿信号时所产生的10fF或20fF可改动节点的行为。” Jennic倾向于只依据曾经呈现问题的区域,如带隙电池,构建其调试方案。“咱们更喜爱增加旁通电路,以防呈现问题。”Ball弥补说。这种保守思想可下降毛病电路的呈现时机。

通过方案,加上命运,以及一点高雅,可以从头运用功用模块进行调试。许多模仿信号在数据转化器中停止,所以至少其间部分是可调查的。Ferguson 指出,可以轻松地开关s-Δ转化器作为滤波器作业,以对进入的模仿信号进行调查。或许当心肠将位流路由到针脚,在转化器两边都可调查。一旦对数据进行数字化处理,就可以运用CPU 或DSP 模块调理及紧缩或测验对其的断语。

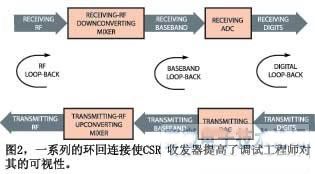

也可以将调试智能(相当于简略的网络剖析仪)构建到一个模块中。环回途径可运用发射器和接收器来相互查看(图 2),有些电路可以抽取成果的模仿波形。“在咱们千兆位PHY (物理层)规划中,咱们在PHY 块中捕捉到了一些模仿信号,”Broadcom Hublitz 介绍说。

发展前景

不难幻想,在体系规划前期阶段,每个功用模块接受满足的自检才干在全速运转期间进行本身确诊,并在DFT扫描链可处理的等级上完结这种才干。这种办法一般需求输入缓冲器或信号产生器对模块仿真,还要有输出捕捉寄存器或ADC 对其调查,以及满足的内部断点和盯梢才干提醒模块的内部作业状况。一些SOC 规划团队现在正在进行此项方案。这样实践的完结就成了架构师以为必要的调试支撑等级与规划所能接受的费用间的折中。

进一步拓宽此概念,完美体系的规划师可以运用重定某些功用模块方针,作为信号源或其它模块的捕捉设备。隶属的ADC 是个很好的比如,这样的时机还有更多。例如,增加快速数据转化器可以将信号处理模块变成网络剖析仪或数字示波器。对操控逻辑稍作增加,即可将缓冲器 SRAM 阵列转化为盯梢缓冲器。

按这种考虑方法,片上的功用模块可成为很多的调试资源,只重置几个多路复用器和形式开关即可。但此进程需求远见卓识。这样安排会影响平面规划和大局布线。有必要在规划开端时进行,而不能在最终的完结时进行。

Ferguson 以为,某些东西也可支撑这种进程。精细的东西可主动装置这种结构,如扫描链、扫描操控器及矢量产生器等。并且,DFT 硬件在寄存器等级确实诊上是必不可少的。可是,并没有支撑创立调试结构的东西。Ferguson至少想要看到一种将混合信号模块视为具有能观性和能控性,并能扫描查看简略过错的检测东西。抱负状况下一种东西应该可以贯穿于一项规划,并能提出一种调试架构和工艺。但这是今后要处理的问题。