ARM的NEON协处理器技能是一个64/128-bit的混合SIMD架构,用于加快包含视频编码解码、音频解码编码、3D图画、语音和图画等多媒体和信号处理运用。本文首要介绍怎么运用NEON的汇编程序来写SIMD的代码,包含怎么开端NEON的开发,怎么高效的运用NEON。首要会重视内存操作,即怎么改变指令来灵敏有用的加载和存储数据。接下来是因为SIMD指令的运用而导致剩余的若干个单元的处理,最终是一个比方来阐明用NEON来进行SIMD优化。

SIMD的比方

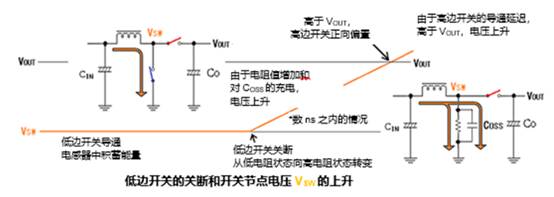

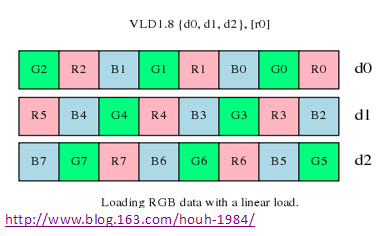

首要看一个实例,24-bit的RGB图画,像素在内存里的安排方法是R, G, B, R, G, B…,假如你想做一个简略的图画处理,比方把R和B通道交流,你该怎么高效的运用NEON协处理器呢?首要从存储空间线性加载RGB数据到D寄存器,然后交流R和B数据。 可是这种线性加载的数据进行R和B通道的数据交流十分费事,需求首要掩码mask,然后移位并兼并掩码数据。这种杂乱的运算明显并不高效。

图1. 线性加载RGB数据

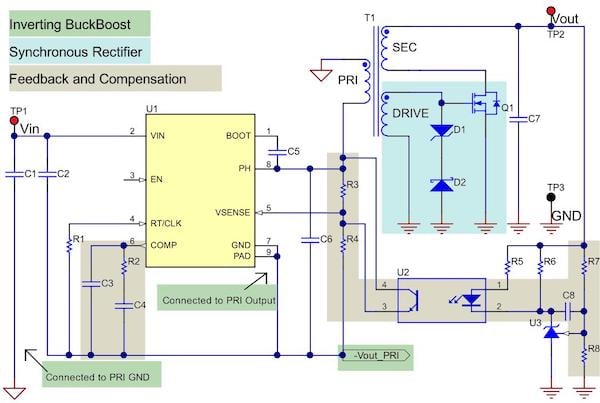

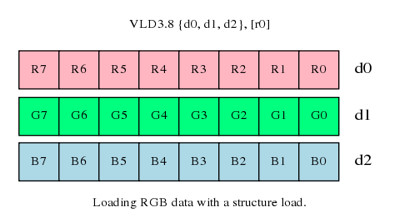

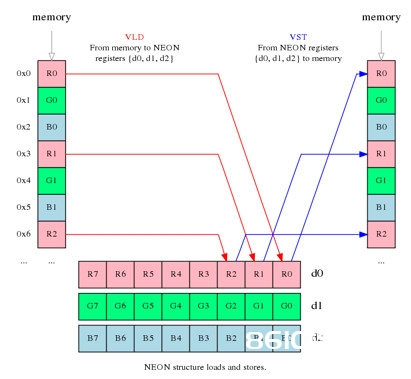

NEON供给了各种结构的加载和存储指令来处理这种状况,这些指令能把数据从存储区加载的一起还能把这些值分隔存储到不同的寄存器中,如下图2所示,你能够运用VLD3加载来把RGB数据分隔存储。

图2. 运用结构化的加载指令加载RGB数据

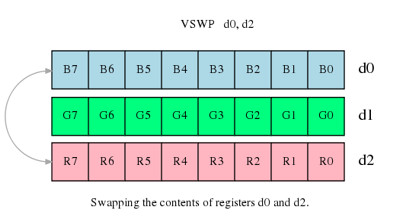

然后运用VLD3分隔加载的数据就能便利的运用指令(VSWP d0, d2)来进行R和B通道的交流了,然后把成果再写入内存,当然也要运用interleave交错方式的存储,即VST3存储指令。

图3. 交流寄存器d0和d2然后存储

结构化加载和存储语法和具体指令

NEON结构化加载会读取内存内容到64-bit的NEON寄存器,运用可选的deinterleave选项,相同加载指令也能够选用这种reinterleave的方法把寄存器的内容写到内存空间。

图4. NEON的结构化加载和存储

下面介绍NEON存储和加载的结构化方法,语法包含如下5个部分:

图5. NEON的结构化加载和存储语法

- 加载VLD或许存储VST指令助记符:instruction mnemonic

- 一个表明interleave方式的数字,表明每个结构体元素间的距离:interleave pattern

- 表明每次拜访单元的位宽比特数,即结构体内元素类型:element type

- 读写的64-bit的NEON寄存器调集,最多能够列出4个寄存器,取决于interleave方式:NEON registers

- 表明内存拜访地址的ARM寄存器,该地址能够在每次拜访时更新: ARMaddress register

交错方式:Interleave Pattern

加载和存储指令能够用从1到4个相同巨细的元素的交错结构体,这些元素能够是NEON指令一般支撑的8,16或许32比特。

- VLD1是最简略的方式,从内存加载1~4个寄存器的数据,没有deinterleave,即线性加载;

- VLD2加载2或许4个寄存器的数据,解交错奇偶元素到各自的寄存器,这样很简单的把交错的立体声音频数据分化为左右声道的数据;

- VLD3加载3个寄存器的数据,很便利的把RGB的数据分为R、G、B通道;

- VLD4加载4个寄存器的数据,解交错,用于分化ARGB图画数据;

存储和加载相似,仅仅把寄存器的数据interleave然后写到内存。

元素类型Element Types

加载和存储interleave的数据的根本元素能够为8,16或许32比特的数据。比方NEON指令VLD2.16将加载4个16-bit元素到第一个寄存器,然后4个16-bit元素到第二个寄存器,把接近的奇偶对分隔保存到每个寄存器。

图6. 加载并解交错16-bit的数据

把元素巨细变成32-bits仍是加载相同巨细的数据,可是只要2个元从来构成一个向量,相同分红奇偶元素部分。

图6. 加载并解交错32-bit的数据

元素巨细还会影响巨细端的处理。假如你指定了正确的加载和存储指令的元素巨细,从存储空间读取和存储的字节都会依照正确的次第摆放,因此相同的代码会在大端和小端体系里适用。最终元素巨细还会影响指针的数据对齐,把数据对齐到元素巨细的鸿沟能带来更好的功能,当然这也是一般的操作体系OS要求的。如,加载32位元素数据,一般要把第一个元素的地址对齐到32位鸿沟。

单个或许多个元素 Single or Multiple Elements

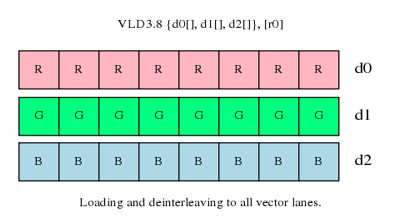

除了加载多个元素,结构读取还能从内存用deinterleave的方式读取一个元素到NEON寄存器的多个通道或许一个通道而保存其他通道不变。

图7. 加载并解交错到一切的通道

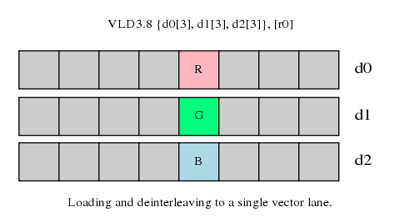

加载到单一通道关于从涣散的内存空间的数据读取来构建一个向量十分有用。存储数据到内存也是相同,也能够选用通道的方式进行存储。

图7. 加载并解交错到单一的通道

寻址方式Addressing

NEON的加载和存储指令支撑3种格局的寻址方式:

- 寄存器 [ {,:}]:数据将会从指定寄存器的地址加载或许存储;

- 带主动加减地址更新的寄存器[{,:}]!:在数据从指定寄存器的地址加载或许存储后会更新地址,更新的地址巨细等于读取或许存储的数据元素巨细;

- 带后索引的寄存器[{,:}],:存储空间拜访后,会依据拟定的寄存器Rm来更新地址,当需求读取或许存储一组具有固定距离的数据时十分有用。

其他的加载和存储

NEON还支撑以下的数据加载和存储:

- VLDR和VSTR来加载和存储64-bit数值到一个单一的寄存器;

- VLDM和VSTM来从仓库加载或许存储多个64-bit数值;

更多的关于支撑的加载和存储运算能够参阅ARM的参阅手册arm.com/help/index.jsp?topic=/com.arm.doc.ddi0406b/index.html” rel=”nofollow”>ARM Architecture Reference Manual. 具体的指令周期信息能够参阅每个独自的指令Technical Reference Manual for each core.