一、阐明:

功用:AM调制

渠道:Vivado 2016.4 和 Matlab R2017a

二、原理:

1. AM调制原理

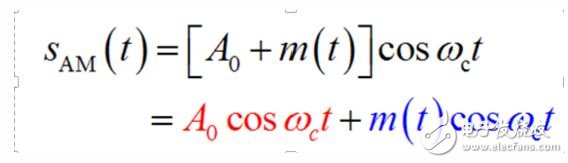

AM已调信号的时域表达式:

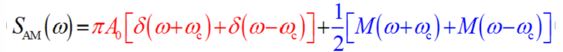

已调信号的频域表达式:

本质上AM调制便是频谱的搬移。

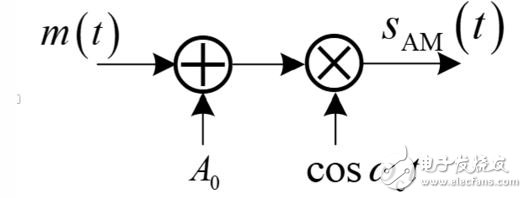

AM调制的体系框图

将调制信号加上一个直流重量,确保信号的最小值大于零,然后再和载波相乘,得到已调信号。

三、AM调制的FPGA完成

1.发生调制信号和载波信号

调用ROM IP核在FPGA内部发生两路余弦信号,其间一路信号用于模仿外部输入的调制信号,另一路用作载波信号。

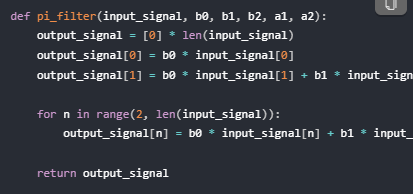

在装备ROM IP核之前,需求用Matlab生.coe文件,存放在ROM核里。

Matlab生成.coe文件:

%———————————%

width=8; %设置rom的位宽

depth=1024; %设置rom的深度

%———————————%

x=linspace(0,2*pi,depth); %在一个周期内发生depth个采样点

y_cos=cos(x); %生成余弦函数

%y_cos=sin(x); %生成正弦函数

%y_cos=round(y_cos*(2^(width-1)-1))+2^(width-1)-1; %将数据转化成整数,生成无符号数

y_cos=round(y_cos*(2^(width-1)-1)); %将数据转化成整数,生成有符号数

plot(x,y_cos); %绘图

fid = fopen(‘E:\Workspace\DDS\Design\IP_Core\cos.coe’,‘wt’);

fprintf(fid,‘memory_iniTIalizaTIon_radix = 10;\nmemory_iniTIalizaTIon_vector = ’);

for i = 1 : depth

if mod(i-1,8) == 0

fprintf(fid,‘\n’);

end

fprintf(fid,‘%6d,’,y_cos(i));

end

fclose(fid); %封闭文件

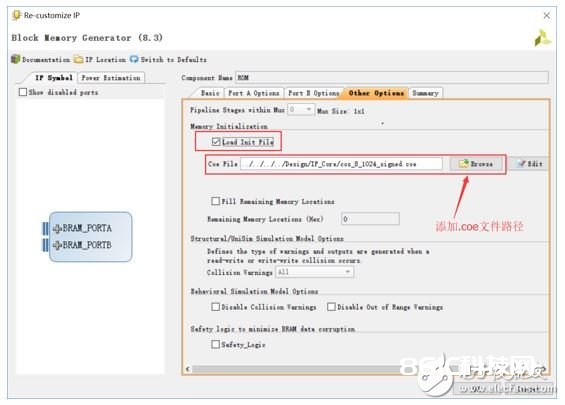

生成.coe文件后就可以进行IP核的装备了。

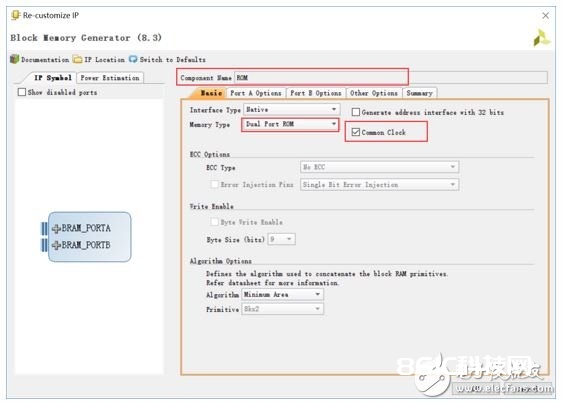

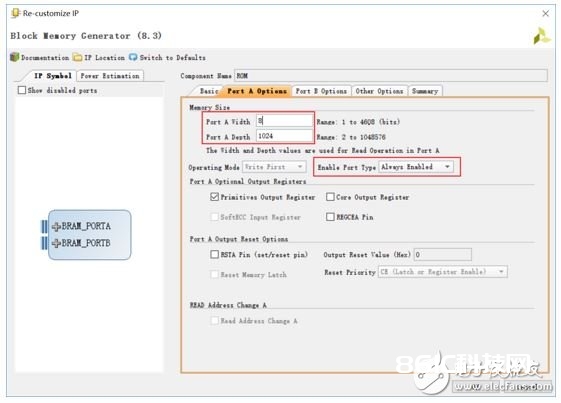

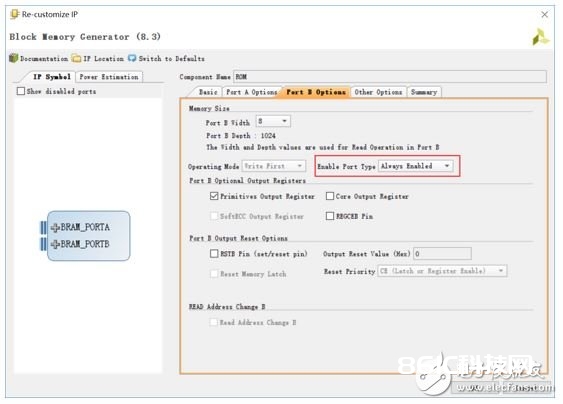

ROM核详细装备:

装备完IP核后,编写操控模块,发生两路信号。其间,调制信号上叠加的直流重量的巨细为调制信号的峰值,这样将得到调准则为100%的已调信号。假如要得到不同的调准则,则需求叠加不同巨细的直流重量,一起需求留意界说的数据位宽,避免数据溢出。

发生载波和带有直流重量的调制信号:

module cos_make(

input clk,

input rst_n,

output reg [7:0] cos_s,

output reg signed [7:0] cos_c

);

//————————————//

parameter freq_s = 32‘d429497; //调制信号频率10k

parameter freq_c = 32’d42949673; //载波频率1M

parameter cnt_width = 8‘d32;

//————————————//

//————————————//

reg [cnt_width-1:0] cnt_s = 0;

reg [cnt_width-1:0] cnt_c = 0;

wire [9:0] addr_s;

wire [9:0] addr_c;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

cnt_s 《= 0;

cnt_c 《= 0;

end

else begin

cnt_s 《= cnt_s + freq_s;

cnt_c 《= cnt_c + freq_c;

end

end

assign addr_s = cnt_s[cnt_width-1:cnt_width-10];

assign addr_c = cnt_c[cnt_width-1:cnt_width-10];

//————————————//

//————调用ROM核—————-//

wire signed [7:0] cos_s_r;

wire signed [7:0] cos_c_r;

ROM ROM_inst(

.clka (clk),

.addra (addr_s),

.douta (cos_s_r),

.clkb (clk),

.addrb (addr_c),

.doutb (cos_c_r)

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

cos_s 《= 0;

cos_c 《= 0;

end

else begin

cos_s 《= cos_s_r + 8 ’d128; //加上巨细为峰值的直流重量

cos_c 《= cos_c_r;

end

end

endmodule

2.生成AM调制信号

得到两路信号后就可以用乘法器将两路信号相乘,得到已调信号。

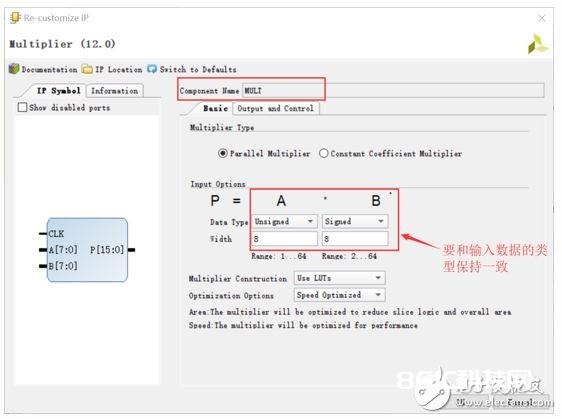

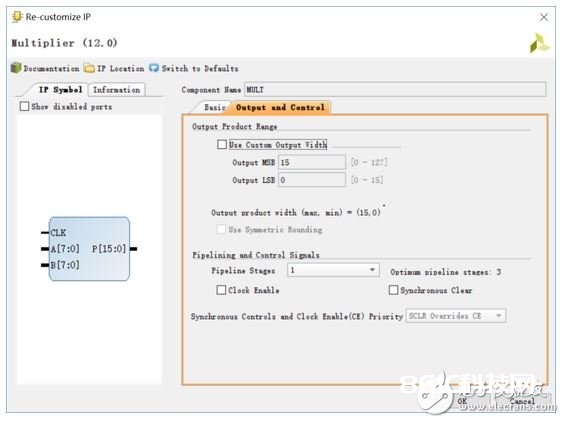

乘法器详细装备:

AM调制的顶层模块:

module modulate(

input clk,

input rst_n,

output signed [15:0] AM_mod

);

wire [7:0] cos_s;

wire signed [7:0] cos_c;

//————调用出波模块————//

cos_make cos_make_inst0(

.clk (clk),

.rst_n (rst_n),

.cos_s (cos_s),

.cos_c (cos_c)

);

//———————————–//

//————调用乘法器————–//

MULT MULT_inst1(

.CLK (clk),

.A (cos_s),

.B (cos_c),

.P (AM_mod)

);

endmodule

3.仿真调制成果

以上AM调制进程基本完成,可是正确与否还需求经过仿真来确认,接下来编写仿真用的测验模块。

TestBeach的编写:

timescale 1ns/1ps

module tb_AM();

//———接口设置———-//

reg sclk;

reg rst_n;

wire signed [15:0] AM_mod;

//————————–//

initial sclk = 1;

always #5 sclk = ~sclk; //100M时钟

initial begin

rst_n = 0;

#500

rst_n = 1;

end

//————————–//

modulate modulate_inst0(

.clk (sclk),

.rst_n (rst_n),

.AM_mod (AM_mod)

);

endmodule

在Vivado中将各个文件添加进工程后,运转仿真。

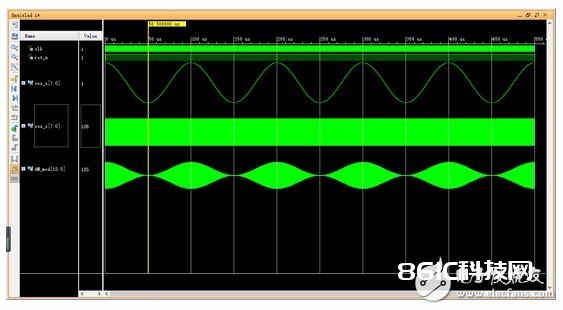

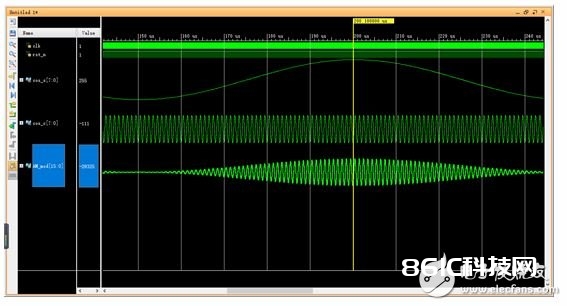

仿真成果如下:

已调信号能显着看到包络,而且包络的频率同调制信号共同,标明AM调制正确。