对依据数字信号处理器(DSP)的体系而言,优化功耗是一项重要但往往难以完结的规划方针。现在,依据DSP的设备常常把以往各自独立的多个运用结合起来,每一个运用都或许有多个作业形式。要得到这样一个设备的功率散布是十分困难的一件事,更遑论整个杂乱的体系。规划人员需求获悉尽或许多的最佳信息,以及可以协助他们优化特定运用之功耗的技能和东西。

走运的是,近年来,在DSP芯片的规划和制作工艺方面,都在不断推出更先进的功耗下降办法。现在的片上功率优化技能可以供给更多的精密操控和更多的省电形式,以及关于处理器功耗的更完好的信息。更新式的DSP开发东西使规划人员得以更深化透彻地了解体系的功率耗费办法,并经过片上硬件来供给功耗下降技能。

为了让开发人员可以更灵敏地操控省电技能,更好地和谐很多片上功用间的低功率作业和时序问题,DSP操作体系整合了多项功率办理功用。这些内建功用及东西加上体系规划的精心布置,DSP体系的功耗可得到大幅度下降。

低功耗问题

低功耗对一切的DSP体系都很重要,虽然理由因详细运用而异。在网格供电体系中,下降功率就意味着下降开支、进步可靠性,以及完结紧凑型规划,然后可以在相同的空间中集成更多的功用性,一起需求更少的电扇和其它冷却技能。在高清医疗成像等要害运用产品中,器材作业产生的热量乃至或许导致运转毛病,因而,低于设备最大额定值并添加对低功耗的要求是至关重要的。

在便携式电子体系中,低功耗有助于尽量减小体系的尺度及分量,一起把电池充电后的运用时刻延至最长。较小电池的运用可进一步下降体系的规划。更低的功率还有助于防止便携式体系在延时运用期间过热。因功耗下降,手机、PDA、MP3播放器、数码相机和视频摄像机这些电子仪器及其他手持式设备的尺度都日趋纤小,作业温度越来越低,而充电后的运用时刻越来越长。

了解功率散布和芯片资源

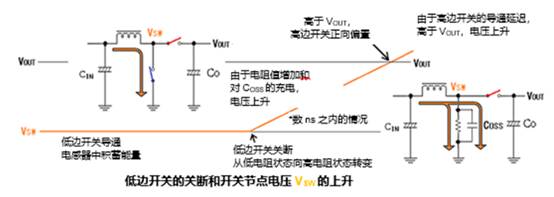

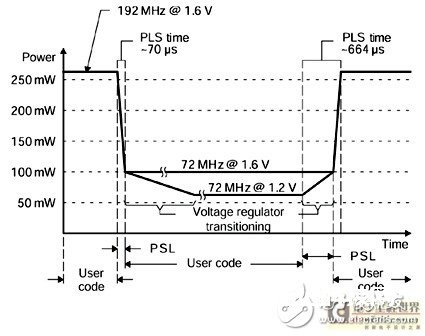

在任何类型的体系中,下降功率的榜首步是了解体系的运用办法,以及这种运用是怎么影响功耗的。比方,手机大部分时刻都处于等候呼叫的状况中,实践通话的时刻适当少。另一方面,MP3播放器一般不是开机处于激活运转状况,便是处于关断状况。其它体系、线路供电体系以及便携式体系,都有着不同的待机功耗散布和激活作业功耗散布,拜见下面的图1。

图1:作业功耗和待机功耗

了解功耗散布有助于规划人员挑选一个具功率功率的处理器,因为在某些类型的运用中,DSP的根本CMOS技能或许对功耗产生很大的影响。先进的CMOS工艺则依据作业电压极低的高功用晶体管。依据既定运用,可以量身定做晶体管,经过对静态电流进行钳位把功耗降至最小,或把功用进步到最大,虽然这样会略微添加走漏电流。专门为手机这样的待机时刻很长的运用而规划的DSP,可经过低走漏晶体管把静态电流降至最低,而为总是处于激活状况的高功用运用而规划的DSP则较喜爱开关速度更快的晶体管。

体系运用还包含体系对各种事情的呼应,以及电路接通电源时的推迟。初始上电时或许有一些推迟,而体系从待机形式被唤醒时,较小的推迟是可以承受的。但用户一般都期望处于激活作业状况的体系可以即时呼应,故而这时片上功用不能处于深度睡觉形式。这里有两方面的考虑:榜首,部分功用可以较其它功用更彻底地关断,特别是在待机期间,激活作业期间也如此。第二,处理器的功率形式操控才能越精密,规划人员就越可以进行充沛的功耗调理以合适体系的操作状况。

高功率功率的DSP芯片规划经过树立电源域,使运用可以堵截不在运用中的功用的时钟输入,然后把一切这些要素都考虑在内了。正如处理内核可以进入睡觉形式,此刻它不履行任何操作,直到被中止信号唤醒,外设和存储器模块也相同可以被置于睡觉形式,在需求时才被唤醒。无时钟输入功用中的晶体管除静态电流之外,没有什么功耗,而康复时钟所需的唤醒推迟被减至最小。体系规划人员在考虑其产品的运用状况时,还需求考虑到在为各项功用供给时钟方面,DSP可以供给多少操控才能,或是否可以主动处理。

节能DSP内建的另一项功用是可以调理中心电压和频率。假如DSP可下降中心时钟速率并依然满意其处理要求,则作业功耗会相应地按份额节约。更低的频率加上更低的作业电压,可以节约适当可观的能量。可以在体系发动时调理电压和频率以适于整个体系的运转,也可以在运用需求改动时经过软件对之予以动态操控,这就为非峰值处理期间的功耗削减供给了一种重要的手法。

正确功率信息的取得

杂乱DSP体系或许具有多个内核、运用和办理形式,这使得对功率的预算极端困难。传统的功率确认办法依据某些信息来完结,比方器材数据手册上注明的最大电流值,每周期或每条指令的耗电量(mA/MHz, mA/MIPS)以及测验事例等。

这些办法只能用来做大略预算,但对内核、外设和片上存储器可以依据运用和操作形式进行独立开关的杂乱体系而言,是不足以预算DSP功耗的。规划人员需求清楚了解实践运用中片上各项功用的详细功耗,因为实践的功率信息使他们可以愈加精确地预算出不同完结计划的成果,并测定出在不同渠道上运用是怎么影响功耗的。

在DSP制作方面,所需求的是模块化的功率预算计划,即把设备划分为若干子体系,然后独立运转每一个子体系。一旦确认了每一个片上功用的最大功率值和闲暇功率值,就可以经过插值法为一个功用树立一条功耗曲线。所以,在清晰了每一功用的运转等级之后,可以把从各条曲线取得的功率值累加,终究给出整个设备的实践功率预算值。

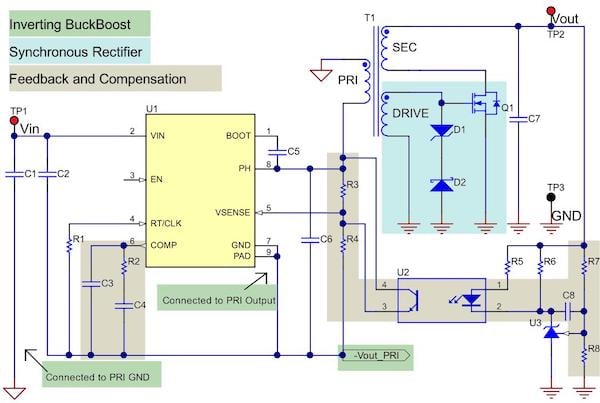

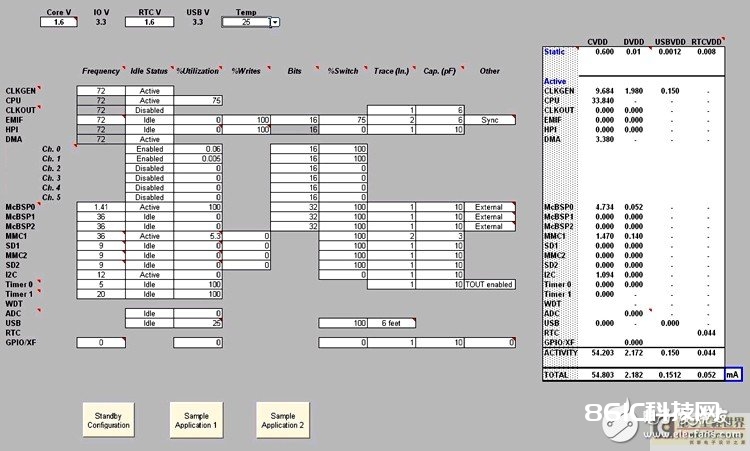

图2是一个功率预算电子数据表,它把一个典型的DSP分解为若干个子体系,由用户输入相关参数,然后可以回来设备的功率预算值。就像这个电子数据表所显现的,预算是否正确取决于用户供给的信息是否反映出对体系运用办法的杰出了解,包含数据宽度、频率、电源电压和运用中外设的可用带宽的百分比等要素。

图2:功耗预算

低功耗规划

具有功耗认识的规划(Power-conscious design)技能可以协助DSP规划人员充沛运用正确的功率预算。在体系级,规划人员应该精心挑选相关元件,使其数目尽或许地低。此外,规划人员还应该考虑到哪些未运用的元件可以置于省电形式,特别是在待机期间。板级存储器的运用也是一个功率耗费源,因为有必要一起给存储器芯片和电路板迹线供电。

运用应该尽或许地运用DSP的内部存储器,以坚持片上大带宽存储,把外部存储器保存用作偶然的低速存取。片外存储器也可以很好地完结发动作业,但应该在发动后被置于省电形式。为了削减存储器中的代码量和所取指令的数量,应该优化软件进步功用。更紧凑的代码有助于更好地运用缓存和内部指令缓冲器,并且运转速度更快,故能削减体系处于激活形式的时刻。

大多数特定设备都是运用DSP的内建硬件才能来下降功耗的。从一发动开端,运用设备就 可以让不运用的模块处于闲暇状况,外设功耗只限用于那些在指定时刻才需求的I/O 。运用一般在发动时就直接操控各个模块,稍后,DSP内核可以后台履行一个循环来检测哪些功用不需求,然后把它们关断。假如运用采用了这些技能,芯片的睡觉形式就可以把闲暇期间内核及芯片的功耗降至最低。

若所要求的整体功用不等于设备的悉数才能,则可以在发动时就对DSP内核电压和频率(V/F)进行调理。若体系在具有不同功用负载的运用间替换,V/F调理也可以在运转期间动态进行。要完结V/F调理,规划必需供给DSP外部电源电压操控,以及内建于后台循环程序的软件操控。因为频率调理减慢内核的运转速度,规划人员在运用规划中应该考虑到彼此相关的各个操作间的时序问题。

OS中的功率办理

不论是经过V/F调理仍是经过低功耗形式来动态改动体系的功率要求,都需求涉及到DSP的实时操作体系(RTOS)。RTOS中的功率办理(PM)模块可以在发动时完结功耗节约,并在整个体系上和谐各个低功耗操作。

内核频率调理会影响子体系操作的时序,因而PM可以在完结频率调理之后进行时钟调理。假如对运用来说OS时钟精度不重要,或者是用户期望节约空间,则可以不运用PM功用

此外,当线程被阻断时,用户还可以激活或停用主动使时钟处于闲暇状况的PM功用。在其和谐效果中,PM供给了一种用于功率事情告诉的注册功用,当特定功率办理事情产生时,客户可以注册告诉,因为体系的杂乱性,PM支撑多个客户端并答应客户推迟事情的完结。

PM还供给了一个运用编程接口(API)库,可完结芯片的低功率技能软件操控。经过这些API,运用可以门控时钟,激活睡觉形式并安全办理V/F调理设置点之间的晶体管。这些设置点作为调理参数,使V/F可以依照正确的次序下降和进步,并且具有正确操作所必需的设置时刻。

下面图3显现了设置点是怎么操控V/F调理的时序的。因为电压和频率调理对规划中所用的DSP和电压调理器是特定的,PM API支撑设置点推迟查询和装备,一起PM库可被重建。

图3:功耗调理成果

东西的辅佐开发功用

要有用处理上述一切技能问题,需求一些专门为功率办理而规划的东西。类似于DSP东西开发的其它范畴,功率优化东西也致力于供给可视化和易于运用的优势,以协助简化体系分析并缩短上市时刻。

这些东西结合DSP的嵌入式及RTOS功率办理技能,可以供给计量表、示波器波形、信道校准、测验代码和事情触发等等测验功用。运用这些快捷功用,规划人员可得到一个反应机制,凭此评价各个完结计划对功耗的影响,终究取得一个最佳计划。

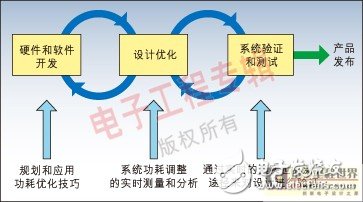

图4显现了在规划周期中,集成的硬件和东西渠道,比方国家仪器有限公司(National Instruments)的C55x电源优化DSP入门套件(DSK),可以怎么以及在什么地方协助开发人员在不同的规划环境下评价DSP的功耗,然后使是他们可以更迅速地选定最合适其体系的最佳低功耗/高功用整体计划。

图4:功耗优化流程

从一开端就进行功率规划

在体系开发中,功率优化有时被当作一项过后作业来处理,但这是不对的。在开发周期中,越早考虑功率优化问题越好,关于具有多个运用和作业形式的杂乱体系而言特别如是。为了延伸电池作业时刻,低功耗一般是首要的要求之一,即使是线路供电体系也需求经过下降耗电量来削减散热和运转本钱。

为了优化功耗,规划人员需求了解体系的功率散布,以供给全面的参阅信息源,然后在功率预算中把一切首要的体系功用都考虑在内。依据高功率功率的CMOS工艺的DSP集成了硬件技能,比方精密界说的低功率形式和电压/频率调理。API使这些技能很简单经过RTOS完结运用操控,测验东西可协助规划人员预算出不同完结计划的功耗。运用这些资源,开发人员有充沛的理由从开发周期的最开端就进行功率规划。