摘要:当今嵌入式信息处理体系运用日益广泛,嵌入式信息处理的效能成为需求处理的重要问题,文章介绍了一种依据双DSP作业的信息处理渠道的规划,该规划运用两种不同的DSP芯片TMS320C6202和ADSP2187别离作为主从处理器,处理器之间运用IDMA接口进行通讯,DSP协同作业完结很多数据收集和核算作业。

0 导言

跟着嵌入式运用领域的敏捷扩展,对嵌入式的软硬件规划的要求更高。在弹载嵌入式体系规划中,对模块的实时性和数据收集等方面有着更为严厉的需求。在这种隋况下,对硬件规划提出更高的要求,不只要求解算速度快,且处理的操控算法也越来越杂乱,使得核算量变大,占用了很多的时刻,形成时序严重。一个DSP的核算操控才能现已不能满意类型研发需求,归纳考虑多种计划,就技能的老练性、可行性及类型研发周期考虑,在核算机的核算才能没有满意余量的条件下选用双 DSP计划,即选用2块DSP芯片。双DSP体系的长处在于能够经过核算才能的均匀分布,使体系具有较好的冗余才能、更快的处理速度、模块化的体系结构。

本文介绍一种依据双DSP的信息处理渠道的规划,该规划尽管本钱不高,可是可在某弹载信息处理体系中高实时性的完结各种数据的收集和核算。

1 体系总体规划

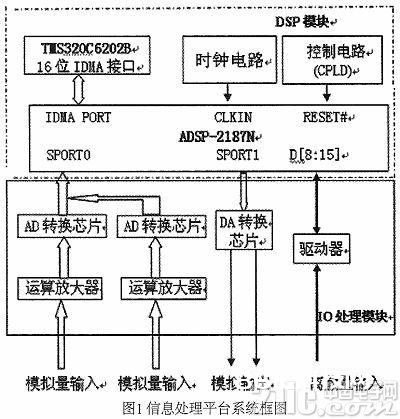

该信息处理渠道选用双处理器规划,然后完结收集量大、运算杂乱、实时性强的需求。双处理器选用了TMS320C6202B和ADSP2187N,前者作为主处理器,用于数据的运算、处理以及对外部接口的通讯,后者作为从处理器用于模仿量数据输入输出、离散量输出操控等。两者之间经过内部直接存储器存取 (IDMA)通道进行通讯,该规划能够高效率、高可靠性的完结多路数据收集和处理等功用。

2 体系硬件规划

该处理模块结构如图1,DSP模块含有两片DSP以及时钟电路和操控电路。IO模块首要含有模仿、数字电路用于数据收集。

双DSP计划选用类型研发中现已老练运用的DSP作为处理器,选用主从式规划结构。主从DSP和谐合作,共同完结软件功用。

2.1 DSP模块

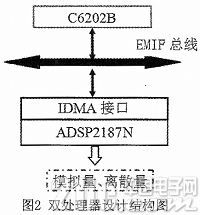

DSP模块包含两个DSP芯片,其间C6202B是DSP模块上的主处理器,它担任整个处理渠道的使命办理、调度以及数值核算。ADSP2187N是 DSP模块上的从处理器,它履行来自IDMA接口的程序,担任办理IO处理模块上的模仿量收集与输出、离散量的输入。双处理器联系如图2:

IDMA接口是主处理器与从处理器通讯的通道,C6202B能够经过ADSP2187N的IDMA接口直接拜访其片上RAM。此外,ADSP2187N没有片内可固化程序的存储器,它的程序要C6202B经过ADSP2187N的IDMA接口来加载。

2.2 IO模块

IO模块首要用于进行离散量的输入输出,以及模仿量信号的收集和输出。

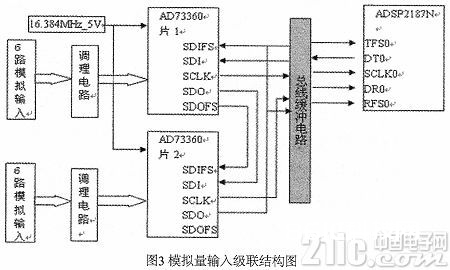

AD电路前端选用8片双路运算放大器TLC4502ID将外部幅值为±15V的模仿输入信号整形降压,经过AD73360AR转化为数字信号,再经过总线缓冲器74LVC244A阻隔驱动输入到从处理器ADSP2187N,在规划中模仿量量的输入选用两片AD73360级联结构方法完结。级联方法如图3。

D/A电路完结将数字信号转化为模仿信号输出的功用。DAC7714UB选用SPI总线接口与ADSP2187N衔接。

离散量由ADSP2187N数据线输出,输出后由经16373锁存后输出,并完结3.3V到5V电平转化。离散量输入信号经过另一片总线缓冲器74LVC244A空余的4路输入到ADSP2187N。

3 软件规划

3.1 规划思维

该信息处理渠道相应的软件用于完结对应硬件规划的主从CPU的通讯和作业形式操控。

从处理器ADSP2187N没有内置的非易失数据存储空间,假如需求在该DSP上运转程序,有必要经过各种数据通讯接口从外部加载,该信息处理渠道经过IDMA通道,将数据从主处理器的FLASH上加载到从处理器。

首要,需求运用ADSP2187N的编译东西将运转于ADSP2187N上的程序依照协议生成纯数据文件,该文件可被C6202B主处理器上的程序辨认。

其次,在运转中,需求从处理器进行各种数据收集作业的时分,主处理器将对应需求运转的程序经过IDMA通道写入到从处理器的内存空间,并告诉从处理器运转程序进行数据收集。

最终,从处理器将收集成果相同经过IDMA接口回来给主处理器,主处理器依据收集成果进行各种核算,可经过串行数据接口回来给上位机。

3.2 规划难点

运用了双处理器导致双处理器间的和谐作业难度增大,尽管主从处理器有各自的优势,但运用两种不同的DSP,尤其是各自的编译环境不同,则对软件完结要求比较高,C62 02B需求运用CCStudiov3.3环境,ADSP2187N需求运用Vistlal DSP++环境,两种处理器的编译环境彻底不同。为了处理该问题,将从处理器上的程序编译后经过协议转化成纯数据文件,主处理器的程序将这些数据文件编译在一起,这样,两个DSP作业程序就可结合在一起,可由主处理器的程序进行操控。主处理器程序运转期间需求从处理器作业,则从FLASH中将从处理器的运转数据文件经过IDMA通道直接加载到从处理器运转。这样主处理器对整个体系的运转程序都是可操控的,也就能够对整个渠道的作业进行一致的调度。

4 成果剖析

从同类类型设备的比照中看,运用双DSP后,比相似类型中数据量收集的才能高出近一倍,一起也能很好满意实时性要求,从软件运转视点看,因为运用了双DSP,对软件的要求尽管有了更高的要求,可是关于软件空间、时刻余量均有所提高。

5 定论

本文介绍的信息处理渠道,运用了不同公司的DSP,两个DSP各有自己在嵌入式体系中的优势,可是关键在于两者之间的信息高效和谐作业的问题上,本文介绍的硬件计划,可最大的利用了两DSP的优势,使得体系能够实时快速的完结信息处理作业。提出的软件计划使得双DSP能够安稳的进行通讯和操控,该规划已在某弹载设备进步行运用,可满意体系要求的实时性和高数据收集的要求。