跟着无线通信技能的快速开展,能够兼容不同通信协议的多规范收发器已经成为当时研讨热门之一。而模数转化器(ADC)作为其间的一个重要模块,也遭到越来越多的重视。在收发器中不同的接纳方式下,体系对模数转化器的采样频率和分辨率位数的要求不同。为了满意体系需求,每一种接纳方式都要对应一个特定采样频率和分辨率位数的模数转化器。因而,关于一个存在多种接纳方式的多规范收发器来说,只是在模数转化器方面就需求占用较大的芯片面积及较长的设计时间。

本文首要规划了一种可重构流水线结构模数转化器。该模数转化器经过重构装备操控电路产生一组操控信号来挑选不同的流水线级数及时钟信号,然后产生一个采样频率(最高可达50MS/s)和分辨率位数(6~12位)必定的模数转化器。此外在规划中还选用了共源共栅两级运算放大器及差分动态比较器技能来优化电路的速度及功耗。仿真成果表明,这种可重构流水线结构的模数转化器能够主动完结采样频率及分辨率位数(6~12位)的可重构,特别适用于多规范收发器中。

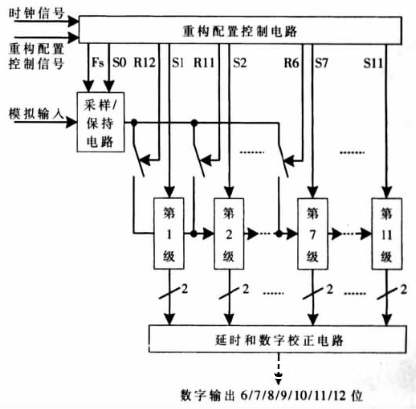

1 可重构流水线ADC的结构

可重构流水线ADC的结构示意图如图1所示,它由一个采样坚持电路、11级1.5位/级的流水线、一个重构装备操控电路、延时和数字校对电路等组成;其间前面10级流水线结构彻底相同,每级都包含一个2位的子ADC和一个MDAC电路;第11级流水线是一个2位的全并行ADC。

整个可重构流水线ADC的作业原理如下:重构装备操控信号送给重构装备操控电路,重构装备操控电路则依据重构装备操控信号的巨细从时钟信号中挑选一个时钟频率送给采样坚持电路作为采样时钟信号,一起也作为整个ADC的时钟信号。这样,不同的重构装备操控信号就可能挑选不同的时钟信号,然后完结ADC采样频率的装备。在产生时钟信号的一起重构装备操控电路也宣布一组操控信号S0~S11及R12~R6操控11级流水线的作业状况,其间操控信号R12~R6在ADC作业期间只要一个是处于有用状况,亦即R12~R6所操控的开关只要一个是处于导通状况,其他都断开。由此决议可重构流水线ADC分辨率的位数,并经过S0~S11把没有用到的流水线级数关断,以节约功耗。例如:当R11有用时,ADC的分辨率位数为11位,采样坚持电路的输出直接送给第2级流水线作为其输入,一起把第1级流水线关断以节约电路的功耗。当ADC的采样频率和分辨率位数装备之后,整个电路的作业情况就同一般结构的流水线ADC[3]相同,由采样坚持电路对输入的模拟信号进行采样,并将坚持的采样值送给与之相连的流水线级。接纳到采样值的流水线级就对接纳到的信号进行转化处理,产生一个2位的数字信号送给延时和数字校对电路,一起产生一个余量增益信号送给下一级流水线作为其输入信号。以此类推,直至终究一级流水线转化完结。各级流水线转化完结后产生的2位数字信号经延时对齐及数字校对后得到终究的数字输出。经过不同的重构装备操控信号,该模数转化器能够完结采样频率(最高可达50MS/s)以及分辨率位数(6~12位)的动态装备,能够满意多规范接纳器在不同的接纳方式下对采样频率巨细及分辨率位数的需求。

2 要害电路规划

2.1 采样坚持电路

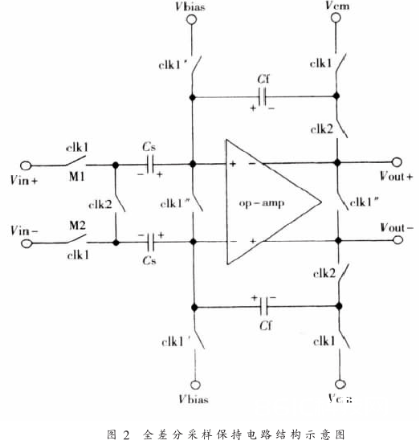

采样坚持电路是流水线ADC中要害的模块。它在采样周期时,对输入的模拟信号进行精确采样,在坚持周期时,将采样成果坚持一段时刻,即完结模拟信号的离散化,其速度和精度直接决议了整个流水线ADC的速度与精度。本规划中选用了全差分结构底极板采样电荷转移结构采样坚持电路,其结构示意图如图2所示。该电路运用两相非交叠时钟,除了时钟clk1之外,还存在时钟clk1′和clk1″,依照clk1′、clk1″和clk1的次序顺次闭合,然后再相继断开。

依据时钟,该电路的作业可分为采样和坚持两个阶段。在采样阶段,时钟clk1、clk1′和clk1″有用,运算放大器的两个输入端被短路,电容CS对输入信号进行采样并以电荷的方式存储起来。在坚持阶段,clk2有用,存储于CS上的电荷转移到电容Cf上,然后完结了对采样电压的坚持。因为选用了全差分结构、相应的时钟操控以及底极板采样技能,能够有用地下降开关沟道电荷注入、时钟馈通、共模电压、温度漂移等的影响,进步了电路的精度。此外为了减小由输入采样开关M1、M2的非线性导通电阻引进的非线性,还选用了栅压自举电压操控的NMOS采样开关以改善采样开关的线性度,进步精度及输入信号的规模。

2.2 运算放大器

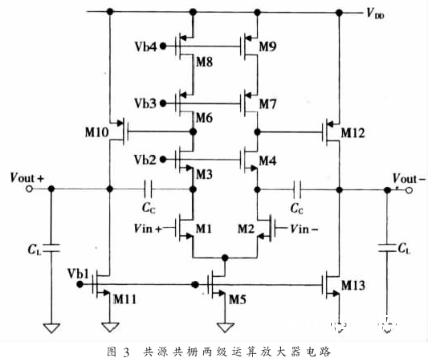

运算放大器是采样坚持电路的中心,其功能直接影响采样坚持电路的速度和精度,是流水线ADC电路规划的要害。本规划选用共源共栅两级运算放大器[4],其榜首级选用高速的套筒式共源共栅运算放大器来补偿两级运算放大器速度慢的缺陷,因而整个电路具有相对较高的增益、较高的速度、较低的功耗和噪声及较大的输出摆幅等特色,其电路结构如图3所示。

因为在榜首级中选用了共源共栅(cascode)结构,极大地进步了榜首级的输出阻抗,具有较高的增益。其直流增益可表示为:

![]()

在规划中选用了共源共栅补偿,即在榜首级的cascode结点和第二级的输出结点之间接了一个补偿电容CC。这种补偿产生了一个低频主极点,并在较高频率处产生了两个互补的零点和极点。这种补偿办法同Miller补偿比较,在进步相位裕度的一起,能够供给更大的带宽。补偿电容CC的巨细关于运算放大器的相位裕度和单位增益带宽都有很大的影响,而且跟着CC的添加,运算放大器的单位增益带宽会下降,而相位裕度则会增大。

仿真成果表明,该运算放大器在3.3V的电源电压下,直流增益为98dB,单位增益带宽为348MHz,相位裕度位为61度,彻底能够满意体系的要求。

2.3 动态比较器

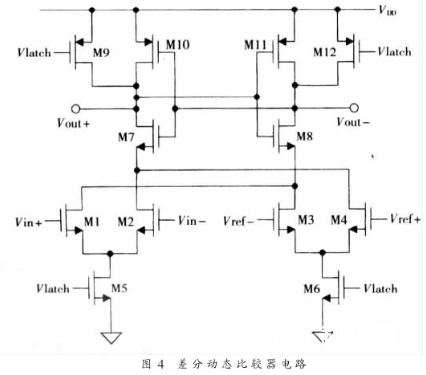

在流水线ADC中,每一级内部的子ADC都是一个由多个比较器组成的全并行ADC,能够说比较器是整个ADC中运用最多的单元电路,其功耗是整个ADC功耗的一个重要组成部分。因为选用了数字校对技能,能够对比较器的输出信号进行校对,因而对比较器的失调目标要求比较宽松,使得在比较器的规划中,在满意速度要求的前提下,能够经过献身精度来下降功耗。本规划中选用差分结构动态比较器[5],它由穿插耦合的差分对和锁存器负载组成,因为整个比较器电路的电源和地之间不存在直流通路,因而不耗费静态电流,其结构如图4所示。

当Vlatch信号为低电平时,M5、M6管截止,M9、M12管导通,比较器的两个输出端悉数被置位为高电平,此刻,M7、M8管导通,M1~M4管的漏端被充电至(VDD-VT),而M5、M6管的漏端电压则由比较器的输入信号决议。当Vlatch信号为高电平时,M9、M12管截止,M5、M6导通,差分对开端作业,对(Vin+-Vin-)和(Vref+-Vref-)进行比较,引起比较器左右两个支路也即两个输出端的泄放电流不同,然后导致锁存器产生翻转,输出比较成果,一起电源电流也被堵截。

由上面的剖析能够看出,在整个比较过程中,功率耗费只是产生在转化瞬间,其静态功耗能够忽略不计;一起该比较器的输入管在比较开端时作业在饱满区,具有较大的跨导,因而这种差分结构的动态比较用具有较高的速度和分辨率。仿真成果表明,该比较器在不同的仿真条件下失调电压小于15mV,树立时刻约为3ns,而功耗仅为0.2mW。

3 仿真成果与定论

本文依据0.18μm CMOS数模混合工艺模型,运用Hspice对流水线可重构ADC中的要害电路进行了仿真,并运用Matlab对整个可重构流水线ADC进行了行为级仿真。表1总结了在不同的重构操控装备信号下,即在不同采样频率和分辨率位数下,可重构流水线ADC的有用位数。从表1能够看出,所规划的可重构流水线ADC在给定的采样频率和分辨率位数下,都达到了规划要求。

本文在传统流水线结构模数转化器根底之上添加了一个重构装备操控电路及其他部分电路,规划了一种可重构流水线结构模数转化器。该模数转化器能够依据输入信号规模及体系需求经过一个重构装备操控信号来动态地装备采样频率的巨细及分辨率的位数,特别适用于多规范收发器中。在实践运用中,依据输入信号的频率规模及体系需求,能够经过重构装备操控信号来装备ADC的采样频率和分辨率位数。

责任编辑:gt