塑料光纤(POF)具有柔软性好、易于衔接等长处,在短距离通讯中得到广泛注重,继其在轿车内部网络的成功运用之后,室内通讯网络将是塑料光纤通讯的下一个巨大商场[1-3]。但塑料光纤因为芯径粗,形式色散大,构成信号波形经传输后失真大,高速率传输时码间搅扰严峻。奈奎斯特(Nyquist) 榜首原则告知咱们:假如信号经传输后整个波形发生了改动,但只需其特定点的抽样值坚持不变,那么用再次抽样的办法,依然能够准确无误地康复原始信号。依据这一原则,假如在发送前,选用奈奎斯特FIR滤波器将数字基带信号进行成形滤波,紧缩旁瓣,就能够大大减小码间搅扰的影响,然后下降误码率。因此,滤波器的规划在塑料光纤通讯体系中占有重要的位置,它的功能将直接影响整个通讯体系的功能指标。

现在FIR滤波器的完成办法主要有3种:单片通用数字滤波器集成电路、DSP器材和可编程逻辑器材。单片通用数字滤波器运用方便,但因为字长和阶数的规范较少,不能彻底满意实践需求。运用DSP器材完成尽管简略,但因为程序次序履行,履行速度较慢,在某些实时性要求高的场合中受到限制。可编程逻辑门阵列(FPGA)有着规整的内部逻辑阵列和丰厚的连线资源,选用的是硬件并行算法,特别适合于实时通讯要求高的场合[4,5]。塑料光纤数字基带传输体系的方针是完成100 Mb/s以上的传输速率,成型滤波器的作业频率较高,而FPGA的本钱不断下降,所以用FPGA来规划塑料光纤通讯成型滤波器具有显着的优势。

1 基带升余弦滚降数字滤波器规划

满意奈奎斯特榜首原则的滤波器有无量多种,最常用的是升余弦滚降滤波器。升余弦滚降滤波器的时域表达式为:

式中,0α1为滚降系数,Ts为码元宽度。可见升余弦滚降滤波器是一个无量阶数的系数对称滤波器。为了能够在硬件电路上完成,有必要截取其间一部分阶数。

因为实践规划中只能选用有限阶数有限精度滤波器,因此规划的滤波器频率呼应与抱负频率呼应之间存在差错。为了减小差错,需求对滤波器进行优化。衡量差错的规范有两种:一种是最大差错最小化原则,便是使滤波器频率呼应在必定的频率范围内与理论滤波器频率呼应比较最大差错最小;另一种是最小均方差错原则,便是使滤波器的频率呼应与理论滤波器频率呼应比较差错的均方值最小。本文选用了最小均方差错优化的原则,对升余弦滤波器的系数进行优化。

Matlab的freqz函数能够方便地核算滤波器的频谱,可用于滤波器的优化。其进程是:挑选一对对称的系数,添加或削减一个量化的最小单位(8位二进制量化最小单位是1/128);假如系数改动后频谱差错削减就选用改动后的系数,不然坚持本来的系数;挑选新的一对系数,重复上面的进程,一向调整到差错不能再减小停止。例如取滚降系数a=0.22,取样频率为4,FIR滤波器的有限长度N为23,能够得到其起伏和相位呼应如图1(a)所示,相应的滤波系数如图1(b)所示。

2 升余弦滚降数字滤波器在FPGA上的完成

分布式算法DA(Distributed Arithmetic)是一种以完成乘累加为意图的运算办法。关于FIR滤波器的输出y(n)能够看作是滤波系数(即单位冲击呼应)与输入信号x(n)的卷积和,其表达式为:

关于有符号的DA数值,最高有用位用来差异正数和负数,其x(n)可写成:

式中xb(n-i)表明x(n-i)的第b位,将式(3)代入式(2)中,可得FIR滤波器的分布式算法DA表达式:

式(4)中方括号的乘累加在DA中使用查找表LUT来完成,查找表的地址矢量xb=[xb(K-1)……xb(0)],即查找表的地址有K个输入信号的同位权位组成。假如滤波器的系数为B位,则一个DA查找表规划为2N×B bit。能够看到抽头系数N过多,则DA表的规划将非常巨大。这是因为LUT的规划跟着地址空间的改动(也便是N的添加)而呈指数添加。

在塑料光纤数字基带传输体系中,为了削减FPGA逻辑资源的占有量和进步体系的运转速度,对升余弦滚降数据滤波器需求进一步优化处理。优化包含两个方面:一是在FPGA完成中使用特有的查找表进行优化,一是对表达式进行优化。

对查找表的优化,能够使用部分表核算,然后将成果相加。长度为LM(N=LM)的内积为:

这样就能够将和分配到L个独立的M阶并行DA查找表之中,表格的规划从一个2N×B bit降到L×2M×B bit,一般M控制在4个或8个最好。假如再加上流水线寄存器,因为大部分FPGA芯片的每个逻辑单元都有一个寄存器,所以并没有添加电路规划,却能大起伏进步电路的履行速度。DA算法的主要特色便是奇妙地使用了ROM查找表将固定系数的MAC运算转化为查表操作,其运算速度不跟着系数和输入数据位数的添加而下降,并且相对直接完成乘法器而言在硬件规划上得到了极大的改进。

对表达式进行优化,考虑到升余弦滚降滤波器系数是奇对称的,h(i)=h(N-1-i),兼并对称的部分能够削减大约一半的乘法运算,即

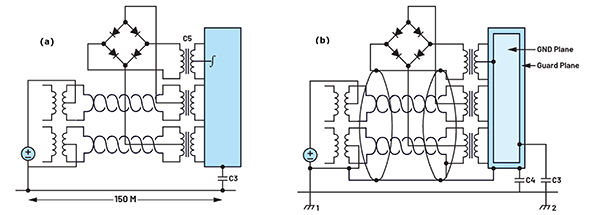

依据优化的分布式算法和使用FIR滤波器的线性相位特性,能够极大地进步电路的履行速度[7]。升余弦滚降滤波器的FPGA完成电路原理图如图2所示。图2中的加法树选用树形结构削减多个数累加次数的办法,即Wallace树结构加法器。Wallace树充分使用全加器3-2紧缩的特性,随时将可使用的一切输入和中心成果及时并行核算,因此能够将N个部分积的累加次数从N-1次削减到logN次,大大节省了核算时延。图3为Wallace树结构与CSA结构的对照,其结构的要害特性在于使用不规则的树形结构对一切准备好输入数据的运算及时并行处理。Wallace树结构是一种高速加法器,其明显长处是速度快,特别对处理多个数相加的状况具有适当的优越性。

3 优化成果与剖析

塑料光纤数字基带传输体系升余弦滚降数据滤波器的规划首要选用MATLAB确认滤波器参数,发生一个滤波器的模型对给定的技术参数进行迫临,依据迫临成果得到的滤波器模型、滤波器系数,再用FPGA进行终究的硬件完成。

本FIR升余弦滤波器是在Altera公司Quartus II6.0版别软件开发环境下,并运用了该公司的Cyclone系列的FPGA芯片(EP2C5类型),进行FPGA程序编译和时序仿真。VHDL强壮的行为描绘才能和程序结构,使其具有支撑对大规划规划进行分化,以及对已有的规划进行再使用的功用。本文选用VHDL言语编写了完成FIR升余弦滚降滤波器的FPGA程序代码,经编译完成后只是需求254个LE逻辑单元,节省了很多的资源,该算法具有极大的优势,能够有用处理在FPGA规划中资源严重的问题,用VHDL言语完成硬件的流程图如图4所示。依据图1(b)中在Matlab中仿真核算出FIR数字升余弦滚降滤波器的量化系数,依照上面描绘的办法在FPGA完成FIR升余弦滤波器。用VHDL编程并仿真,仿真成果如图5所示,试验仿真的成果与理论核算成果共同。

分布式算法在完成乘累加功用时,是经过将各输入数据的每一对应位发生的部分积预先进行相加构成相应的部分积,然后再对各个部分积累加构成终究成果的。它与传统算法完成乘累加的不同在于履行部分积运算的先后次序不同。与传统串行算法比较,分布式算法能够使用查找表的办法完成,能极大地削减硬件电路的规划,进步电路的履行速度。本文依据塑料光纤基带传输体系形式色散大的特色,选用分布式算法在FPGA上规划了升余弦滚降成型滤波器,完成了23阶FIR升余弦滚降滤波器的试验仿真,仿真成果与理论核算成果共同,验证了规划办法的正确性和高效性,规划进程不只克服了传统滤波器规划带来的许多坏处,一起也进步了体系的全体功能。