摘要 针对空空导弹高速图画信息处理板上呈现的电压压降较大,导致集成电路无法正常作业的问题,将电源完好性理论与PCB规划实例相结合,提出了处理高速印制电路板中电源完好性的办法,并将压降控制在0.5%以内,为目益杂乱的高速印制电路板规划供给了参阅。

跟着空空导弹高速图画信息处理板上DSP、FPGA等大规模数字集成电路的广泛应用,信号的频率也越来越高,图画信息处理板呈现电源压降较大的问题。频率较低时,可将电源和地作为一个完好的参阅平面,电源压降较小。但高频时,因为散布电感ESL的影响,电源、地平面相当于一个谐振腔,具有谐振特性。电源平面其实可看成是由较多电感和电容构成的网络,也可看作是一个共振腔,在必定频率下,这些电容和电感会发生谐振现象,然后影响电源层的阻抗。跟着频率的添加,电源阻抗是不断改变的,尤其是在并联谐振效应显着的时分,电源阻抗也随之显着,因而在瞬间电流经过期便会发生必定的电压降和电压摇摆。而大部分数字电路器材对电源动摇的要求在正常电压的±5%规模之内,因而形成数字电路器材不能正常作业。

本文将电源完好性理论和PCB规划实例相结合,在谐振、电源阻抗、防止重要信号线跨过平面层切割、直流压降等方面做了电源完好性方面的优化规划。

1 经过谐振剖析优化印制板布局

谐振形式核算剖析的是由PCB中电源和地的结构而或许引发的危险,包含叠层、板材以及地电切割等,意图是使印制电路板在所重视的频率规模内不发生谐振。

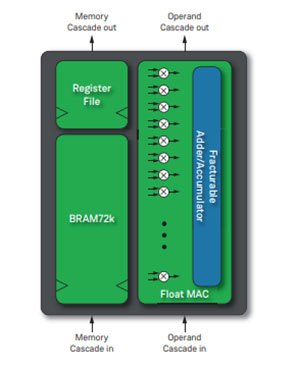

调查PCB的谐振形式下的电压散布,尽量防止将大电流IC放置在谐振方位或其邻近方位。图画信息处理板上电源和地的谐振图,如图1所示。

从图中可知,印制电路板右上角谐振较大,因而在印制电路板布局时大电流%&&&&&%器材尽量防止放置在印制板的右上角。

2 下降电源阻抗优化电路规划

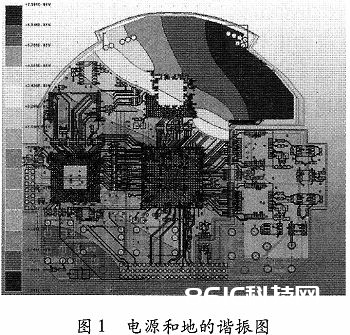

体系电源部分的好坏直接影响到体系的稳定性,乃至或许使得体系逻辑过错。一个低阻抗的电源散布体系是比较抱负的,至少在整个体系的作业频段内呈低阻抗,然后具有较小的压降。以图画处理板上的FPGA为例,供电电源为3.3 V,电压噪声限为5%,最大瞬间电流为0.15 A,则规划的最大电源阻抗如式(1)所示

![]()

对FPGA的3.3 V电源做电源阻抗仿真,图2所示为FPGA的3.3 V电源阻抗。

从图中可看到,在357 MHz、765 MHz处谐振频点阻抗较高,需求挑选适宜的去耦电容,以改进电源阻抗特性。这儿选取电容值为200 pF封装为0603的电容作为FPGA的去耦电容,因为它的特征曲线与电源阻抗曲线峰值频点共同,这样可将电源阻抗的峰值下降。

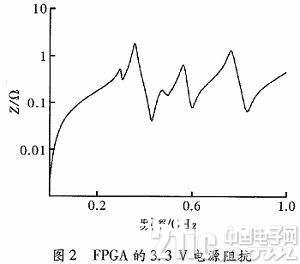

200 pF的去耦电容布局挑选在357 MHz谐振电压动摇最大的方位处,因在此处谐振比较显着,同样在728 MHz处谐振频点电源阻抗也较高,因而再加上两个62 pF电容后,电源阻抗如图3实线所示,虚线为开始没有加电容的电源阻抗。

从图3中可看到,电源阻抗有了较大改进,满意低于最大电源阻抗的要求。

3 防止高速信号线跨过平面层切割

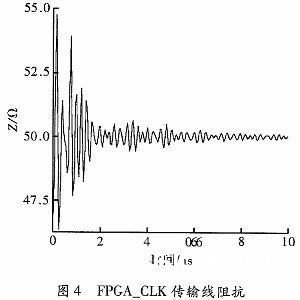

电源和地切割、线宽以及过孔等都会形成PCB传输线的阻抗不接连,引起电源平面和地平面回流途径不抱负,形成电源完好性问题。为得到更好的信号质量,可调理线宽和介质层的厚度以及电源和地的切割线来满意特性阻抗的要求。以FPGA_CLK为例,在当时PCB中,其的传输线阻抗如图4所示,阻抗在 43.5~54.7 Ω之间动摇,动摇过大。

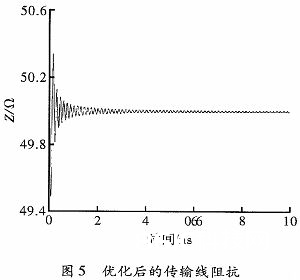

为改进传输线特性,对PCB层叠做优化。经过调理线宽,介质层的厚度以及不要跨平面层切割等来满意50 Ω特性阻抗的要求。优化后的传输线阻抗如图5所示。

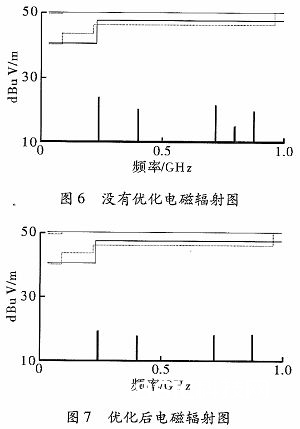

FPGA_CLK在层叠结构优化后,传输线阻抗在49.5~50.5 Ω之间,满意了阻抗匹配的要求。电源地网络和信号网络不是分裂的,而是紧紧耦合在一起的,所以电源地的噪声还会经过耦合影响信号线,或许辐射到外面,会发生EMI、EMC的问题。经过电磁辐射方面的比照。图6为没有优化时电磁辐射的波形,图7为优化后电磁辐射的波形。

经过图中比照,电磁辐射显着下降。

4 直流压降

在PCB规划中,因为平面层的切割,不抱负的电流途径和各种过孔信号线的散布,电源网络的直流供电经常受到影响。直流压降剖析可显现整个PCB上电流的流向、电路密度以及直流压降等特性。

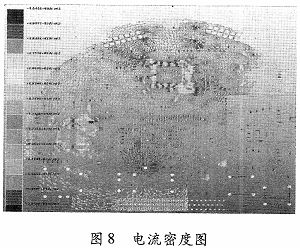

在发生3.3 V的芯片出口处设置电流源和电压源,在印制板右上方放置电流源的探针和电压源的探针,如图8所示。

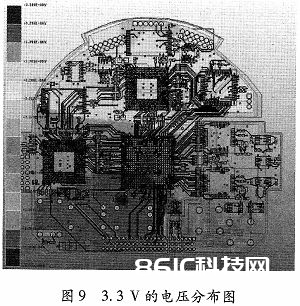

可看到深色区域表明电流密度过大,在两个DSP处赤色比较显着,可减小阻隔盘的巨细,使电流经过,在3.3 V供电处可经过增大过孔的尺度以及多打几个过孔的办法使电流在几个当地经过,以下降电流的密度。再对其做电压压降仿真,仿真图如图9所示。

最低电压为3.285 V,压降为0.5%,满意体系电压动摇在±10%要求。

5 结束语

电源完好性问题主要是因为去耦电容的规划不合理、回路影响严峻、多电源/地平面的切割欠好、地层规划不合理以及电流不均匀等问题引起的。经过电源完好性仿真,找到这些问题,然后经过以下办法处理电源完好性问题:(1)经过调整PCB叠层线宽、介质层的厚度满意特性阻抗的要求,调理叠层结构满意信号线回流途径短的准则,调整了电源/地平面的切割,防止了重要信号线跨切割的现象;(2)对印制板上用到的电源进行了电源阻抗剖析,经过参加%&&&&&%使其控制在方针阻抗之下;(3)在电流密度大的部分经过调整器材的方位,使电流从更宽的途径经过。