跟着路途上轿车数量的添加,咱们需求更多的技能来进一步削减交通事故。曩昔几年,根据雷达和摄像机的新体系功用的呈现使驾驭愈加安全。许多高档辅佐驾驭体系(ADAS)运用,如主动巡航操控、路途违背报警、交通讯号标志辨认等,已经成为车辆上十分便利的功用,但对车辆行为没有影响或影响很小。但是,现在这些技能开端在车辆操控中扮演积极主动的人物,如车道辅佐坚持(LKA)或主动紧迫刹车(AEB)等,以协助完结削减交通事故的既定方针。这带来的应战是,当体系呈现毛病时,有必要保证体系不会对车辆和环境形成更大的危害。

本文以单前端摄像机体系为例,对其进行深入剖析,介绍它怎么经过运用Altera Cyclone V SoC确认要害数据流.在现有的确诊机制下,怎么找到毛病;并供给一些确诊实例,经过灵敏的可编程FPGA,在体系级完结确诊。与运用通用微处理器、数字信号处理(DSP)和其他渠道比较,在某些情况下,针对实践运用运用定制确诊办法能够进步运用功用。

ADAS运用中的FPGA

上文说到的许多运用都有相对较高的核算需求,需求从雷达或视频图画中提取特征信号,确认方针及其踪影。这一般要求高功用多核CPU体系结构。这些CPU能够灵敏地对特别事情从头编程,但缺陷是功率较低,因为有些功用并非必需或很少运用。

功耗是需求点重视的另一要素。许多体系坐落后视镜前面的挡风玻璃下面,直接暴露在阳光下,或坐落散热器前保险杠中,因而无法高效地散热。当运用高频运转的多核通用CPU体系结构时,很难满意功用和功耗要求。运用FPGA可一起处理这些问题。FPGA的功耗一般比规范逻辑高,但与通用核算体系结构比较,高效的定制完结某一算法实践上下降了功耗。FPGA的另一长处是,当完结流处理算法后,能够防止在内部和外部存储器之间传送数据。若运用外部DDR存储器进行数据处理,实践功耗会十分大。

就功用而言,流处理也下降了某些运用中遇到外部存储器带宽问题的风险。FPGA内涵的可编程特性带来了通用核算体系结构所具有的某些优势。它乃至支撑系列产品的在现场更新,完结在体系编程。在某些情况下,根据FPGA开发,要比根据CPU的高功用芯片体系结构简单得多。因为SoC越来越多,因而,FPGA能够很好地结合这两种体系结构,例如Altera Cyclone V SoC系列,它在一个芯片上集成了通用CPU体系和FPGA架构。Cyclone V SoC完结了两个ARM Cortex—A9 CPU,支撑通用微操控器和处理器常用的许多外设。

功用安全

与现在市场上的其他处理方案比较,FPGA愈加简单满意运用的功用安全需求。ADAS需求满意特其他功用安全要求。2011年,发布了载重3.5吨以上的ISO26262规范,以下降体系呈现毛病后形成风险状况的风险。这一规范要求完结紧密的规划进程,在运用履行进程中勘探随机硬件毛病,以削减体系性毛病。它涉及到一个体系及多个体系的剖析和开发,列出了体系中运用的每一硬件组件的攻略(包含这些硬件组件上运转的软件),设定了产品整个安全生命周期中的要求。

运用开发人员界说了专门的安全方针,针对每一方针分配了相应的轿车安全完整性等级(ASIL)。关于运用中最高档其他ASIL,一般界说了每一组件从开发直至作业到寿数终了时应满意的要求。图1显现了ASlL现在的规模,来自ADAS需求恪守的客户需求。

ASIL-B是市场上的最低等级,而某些运用则要求选用ASIL-D以支撑某些功用。越来越多的ASIL有更严厉的要求。在某些具体完结中,组件的通用ASIL或许条目(体系)等级都会带来不必要的复杂度,对开发本钱和进展有影响。主张应具体地了解运用需求。这一般经过剖析体系概念,并从中得出安全概念和要求来完结。还能够把运用分红几种不同的过程,具有不同的ASIL,更简单完结,功率更高。

ADAS单前端摄像机运用体系概念

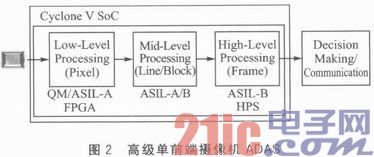

本文举例的前端摄像机运用运用了ADAS中常见的一个图画传感器。图2显现了体系的全体框图。

一个图画传感器衔接至图画处理器,即Altera Cyclone V SoC。信号处理链和数据流被分红4部分:

◆ 经过把图画变换成更有用的表明,在像素级上进行底层处理。

◆ 对行图画或许块图画进行中间级处理,运用相应的算法,例如Sobcl滤波器或许Canny边缘勘探算法等,提取出边缘等特征。

◆ 进行高档处理,提取出每一帧的数据,勘探方针并分类。

◆ 盯梢辨认出的方针,决定在风险环境下是否需求采纳办法,例如刹车或许换挡电子操控单元(ECU)等会要求与微操控器进行通讯。

在FPGA上能够十分高效地完结底层和中间级处理,但用户也能够在Cyclone V SoC硬核处理器体系(HPS)的Cortex—A9处理器等CPU上完结某些中间级处理。高档处理主要是操控代码,能够映射到HPS中的一个或两个Cortex—A9上。处理链的终究一步是方针盯梢和判定,能够在外部微操控器上完结这一步。

在整个处理进程中,每一步将输入数据进行简化得到更有意义的数据,数据削减意味着进步了安全临界。因而,底层完结能够分红质量办理(QM)或底层ASIL(如ASIL-A)。这样的原因是,一个像素期间引进的毛病对后续算法功用的影响很小,能够疏忽。在这个比如中,假定中间级处理契合ASIL-A或许ASIL-B,辨认方针并进行分类的高档处理应契合ASIL-B。对方针进行分类后,生成方针表,供给给微操控器,进行方针盯梢和判定。这是信号链最要害的部分,咱们假定它应该契合ASIL-D,这对轿车的行力有直接影响。

组件运用功用

图3显现了单前端摄像机体系实例的整体结构图。由一个外部电源办理电路为Cyclone V SoC供给电源。当供电电压不在额外作业规模内时,独自的电压监控功用会发生复位。外部非易失存储器衔接至四路串行外设(quad SPI)模块,用于体系启动进程中装入运用程序并装备FP GA。履行运用代码,存储数据和图画帧时,咱们运用DDR存储器。经过SPI衔接外部微操控器,进行方针勘探和终究判定,经过CAN总线接口与轿车根底结构的其他部分进行通讯。