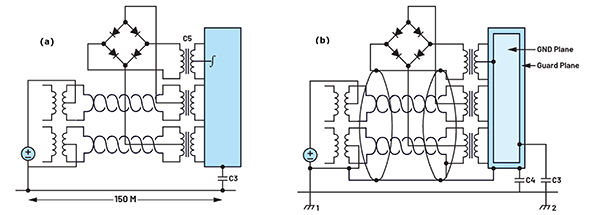

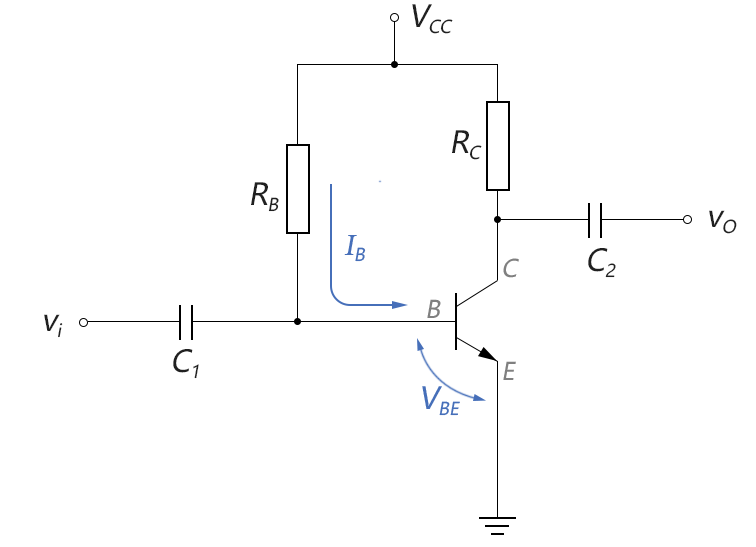

BJT共射级电路扩大器是比较常用的一种扩大电路,不同于前面的共基级扩大器单一的电路方式,共射级扩大器的规划比较灵敏,历史上人们从前规划出过许多各式各样的共射级扩大器。最常用的是以下三种方式的共射扩大电路(见下图3-06.01)。一般只需把握了这三种电路的共通剖析办法,那今后再遇到其他比较偏门的共射电路时,咱们也能够依照咱们已把握的共通办法,剖分出其根本电路特性。

图 3-6.01

1. 固定偏置

固定偏置(fixed-bias configuration)是最简略的共射扩大电路结构,咱们现以npn型晶体管为例对齐进行直流剖析。

(1) 输入静态作业点

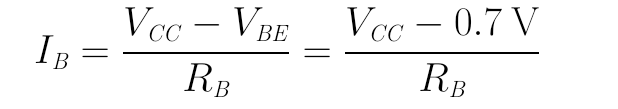

咱们将固定偏置的共射扩大电路重画于下,在直流剖析(静态剖析)时,可将动态输入电压vi视为0。

图 3-6.02

关于输入端回路,BJT的发射结正偏,咱们选用简化剖析模型,假定VBE固定为0.7V。因而在输入回路可得:

上式的IB即为输入端的静态作业电流,在上式中咱们能够取适宜得RB,而得到一个比较合理得IB值(一般为几个微安级)。

(2) 输出静态作业点

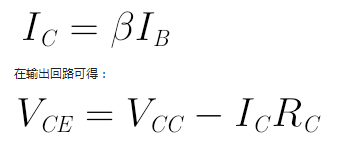

输出静态作业点,即为求VCE和IC,咱们将输出回路的电压电流联系画于下图:

图 3-6.03

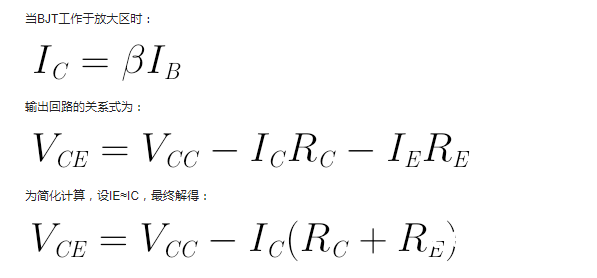

当BJT作业于正常的扩大区时:

上两式中的VCE和IC即为输出的静态作业点。

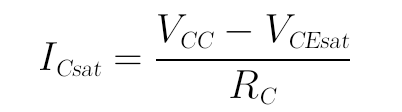

(3) 饱满条件

在共射电路中的饱满条件与共基电路稍有不同,在共基电路中,VCE《0会进入饱满,而在共射电路中,只需VCE《VCEsat(一般咱们常近似取为0.3V),晶体管就会进入饱满。因而,咱们能够算出此刻的集电极饱满电流ICsat,

当共射电路的进入饱满时,输入端IB的持续增大不会使输出电流IC持续增大,尽管不会像共基电路那样损坏晶体管,但会使基极电流IB与射极电流IC之间的扩大倍数小于本来的β参数。

(4) 固定偏置的缺陷

固定偏置的长处是:结构简略、概念明晰。可是咱们一般很少将固定偏置电路直接应用于实践规划,原因在于固定偏置电路有一个丧命的缺陷:便是作业点不稳。

前面从前说过,由于半导体器材加工工艺的约束,一般参数都会违背规范值,比方对某个BJT来说,扩大系数β在50~200规模内都算正常,整整差了4倍。那么依据上式:

相同的电路,输出静态电流IC就会差整整4倍,输出静态电压VCE也会有较大规模的改变,由此带来的电路功耗、扩大倍数等一系列功能也会跟着改变,这样不安稳的功能是无法在实践产品中运用的。

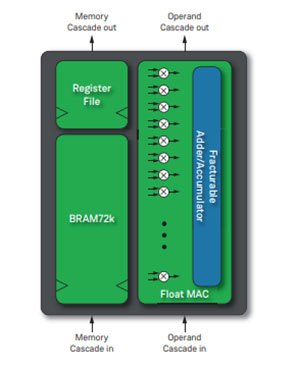

2. 改进的固定偏置

(1) 负反应的效果

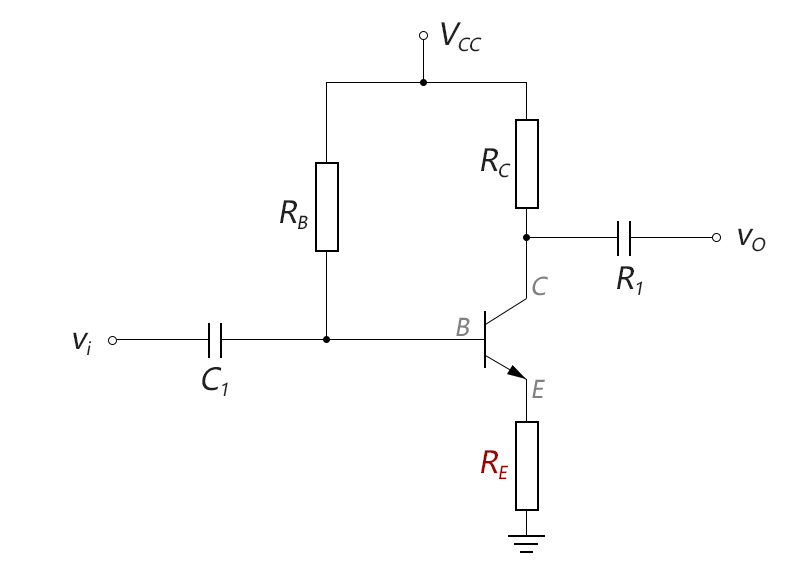

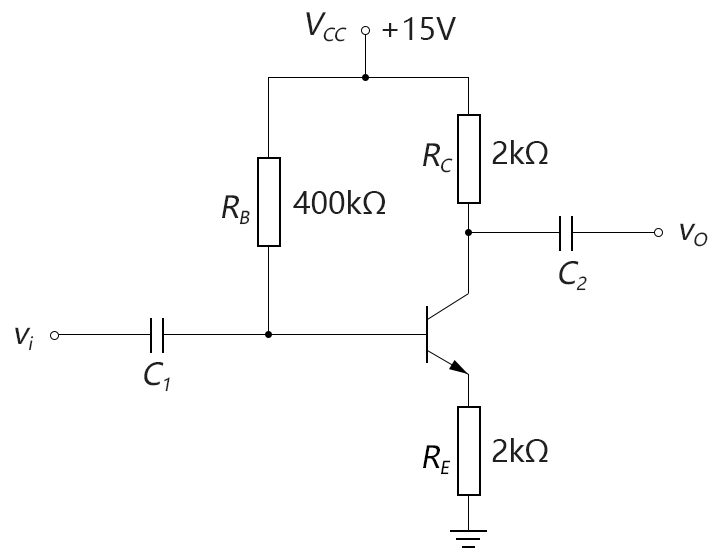

在固定偏置的发射极添加一个射极电阻RE,能够大大进步电路的安稳性,如下图所示,这种方式的电路也能够称为射极偏置(emitter-bias ConfiguraTIon):

图 3-6.04

这种规划称为“负反应”规划,负反应规划是一个很巨大的论题,这儿你能够先简略将其了解为:负反应结构的电路自身有一种安稳效果,当某种非正常要素(比方β值偏移,温度影响等等)导致电路作业点偏移时,负反应结构会迫使电路作业点回向正常值方向移动,然后减小偏移值,进步安稳性。

咱们这儿先大略定性地看一下射极电阻RE对进步电路安稳性的效果:

(1)当扩大系数β增大导致IC增大时,流过RE的电流IE也会增大,由此会导致E点的的电压VE升高。

(2)当VE升高,由于VBE坚持固定值0.7V不变,因而成果导致B点电压VB升高。

(3)VB升高,但VCC不变,由此导致RB两头的压降减小,然后导致输入电流IB减小。

(4)IB的减小终究会导致IC的减小,按捺了前面因β增大导致IC增大的效应,因而进步了电路的安稳性。

当然,假如你若要深究的话,又会发现:IC的减小会导致IE的减小,再导致VE的减小和VB的减小,然后又使得IB增大……那么,终究哪个对终究成果的影响力更大些?这个就需要下面的定量剖析了。

(2) 静态作业点剖析

图 3-6.05

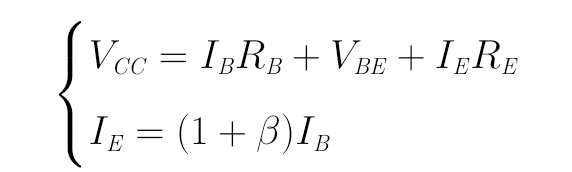

● 先看输入回路:

输入回路的联系式为:

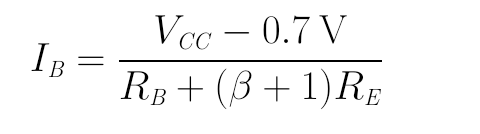

解得:

● 再看输出回路:

● 关于简化运算的阐明:

这儿你或许还有一点小疑问,为什么在输入回路中,不把(1+β)简化成≈β,不去掉那个1?而在输出回路中,却做了IE≈IC¬的简化,去掉了那个1呢。其实理由很简略:输入回路的核算式中,即使藏着那个1,核算起来也不费事,所以就放着了。而在输出回路的核算式中,藏着那个1算起来略微有点费事了,所以就把它给去掉了。

听着是不是很随意呢?其实这便是工程中模仿电路的魅惑点地点。由于实践的模仿电路要面对许多的不确定参数的影响(比方,惯例运用的电阻都是5%的差错等级的;BJT等半导体器材的参数乃至会有50%以上的差错;受温度影响,许多参数也会偏)。你辛辛苦苦算出来的准确解,仅一个5%的电阻阻值差错就能够把成果给带偏。所以,太准确的核算有时并不是很必要,许多核算都能够作简化。那么,终究对哪些部分能够做简化,哪些部分不作简化呢?这个在很大程度上取决于规划者自己的经历(或者说直觉)。

所以,有时你能够看到在一些不同的模电教材上,关于相同方式的电路,不同的作者会给出略微有点不同的公式,这个是由于他们各自取的简化点不同。可是,剖析原理必定都是相同的,并且他们的成果也都是可用的。这个跟着你自己经历的添加,就会了解他们各自的做法了。

事例3-6-1: 鄙人图中,核算当β=50和β=200时的IB, IC, VCE,并进行比较。

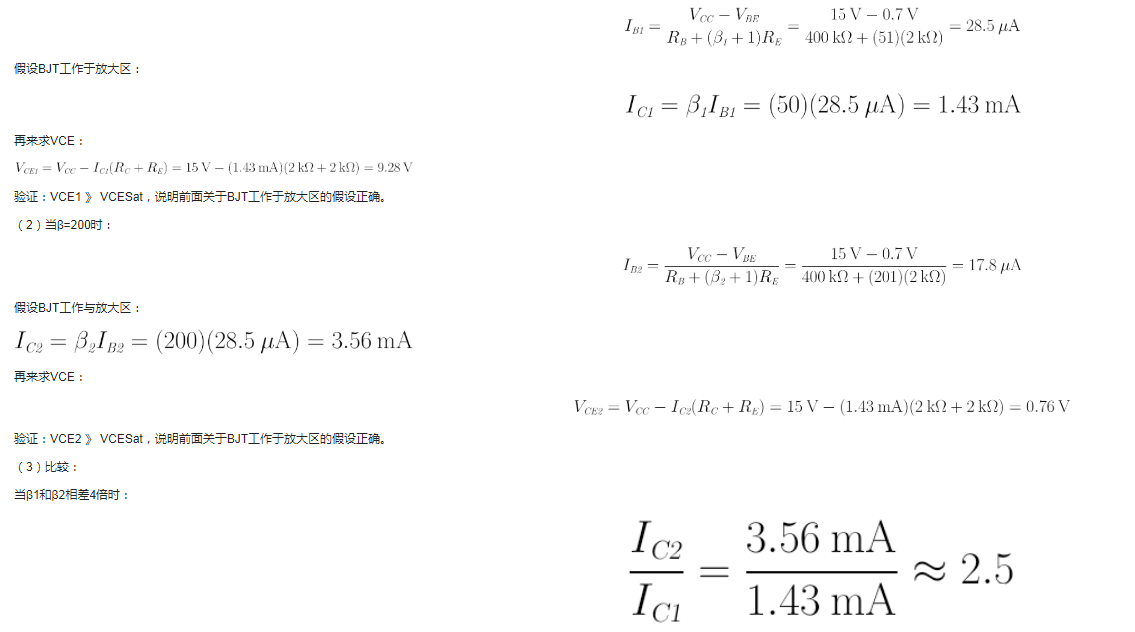

解: (1)当β=50时:

IC1和IC2只相差2.5倍,阐明反应电阻RE的确改进了电路的安稳性。

别的,当β=200时,VCE2仅比饱满阈值VCESat (0.7V)大一点点,已处于扩大区的边际,还能够牵强作业。若是没有反应电阻RE,BJT会早早地就进入饱满区,而不能起正常扩大效果了。

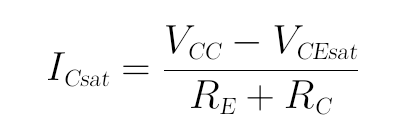

(3) 饱满条件

当VCE《VCESat时,晶体管进入饱满区。因而,咱们能够算出此刻的集电极饱满电流ICsat,

当IC》ICsat时,晶体管进入饱满。