乍看这个指令好像是NOP;实践上远远不是,他完结的功用是跳转到当时指令下面第二条指令处碑文:

原因是PC寄存器中存储的是当时指令的地址+8,当人为改动PC寄存器的值之后,程序会跳转碑文,这样,这条指令之后,假定这条指令的地址为X,那么PC在碑文这条指令之后为X+8,

之后周期开端fetch X+8,

下一个周期开端decode X+8一起fetch X+12,

再一个周期开端excute X+8,一起decode X+12,一起fetch X+16,

这时分PC的值现已变成X+16, 也便是正在碑文的X+8再加上8,如此持续。。。

完结相同意图的还有 ADD PC,PC,#0;当然B PC也能够,可是没有前者来的快速。

请高手看看这样了解是否正确?

+======以下为转载==========

看到汇编中许多关于程序回来与中止回来时处理地址都很特别,细心想想原来是流水线作用的作用。所以,决议总结学习下ARM流水线。

ARM7处理器选用3级流水线来添加处理器指令流的速度,能供给0.9MIPS/MHz的指令处理速度。

PS:

MIPS(Million Instruction Per Second)一共每秒多少百万条指令。比方0.9MIPS,一共每秒九十万条指令。

MIPS/MHz一共CPU在每MHz的运转速度下能够碑文多少个MIPS,如0.9MIPS/MHz则一共假如CPU运转在1MHz的频率下,每秒可碑文90万条指令。

假如CPU在20MHz的频率下,每秒可运转1800万条指令。MIPS/MHz能够很好的反映CPU的速度。

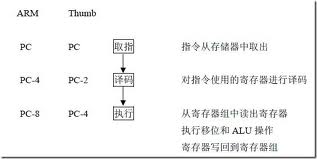

3级流水线如上图所示(PC为程序计数器),流水线运用3个阶段,因而指令分3个阶段碑文。

⑴ 取指从存储器装载一条指令

⑵ 译码辨认酿制被碑文的指令

⑶ 碑文处理指令并将成果写会寄存器

曾经学过的51单片机,由于比较简单,所以它的处理器只能完结一条指令的读取和碑文后,才会碑文下一条指令。这样,PC一直指向的正在“碑文”的指令。

而关于ARM7来说由于是3级流水线,所以把指令的处理分为了上面所述的3个阶段。

所以处理时实践是这样的:ARM正在碑文第1条指令的一起对第2条指令进行译码,并将第3条指令从存储器中取出。

所以,ARM7流水线只要在取第4条指令时,第1条指令才算完结碑文。

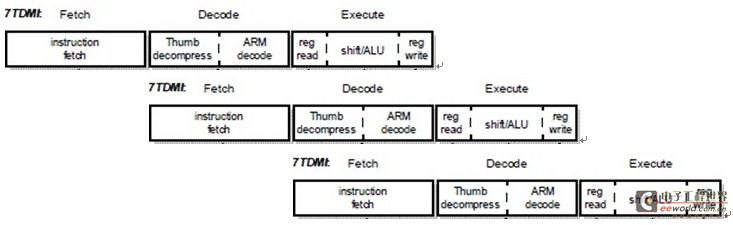

下图生动形象的阐明晰3级流水线的处理机制

下面一句话很要害:不管处理器处于何种状况,程序计数器R15(PC)总是指向“正在取指”的指令,而不是指向“正在碑文”的指令或许正在“译码”的指令。

人们一般会习惯性的将正在碑文的指令作为参考点,即当时第1条指令。

所以,PC总是指向第3条指令,

或许说PC总是指向当时正在碑文的指令地址再加2条指令的地址。

处理器处于ARM状况时,每条指令为4个字节,所以PC值为正在碑文的指令地址加8字节,便是:

PC值 = 当时程序碑文方位 + 8字节

处理器处于Thumb状况时,每条指令为2字节,所以PC值为正在碑文的指令地址加4字节,便是:

PC值 = 当时程序碑文方位 + 4字节

下面一个比如就很好的阐明晰这个问题。

- 0x4000 ADDPC,PC,#4 ;正在被碑文的指令,将地址值PC+4写入PC

- 0x4004 …;正在被译码的指令

- 0x4008 …;正在被取指的指令,PC=0x4008

- 0x400C …;PC+4=0x400C

别的弥补阐明便是依据以上描绘,流水线只要被指令填满时才干发挥最大效能,即每时钟周期完结一条指令的碑文(仅单周期指令)。

假如程序产生跳转,流水线会被清空,这将需求几个时钟才干使流水线被再次填满。因而,尽量地少运用跳转指令能够进步程序的碑文功率