摘要:文章介绍了YCbCr颜色空间和RGB颜色空间之间的转化的办法,完成了不同规划以及不同数据结构的YCbCr到RGB的快速硬件转化。选用数据重摆放和数据别离等办法,不只支撑QCIF到HDTV多种分辩率的视频转化,而且支撑YCbCr444、YCbCr422和YCbCr420等多种打包或平面YCbCr格局。本规划方案已用VerilogHDL言语完成,并在FPGA渠道验证经过,转化后的RGB视频可直接输出到显现器显现,并能完成视频操控,存储,回放等功用。

0 导言

颜色空间是经过数值的办法来描绘颜色,在数字电视和核算机范畴最常用到的为RGB(Red,Green,Blue)颜色空间和YCbCr(Luminance,

Chroma Blue,Chroma Red)颜色空间。RGB是最常见的颜色空间,经过红、绿、蓝三种基色彼此叠加然后发生其它颜色。因为其设备的独立性,它被广泛运用于核算机图形、成像体系和彩色电视之中,如现在遍及的核算机显现器用的VGA接口所需求的数据类型便是RGB。YCbCr颜色空间则是灰度和色差的叠加,这种颜色空间因易于紧缩和处理,广泛运用于播送、电视体系和图画处理。

因为不同颜色空间在视频设备的运用,使颜色空间的彼此转化成为必需。跟着核算机、互联网和多媒体技能的飞速发展,对颜色空间转化的要求也越来越高,这更突显出颜色空间转化的重要性。

颜色空间转化的首要意图是令一切的输入数据在进行运算和处理或许显现前都依据相同的颜色空间。关于YCbCr转RGB而言,首要的问题在于两个方面,一个是视频格局的规划,也便是咱们所说的分辩率,高的分辩率意味着需求更多的硬件资源和更快速的核算进程;另一个是YCbCr自身具有许多不同的格局,而现在的转化器一般都是依据其间一种固定的格局,关于其他格局的YCbCr数据并不支撑,所以为了支撑多种YCbCr数据格局,有必要把不同的YCbCr数据一致到一种格局来完成转化。

1 YCbCr与RGB颜色空间

1.1 YCbCr颜色空间

在常见的消费类视频产品中,常用的颜色空间是YCbCr。人眼对视频的Y重量更灵敏,因而能够在采样时恰当削减Cb和Cr重量然后完成视频的紧缩,因而YCbCr格局有三种不同格局:4:2:0、4:2:2和4:4:4。这三种格局又分为打包办法和平面办法两大类,差异在于不同像素的Cb和Cr坐落Y重量之间仍是之后。

移动视频设备是以YCbCr4:2:0的办法记载,跟着H.264视频解码规范的推行和杰出的紧缩比率,YCbCr4:2:0运用越来越多。4:2:0表明每4个像素有4个亮度重量,2个颜色重量,以8个像素点为例,数据格局如下:

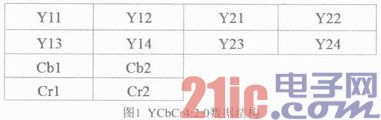

4:2:2表明每4个像素有4个亮度重量,4个颜色重量,是数字电视、有线视频传输设备的最常用格局。以8个像素点为例,数据格局如下:

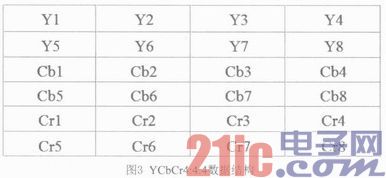

4:4:4是最接近RGB的选用格局,每一个像素都有三个重量,运用于需求高质量视频收集的专业视频产品。以8个像素点为例,数据格局如下:

由这三种数据格局剖析可知,他们仅在采样点和采样点散布上有所不同,Y重量是每个像素都需求采样的,而Cr、Cb重量能够依据对数据格局和视频质量要求的不同而自主挑选。这三种数据格局因为摆放次序不同又叮分为不同的类型,所以完成可变规划的多格局转化首要要把不同的YCbCr格局转化成一个易于一致的格局,三个数据格局的比照如表1所示。

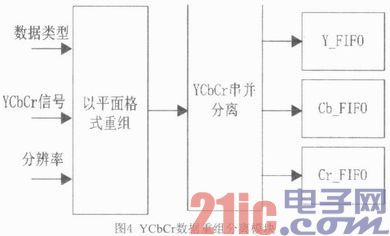

综上所述,YCbCr的采样格局将直接影响到图画数据存取空间巨细,以及读取和存储图画的速率。要完成YCbCr4:2:0,YCbCr4:2:2与YCbCr4:4:4三种格局都能够成功地转化为RGB信号,就有必要把这三种格局转化为同一种格局,然后再转化为RGB信号的格局。为最大极限保存各种图画质量,选用YCbCr4:4:4平面格局为一致格局。经过逻辑摆放电路把不同格局的YCbCr序列转化成YCbCr4:4:4序列,并把YCbCr信号别离存在三个不同的FIFO中,再由YCbCr—RGB转化模块读取三个并行FIFO中的序列进行转化。完成逻辑结构如图4所示。

1.2 YCrCb到RGB颜色空间改换原理

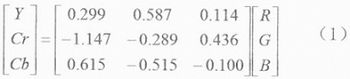

YCrCb颜色空间与RGB颜色空间的对应联系如下:

人眼能够分辩的颜色数量远小于256,所以一般都运用8bit的位宽来描绘颜色,其间R、G、B、Y、Cr、Cb都为0~255的整数。为最大程度削减改换进程发生的差错,转化成公式(2)核算。

R=1.164(Y-16)+1.596(Cr-128)

G=1.164(Y-16)-0.813(Cr-128)-0.392(Cb-128) (2)

B=1.164(Y-16)+2.017(Cr-128)

注意到等式中包括的7个因式,其间有3个是相同的,该因式只需核算1次,送到相应的加法器进行之后的运算。

因为在硬件完成时,核算进程不支撑浮点核算,所以要把核算进程进行取整,如式(3)。

R=1.164Y+1.596Cr-223

G=1.164Y-0.813Cr-0.392Cb-173 (3)

B=1.164Y+2.017Cb-277

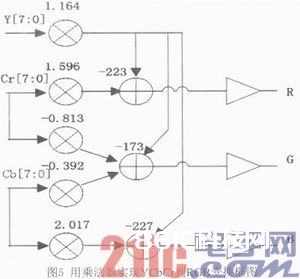

硬件完成框图如图5所示。

2 YCrCb到RGB改换的FPGA完成

2.1 硬件完成办法和优化

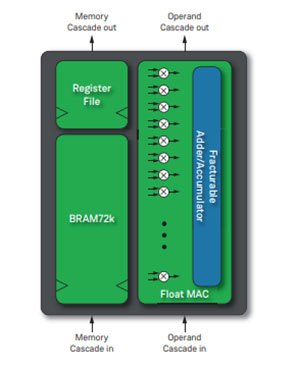

依据视频格局转化的特色和需求,本文选用FPGA硬件体系来完成多种视频格局的YCbCr格局转化和RGB显现。在FPGA规划中由颜色空间YCrCb到RGB的转化有三种办法。第一种是运用嵌入式处理器,选用软件的办法完成转化,这样做一来硬件消耗大,另一方面在FPGA上处理器的运算速度达不到大数据实时显现的要求。第二种是用Verilog代码来表达转化公式,这种办法需用到5个乘法器,而且YCbCr到RGB的转化均是经过很多的浮点运算来完成的,每个像素点都要进行一次核算,所以假如是高清视频,用100MHz时钟每帧图画的转化将为此消耗近54ms的时刻,而假如要到达30f/m的显现要求,这个时刻不能超过33ms。第三种办法是运用查找表法,把乘法成果用查找表的办法获得。这种办法不只减小了浮点运算的差错,也使得核算速度比前两种办法快了一个数量级,而且YCbCr的值都在0~255之间,所以每个查找表项目都只要256项,并不会过多地占用硬件资源。

查找表中预存的数值是各个因式的值,为进步的炔考扑憔度,又不占用过多的RAM资源,归纳考虑可将各个因式数值扩展2倍进行存储,RAM的数据宽度可设定为9位。由查找表读出的数值经过加减运算后再右移一位的简略运算就能够把数值缩小到原先的位数,再经过钳位运算束缚在0~255之间,核算公式如下:

R=(2.328Y+3.192Cr-446)>>1

G=(2.328Y-1.626Cr-0.784Cb+346)>>1 (4)

B=(2.328Y+4.034Cr-554)>>1

用查表法完成转化中的乘法核算,在硬件完成YCbCr转RGB的实时视频显现有着重要的含义,表2是YCbCr转RGB不同办法的试验数据,本文用于验证该模块的器材是Altera公司的Cvclone2-EP2C70F896C6。占用的归纳东西为Design Compiler,经过时序束缚最快时钟频率能够到达102MHZ。

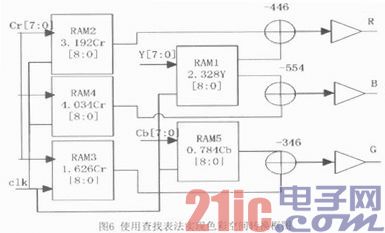

浮点乘法是影响转化功率的要害,而运用查找表法避免了浮点乘法的运算,使转化功率进步了1个数量级。要支撑高清格局30f/s实时转化,转化时刻要低于33ms,加之数据存储的延时,用查找表结构转化模块是必要的。用查找表法完成的模块结构如图6所示。

经过结构RAM1~RAM5五个查找表映射单元,把输入的信号别离按式(4)的办法核算出RGB相应的成果,直接送给显现缓存寄存器。本文用的测验渠道是Altera DE2-70开发板,体系结构如图7所示,内部首要分为数据重组模块、查找表模块、操控模块和显现模块。数据重组模块能经过设置不同的分辩率和YCbCr格局把YCbCr数据别离提取贮存在三个FIFO中,查找表模块担任经过FIFO中Y、Cr、Cb的值输出浮点乘法的运算成果,再加减运算后输出转化后RGB24位的值。操控模块担任操控码流的播映、暂停和存储回放等扩展功用。显现模块担任驱动码流到VGA显现。

2.2 体系验证

2.2.1 数据验证

体系验证包括两个部分,首要要验证不同格局的YCbCr转化为YCbCr444的码流是正确的,这部分能够先用ModelSim把转化逻辑进行仿真,别离把Y、Cb、Cr三个数据按次序存在对应的三个FIFO中。

之后经过MATLAB的数据比较指令strcmp,将FIFO中的YCbCr444数据与MATLAB转化的数据进行比较。别离运用QCIF、CIF、HDTV三种分辩率进行随机一帧码流的验证,返回值都为1,证明转化体系牢靠。

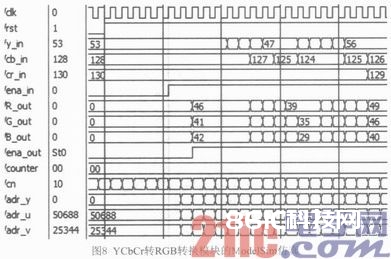

体系全体经过ModelSim仿真成果如图8所示。

在图8中,adr_y、adr_u、adr_v,为数据重组后的YCbCr地址,y_in、Cb_in、cr_in别离为待转化的数据,R_out、G_out、B_out为转化后的输出成果。ena_in和ena_out为输入使能和输出使能信号,这两个信号能够操控视频转化的发动和中止,在2个时钟周期之后就能够有显现成果呈现,这只是需求6 μs,人眼底子感觉不到推迟,能够用在对转化速度要求较高的体系上。像素计数器为cn,在一帧图画彻底转化后帧计数器counter会计数一次,经过这个能够提取完好的一帧图画进行查验。

2.2.2 FPGA体系验证

将整个体系烧录到FPGA中进行硬件验证,输入的视频编码经过SD卡读入体系,进行YCbCr格局的重组,这儿选用了三种格局三种分辩率的视频编码,如图9所示别离为YCbCr420格局OCIF分辩率、YCbCr422格局CIF分辩率和YCbCr444采样格局HDTV分辩率经过YCbCr-RGB转化后某一帧图画的显现成果。显现成果表明该办法能够正确完成30f/s的不同规划和不同格局的YCbCr-RGB实时转化。

3 结语

本文依据FPGA构建硬件渠道,完成不同分辩率和不同格局的YCbCr视频数据的存储、处理和VGA输出,具有结构紧凑、功用完善、装备灵敏、体系安稳的特色。视频格局转化办法适用于大部分视频图画处理的通用渠道,满意视频图画高精度快速实甲换和显现的要求。可运用于多种制式视频采样数据与输出接口数据格局不匹配的场合,具有必定的运用价值。