CAN总线是当时最盛行的工业现场总线之一,PCI则是一种运用遍及的高速同步总线,具有32 bit带宽,时钟频率为0~33 MHz,最大传输速率可达132 Mbit·s-1,广泛运用于数字图像、语音及数据实时收集与处理等范畴。本文运用PCI9054接口芯片、FPGA、微处理器与CAN收发器完结CAN总线与PCI总线问的快速数据交流。

1 总体规划

PCI_CAN数据转化体系用于完结上位机的操控信息与CAN总线上各节点间的状况、数据信息交流功用。体系经过PCI接口芯片与FPGA将上位机宣布的操控信息发送给微处理器,由微处理器操控CAN收发器对CAN总线各节点进行查询;一起CAN总线节点的状况、数据信息上传给CAN收发器,由微处理器操控将其送入FPGA中缓存,再由PCI接口芯片上传至上位机做进一步数据处理、存储操作。

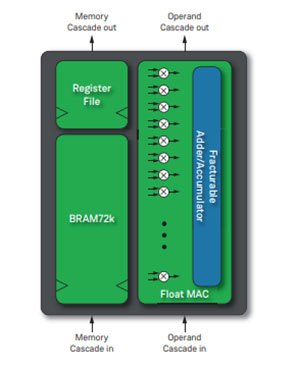

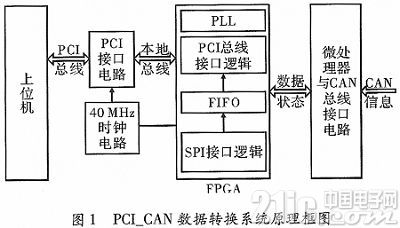

PCI_CAN数据转化体系主要由PCI接口模块、FPGA逻辑模块、微处理器与CAN收发器模块及时钟电路4部分组成,其原理框图如图1所示。

PCI接口模块完结PCI总线与本地总线间的数据交流。FPGA完结对PCI接口芯片和微处理器的逻辑操控、总线裁定等使命,且与微处理器之间经过SPI方法进行数据交流。因为CAN节点以“帧”为单位上传数据,体系运用FPGA内嵌的内存块生成FIFO,进行数据缓存;一起上位机的操控信号只要一个长字,无需FIFO缓存。微处理器与CAN收发器模块接纳来自上位机的操控信号,完结对各CAN节点的查询、监督功用;一起操控CAN收发器,将CAN节点上传的数据打包、发送至FPGA。时钟电路由40 MHz和25 MHz军等第晶振组成,供给PCI接口电路部分总线作业时钟、FPGA主时钟、微处理器作业时钟。

2 模块规划

2.1 PCI接口模块规划

PCI9054是美国PIX公司出产的PCI桥接芯片,契合PCI总线标准,支撑主形式、从形式及DMA传输方法,广泛运用于嵌入式体系中。

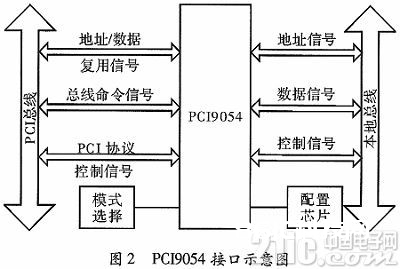

PCI9054在本模块中的衔接框图如图2所示,其间PCI总线信号与PCI衔接器相连,包含地址/数据复用信号AD[31:0],总线指令信号C/BE[3:0],PCI协议操控信号PAR、FRA ME#、IRDY#、TRDY#、STOP#、PERR#、SERR#、IDSEL;EEPR()M接口信号直接与装备芯片衔接,包含EESK、EEDO/EEDI、EECS;本地总线信号与FPGA相连,包含地址总线LA[13:2],数据总线LD[31:0],LBE[3:0]#字节使能信号及操控信号LW/R#、BLAST#、READY#、ADS#。

设置PCI9054芯片的MODE[1:0]管脚,挑选作业形式为C形式;装备PCI9054相关寄存器,设置数据传输方法为DMA和PCI从设备方法协同操作。DMA传输是在PCI9054操控下,完结PCI端存储器和LOCAL端存储器间的大数据量传输。

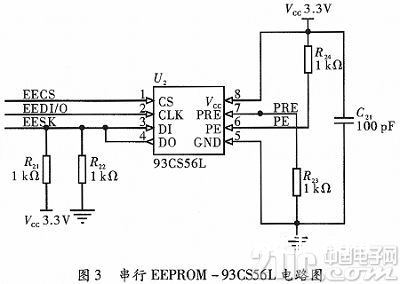

本文选用串行EEPROM芯片93CS56L。在体系复位后,完结对PCI内部寄存器的初始化装备,包含设备标识、状况寄存器、操控寄存器、中止寄存器、本地总线上设备的地址、空间等信息。因为需要对串行EEPROM进行写操作,芯片须处于可编程且非维护状况,如图3所示。

2.2 FPGA逻辑模块规划

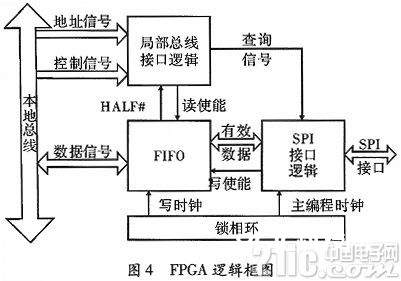

FPGA芯片选用Altera公司的Cyclone IV系列工业级芯片。EP4CE10E22I7,该芯片用户可用管脚为92个,逻辑单元巨细为10 320 bit,分布式RAM总容量144 kbit,嵌入式块状存储器SRAM容量270kbit,可满意规划需求;选用Verilog HDL言语进行逻辑规划,FPGA逻辑功用框图如图4所示。

上位机需查询CAN节点状况、数据信息时,PCI9054数据传输方法为PCI从设备。PCI总线主设备,即上位机,拜访PCI9054的本地空间,向内存空间写一个长字的操控数据。本地总线将该数据读出并发送至FPGA,经过微处理器对CAN总线某节点进行查询。

CAN总线节点的数据上传功用经过PCI9054的DMA形式完结。PCI9054集成了两个彼此独立的DMA通道,每个通道都支撑块DMA和涣散/会集DMA传输。块DMA传输由上位机供给PCI总线和本地总线的开端地址、传输方向及传输字节数。在块DMA传输中,作为PCI总线和本地总线的主控设备,PCI9054使能本地总线的中止等候状况;FIFO半满信号HALF#有用时,FPGA拉低本地总线的LINT#信号,发生中止;PC呼应中止,在中止处理子程序中调用DMA程序,建议DMA传输;传输完结时,PCI9054设定DMA“传输完毕位”完毕DMA操作。

SPI接口逻辑接纳、处理来自微处理器的帧数据,发生FIFO写使能信号,并将去掉帧头后的有用数据存入FIFO;锁相环PLL用于发生FIFO写时钟与SPI接口逻辑主时钟。

体系规划一次DMA传输数据为100 Byte,因而运用FPGA的内嵌内存块生成FIFO。该FIFO深度为128 Byte,宽度为8 bit;且只缓存CAN节点的上传数据,而不存储上位机的查询操控数据。本地总线接口逻辑单元依据操控信号、地址信号及半满信号HALF#,发生FIFO读使能,将有用数据传输至PCI9054;其间本地总线端时钟信号LCLK作为FIFO读时钟。

2.3 微处理器与CAN收发器模块规划

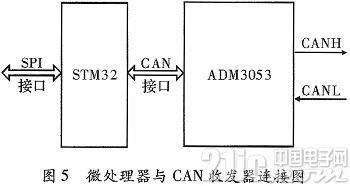

该部分电路由ARM公司的微处理器STM32F105、阻隔型CAN收发器ADM3053组成,如图5所示。

微处理器STM32F105集成CAN协议接口与SPI协议接口,可直接与CAN收发器衔接,并将接纳到的CAN数据、状况信息参加帧头,经过SPI口打包、发送到FPGA。

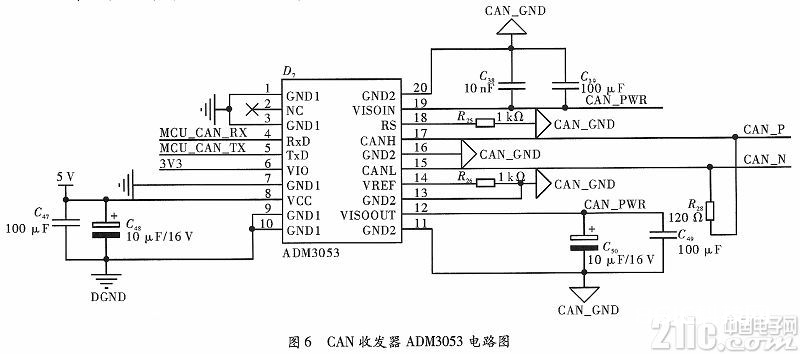

ADM3053集成了双通道阻隔器、CAN收发器和ADI公司的isoPower DC/DC转化器;芯片内部振荡器输出一对方波,驱动内部变压器供给阻隔电源。该器材选用5 V供电,最高作业频率为1 Mbit·s-1,其电路规划如图6所示,图中CAN_P、CAN_L作为差分信号线,以双绞线作为物理层传输。

3 运用软件规划

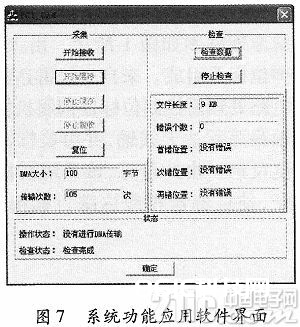

体系规划完结后,在Windows XP操作体系下,用C言语编写运用软件,并对体系功用与功能进行测验,软件界面如图7所示。

该运用软件发送开端接纳信号,查询CAN节点数据和状况,操控CAN节点向上位机发送收集到的数据与当时节点的状况信息。上位机保存接纳到的数据、状况信息并对其进行检查,显现犯错方位。图7所示为进行了105次DMA传输、且保存9 kB数据、对数据进行检查后的显现界面。该测验过程中,CAN发送的每帧数据为0~99接连改变的数据,经过测验能够验证接纳到的数据完全正确。

4 完毕语

规划开发的PCI_CAN数据转化体系,数据最高传输速率为1 Mbit·s-1,最远通讯间隔>10 km,满意CAN总线的功能要求。选用FPGA+PCI9054的规划使体系便于晋级和移植;在多种不同类型计算机中运转,均未出现因与计算机不相容而发生找不到PCI卡或蓝屏的现象,达到了规划和运用意图。