机载合成孔径雷达(Synthetic Aperture Radar,简称SAR)是以“合成孔径”原理和脉冲紧缩技能为理论基础,以高速数字处理和准确运动补偿为前提条件的高分辨率成像雷达关于机载合成孔径雷达成像处理来讲,仅有方针的原始回波数据是不行的,还有必要取得雷达和载机的参数别的,为了满意信号处理机实时处理的要求,要求输入到处理机的各种数据契合处理机成像处理的数据格局这样,处理机在取得数据帧后就可以直接进行成像处理而不用再有格局转化的开支可是 方针的原始回波数据与雷达和载机的参数数据来自两个不同的设备它们的数据格局和时序都是由各自的设备确认的,因而信号处理机便面临着与外围设备接口的问题

1 体系功用

在本机载合成孔径雷达体系中,进出接口板卡的数据流包含数据收集设备输入的原始回波数据监控设备输入的雷达和载机的参数数据以及输出到处理机的成像处理数据它们有如下特色:①输入数据流的速度和时序不匹配数据收集设备和监控设备是两个异步的体系,它们都有自己的守时操控电路,以自己的速度传输数据②输入输出数据流的信息格局不匹配数据收集设备输入的原始回波数据和监控设备输入的雷达和载机的参数数据选用FPDP协议传输,接口板卡输出到处理机的数据选用Link口传输协议进行传输

考虑到进出接口板卡数据流的特色和雷达体系对接口板卡的操控要求,接口板卡要具有如下功用:

(1)设置数据的缓冲存储逻辑,以习惯不同设备之间的速度差异和时序差异;

(2)进行信息格局转化,将方针的原始回波数据与雷达和载机的参数数据打包,刺进相应的帧信息构成处理机要求的数据帧,并操控数据流的走向;

(3)完结PCI接口,可以发生PCI中止;

(4)具有在线自检测功用

2 体系硬件结构规划

为了简化体系硬件规划,添加体系的灵敏性,选用FPGA芯片完结体系要求的数据格局转化打包分发和逻辑操控功用数据缓存选用硬件FIFO和软件双口RAMPCI接口选用专用接口芯片完结硬件FIFO和软件双口RAM的写时钟分别由各自的FPDP接口供给,其它时钟由接口板上的晶振供给体系的硬件结构框图如图1所示

2.1 输入数据流的缓存计划

为了习惯处理机与数据收集设备和监控设备之间的速度差异,处理速度不匹配问题,需求将输入的数据先进行缓存数据收集设备送入的原始回波数据每帧的数据量比较大,接口板卡上规划了硬件FIFO作为原始回波数据的缓存器,FIFO的读写使能由FPGA编程操控,写时钟由FPDP接口供给,读时钟由接口板卡上的晶振供给数据收集设备和监控设备是两个异步的体系,雷达参数数据流和原始回波数据流之间没有同步联系,一帧雷达参数数据对应几帧原始回波数据,因而规划顶用双口RAM作为雷达参数数据的缓存器别的,每帧雷达参数的数据量比较小,本规划在FPGA内使用参数化的模块库(Library of Parameterized Modules,简称LPM)中的lpm_ram_dp编程完结双口RAM,简化了硬件规划

2.2 PCI接口规划

完结PCI接口的计划一般有两种:选用可编程逻辑器材和选用专用总线接口器材选用可编程逻辑器材完结PCI接口的最大优点是比较灵敏,缺陷是规划难度较高,开发周期较长选用专用接口器材完结尽管没有选用可编程逻辑器材完结那么灵敏,但可以有用地下降接口规划的难度,缩短开发时刻本体系选用专用接口器材PCI9052完结接口板卡的PCI接口

接口板卡的硬件资源为映射到FPGA内部寄存器的I/O映射空间和一个中止源PCI9052供给5个部分地址空间,选用Space0作为接口板的地址空间,分配16个8位地址一起设置相应的初始化,PCI装备寄存器中的PCIBAR2设置为0XFFFFFFF0,向体系恳求分配内存的数量为16设置部分地址空间的规模为0X01000000~0X01000010PCI9052供给两个部分中止源,选用LINTi1FPGA供给电平触发中止信号,因而PCI9052的中止触发形式设置为电平触发使用PCI9052的部分设备片选信号CS0#作为FPGA的片选信号CS0#片选信号的开端地址和地址规模由CS0 Base Address寄存器的设置值0x01000011决议,即开端地址为1000000h,地址规模为20hPCI9052寄存器的初始值由串行EEPROM供给,在PCI9052加电后读取EEPROM有必要选用支撑连读功用的芯片,本规划中选用FairChild Semiconductor公司的93CS46N

2.3 FPGA的装备规划

本规划为FPGA供给了两种装备方法:自动串行装备和被迫串行装备

自动串行装备由EPC2向FPGA器材输入串行位流的装备数据在该装备方法下,一向由FPGA操控着装备进程在加电进程中,FPGA检测到nCONFIG由低到高的跳变时,就开端预备装备FPGA将CONF_DONE拉低,驱动EPC2的nCS为低,而nSTATUS引脚开释并由上拉电阻拉至高电平使能EPC2尔后,EPC2就用其内部振荡器的时钟将数据串行地从EPC2DATA输送到FPGADATA0当装备完结后,FPGA开释CONF_DONE,将EPC2与体系阻隔

被迫串行装备由编程硬件通过ByteBlaster装备ByteBlaster发生一个由低到高的跳变送到nCONFIG引脚,然后由编程硬件将装备数据送到DATA0引脚,该数据锁存至CONF_DONE变为高电平中止当CONF_DONE变成高电平时,用DCLK的10个周期初始化FPGA,器材的初始化由下载电缆自动履行

为了两种装备方法共存,规划顶用拨码开关将EPC2与FPGA和ByteBlaster的下载电缆插座阻隔当用被迫串行方法装备时,拨码开关断开,由上位机通过ByteBlaster下载电缆加载FPGA当用自动串行方法装备时,拨码开关接通,由EPC2加载FPGA电路图如图2所示

2.4 在线自检测功用

板卡规划时还应考虑便于日常调试保护及毛病检测定位板卡在硬件上针对各电源信号和要害的状况信号规划了信号灯,一旦发现有误,便可给出信号触发该电路板上的信号灯告警,定位体系毛病别的在电路规划时应留出测验孔,以添加电路的可测性

3 体系的软件规划

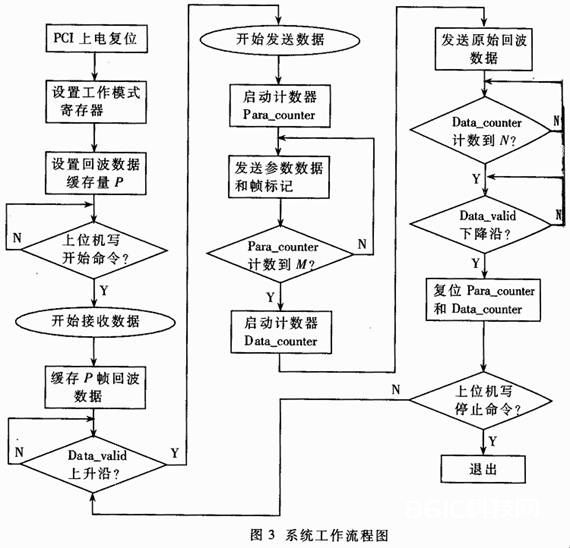

体系上电后, PCI上电复位,FIFO清零上位机向相应寄存器写入初始值,完结寄存器设置当体系发动信号有用时,接口板开端接纳数据,进行数据打包和分发,直到上位机向接口板卡写中止指令中止图3给出了体系作业流程图

3.1 数据的打包和流向操控

雷达参数数据和原始回波数据的数据源是异步的,不能确保两者切当的对应联系,接口板卡使用对缓存原始回波数据FIFO和缓存雷达参数数据双口RAM的读写操控,调整雷达参数数据和原始回波数据对应联系,将两种数据源按处理机要求的输入数据格局组成正确的数据帧雷达参数数据和原始回波数据打包后的数据帧格局如下:

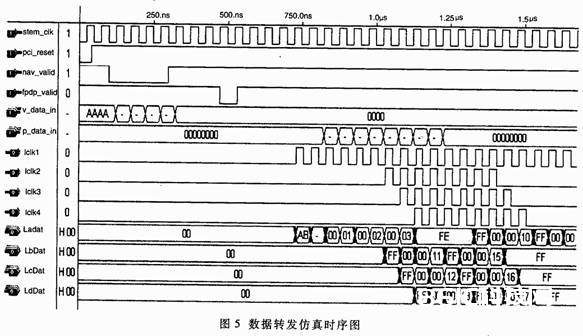

在程序中,规划了雷达参数发送操控计数器Para_counter和回波数据发送操控计数器Data_counter体系作业后,每次检测到原始回波数据流的数据有用信号data_valid的上升沿(符号收到完好的一帧回波数据)时,发动雷达参数发送操控计数器开端计数,当计数到设定的值(本规划中为25)时中止计数并发动回波数据发送操控计数器开端计数,计数到设定的值(本规划中为5000)时中止计数当检测到原始回波数据流的数据有用信号data_valid的下降沿(符号开端接纳新的一帧回波数据)时,两个计数器都清零依据计数器的计数值发生Link口挑选信号确认数据的流向图4给出了数据流向的示意图图5给出了根据MAXPLUSⅡ10.0的仿真成果,仿真显现正确地完结了数据打包和流向操控

3.2 Link口传输协议的完结

Link口的数据传输是在同步时钟线(LxCLK)与应对线(LxACK)彼此握手的情况下同步传输的一个传输字为32bit,Link口以4bit为单位进行传输在LxCLK上升沿,发送端会发送一个新的4bit数据,在LxCLK的下降沿,接纳方锁存数据线上的数据8个4bit数据发送结束后,假如接纳方预备好接纳下一个字,则将LxACK置1发送方在每次发送新字的第一个4bit时对LxACK采样,假如LxACK为0,标明接纳方没有预备好,则发送方坚持LxCLK为高电平,且数据线上坚持当时的4bit数据,直到接纳方将LxACK置1,发送刚才将 LxCLK下拉,并持续发送新的数据当发送方缓存为空时,标明没有数据需求发送,则LxCLK坚持为低电平接口板使用VHDL言语完结了Link口传输协议下面给出了要害的程序片断:

ChangeStateMode process NibleCount empty LxACK PresentState empty

begin

case PresentState is

when SendACK =>

if LxACK='1' and empty='0' then

NextState=Send

else NextState=SendACK

end if

when Send =>

if NibleCount/= 3 or NibleCount=3 and empty='0'and LxAck='1' then

NextState=Send

else NextState=SendACK

end if

end case

end process changestatemode

4 使用和定论

现在该接口板现已完结了电路规划软件仿真和制板,并使用到某机载合成孔径雷达数字信号处理机中接口板卡坐落信号处理机的前端,通过CPCI机箱的前面板接口,选用一块PMC子板完结体系选用了图1所示的体系结构,锁存器选用TI公司的SN74LVT16374,时钟驱动芯片选用IDT公司的IDT49FCT3805APY,FIFO选用IDT公司的IDT72V36110,PCI接口芯片选用PLX9052,FPGA选用Altera公司的EP1K100FC256-1通过实验室阶段和外厂实验,接口板都作业正常,达到了规划要求