电子技术的飞速发展变化给板级规划带来许多新问题和新应战。首要,因为高密度引脚及引脚尺度日趋物理极限,导致电路极低的布通率;其次,因为体系时钟频率的进步,引起的时序及信号完好性问题;高速数字电路(即高时钟频率及快速边缘速率)的规划将成为干流。

PADS(PeroonaI Automated Design Systems,个人主动规划体系)Logic9.0是一个功用强壮、多页的原理图规划输入东西,具有在每页进行快速存取、在线元件修正、库办理便利简练等特色,一切这些都为PADS Layout供给了高效的电路板规划环境,进步了由原理图规划链接到PCB制版的转化功率。PADS Layout9.0是一个杂乱的、高速印制电路板规划软件。它具有快速交互布线修正器(FIRE).它的这一功用在很多的交互布线形式中别出心裁,因为FIRE选用强壮功用的算法,布线完成后很少需求用户修正调整,能够运用户在布线时节约很多时刻,进步功率。对表贴元件等细微焊盘间隔、对高速布线的约束条件设定、对图形用户界面的定制等方面功用,PADS Layout9.0软件都是无可挑剔的。因为PADS Logic9.0和PADS Layout9.0两软件运转速度快,加之功用强壮,有些简略的操作能够完成杂乱的功用、快捷键便利、视窗宽等长处。

PADS软件好用,易上手,是现在市场上运用规模最广的一款EDA软件,适宜大多数中小型企业的需求;而且高端软件(如Cadence allegro)能完成的功用PADS软件也都能完成。经过对多年的EDA规划经历的总结,我认为运用PADS软件中的差分和等长走线等功用完成高速电路布线是一个很好的挑选。下面,就以Hi3511器材组合为例进行详细介绍。

1 板层结构规划

板层的结构是决议体系的EMC功用一个很重要的要素。一个好的板层结构对按捺PCB中辐射起到杰出的作用。现在常见的高速电路体系中大多选用多层板而不是单面板和双面板,板层结构的规划应留意以下几个方面:

1)一个信号层应该和一个敷铜层相邻。

2)信号层应该和接近的敷铜层严密耦合(即信号层和接近敷铜层之间的介质厚度很小)。

3)电源敷铜和地敷铜应该严密耦。

4)体系中的高速信号应该在内层且在两个敷铜之间,这样两个敷铜能够为这些高速信号供给屏蔽作用且将这些信号的辐射约束在两个敷铜区域。

5)多个地敷铜层能够有用的减小PCB板的阻抗,减小共模EMI。

要满意以上要求,引荐运用8层板的规划,其层叠结构如下:

①TOP层:信号层(器材层)

②第二层:地平面层

③第三层:信号层

④第四层:地平面层

⑤第五层:电源平面层

⑥第六层:信号层

⑦第七层:地平面层

⑧BOTTOM层:信号层(器材层)

但考虑到本钱要素,咱们将Hi3511模块电路的板层界说为6层,其层叠结构如图1所示。

图1 板层结构

2 元器材的布局

元器材布局是制造PCB的重要环节,布局是否合理直接影响电路的功用,在布局时应留意以下几个方面:

1)先确认与结构联系密切的元件方位,如定位孔、衔接器等。

2)遵从“先大后小,先难后易”的布局准则,先摆放中心器材或者是较的的器材,再以其为中心摆放周围的电路元器材。例:先确认Hi3511的放置方位,再将其周围的元器材按电路联系摆放的适宜方位。

3)布局时应将高电压、大电流信号与低电压、小电流信号分隔;数字信号与模拟信号分隔;高频信号与低频信号分隔。

4)接口芯片尽量接近变压器或衔接器。

5)时钟电路连线尽量短,并远离灵敏电路。

6)滤波电容放置间隔电源管脚越近越好。例:DDR2 SDRAM的每一个电源管脚周围都加了至少一个去耦电容,如图2所示。

图2 去耦%&&&&&%摆放

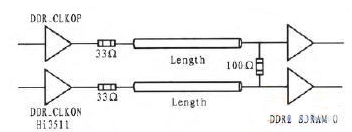

7)源端的串联端接尽量接近源端放置,并行端接尽量接近接纳端。例:如图3所示是Hi3511与DDR2_CLKOP、DDR2_CLKON的端接匹配结构,由图可知,33Ω的串联匹配应该尽量接近Hi3511端而100Ω的并联差分匹配电阻应尽量接近DDR2端。

图3 Hi3511与DDR2_CLKOP,DDR2_CLKON的端接匹配结构

3 布线

PCB布线是EDA规划的重要环节,是体系能否正常有用作业的关键要素。下面简略介绍一下PCB布线中要留意的一些问题。

1)阻抗操控

阻抗操控的PCB板是指PCB板上一切网络的阻抗都操控在必定的规模以内,如20~75Ω。

在Hi3511模块中,期望咱们把走线的特性阻抗操控在50Ω,差分走线的特性阻抗操控在100Ω,经过对叠层的剖析,在PADS软件中将一般走线线宽界说在5mil,最小间隔为5mil,独自界说几个差分对走线宽度为4mil,间隔10mil,这样画出的PCB图根本能满意阻抗操控要求。

2)走线间隔的巨细。一般常用到的间隔为两倍线宽。能够透过仿真来知道走线间隔对时序及信号完好性的影响,找出可容忍的最小间隔。不同芯片信号的成果或许不同。

3)走线的规矩设定等级

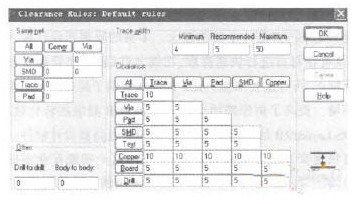

①在PADS软件中能够对不同的走线进行不同的规矩设置。如一般信号线咱们进行惯例设置,如图4所示,只规矩线宽间隔等。在布线过程中也首要遵从一般的准则就好。如:走线尽量短,尽量走直线或135°角的折线,电源和地引线尽量短、尽量粗等。

图4 走线的规矩设定

②能够将需求等长走线的网络先进行分组,在布线过程中,应选用分组布线的办法。先连通一组中的每一个网络,然后查询网络的长度,从中找到最长的一个作为参阅,界说本组网络的长度,如图5所示。本组中其他网络进行蛇行走线,并调整其长度,以到达规矩要求。

图5 等长走线的设置

③关于差分信号,应尽量不打孔走在接近地平面的内层,并需求独自设定线宽和间隔,如图6所示。在走线的时分要留意尽量短,且两根线要严厉等长。

图6 差分信号设置

4)布线过程

①先布地线(电源线):咱们能够从元器材的接地(电源)管脚直接引线出来就近打孔和地(电源)层相连,而且连线尽或许的短且粗。

②归纳信号的优先等级(如时钟信号、差分线、等长线等)和布线密度状况挑选挑选布线的优先次序。再按相应的规矩进行布线。

如在Hi3511模块中,连线最多,要求最杂乱的便是与DDR2 SDRAM之间的衔接,硬件规划指南中主张将数据信号、地址信号、操控信号、时钟信号等一切线的长度持平,则作用到达最优,误差规模为±50mil.并主张时钟信号的走线长度小于4.5英寸。咱们将数据信号、地址信号、操控信号、时钟信号分红不同的组,进行分组布线。从布局图中咱们能够看出数据信号是一切信号线中途径最长的。故此,咱们先对数据信号进行布线,选用蛇行走线使数据线到达等长,其走线误差操控在20mil中。经丈量数据信号网络的实践布线长度为3430±20mil,满意时钟信号的走线长度的要求,故将此长度作为地址信号、操控信号、时钟信号等线的长度根据,将其它信号进行分组蛇行走线,以满意长度要求。在这里还要留意每组信号线与其他走线之间的间隔要大于20mil。时钟等重要信号要尽量走到第三层,并用地进行阻隔。布线成果如图7所示。

图7 布线成果

4 电源切割

现在体系的作业电源多为多个电源,那么在实践的操作中就需求研讨电源层的切割问题。

1)电源切割过程中即要确保同一组电源围住在一起又要留意不要跨信号线进行切割。即要确保信号有杰出的回流途径。

2)电源层比地层内缩20H,H为电源层与地层之间的间隔。

5 定论

经过对Hi3511模块的PCB规划实践,充分说明了,只需咱们把握了高速电路规划的根本规矩和技巧,结合PADS软件对布局布线进行的各种规矩约好,并运用差分和等长走线等各种强壮的功用,进行高速电路规划是一个很好的挑选。