跟着电子体系中传感器和信号源的快速添加,使得设备设计师们可以在体系MCU或传感器交融协处理器中参加更多的模仿信号通道。尤其是在日益开展的小型物联网领域中更是如此。

信号均匀法是一项常用于此类数据收集体系的技能,可以增强数值成果的可用分辨率并按捺多种噪声。虽然过滤办法简略,但其全体作用要取决于所运用的均匀法。本文将对传统的序列均匀法和最新的穿插均匀法进行比较。

许多现代的混合信号MCU和片上体系都直接将均匀法参加到模仿-数字转化器硬件中。这大大削减了MCU需求完结的处理量,简化代码编写,缩短处理器需求在高功耗方式中的运转时刻。

虽然多种信号与设备之间完结衔接的模仿输入多路复用器已十分遍及,但大部分混合信号MCU的硬件均匀功用每次只能在一条信号通道中履行。当均匀进程完结后,通常会引发中止,然后固件在中止中挑选另一个需求转化的模仿输入。在一些设备中,比方赛普拉斯半导体公司的PSoC 4系列1 Msps 12位ADC可编程片上体系,其通道序列内置于转化器硬件中,可在无需处理器干涉的状况下对一切通道履行均匀功用。

这种传统的对单一通道信号进行屡次转化后才转到下一个通道的均匀模型被称为序列均匀。这种办法存在一些约束,首要问题在于会下降多通道环境中的可用采样率,包含被均匀的通道和序列中不需求均匀的通道。

最近呈现了一种新的办法,可以增强数据收集体系设计师所运用的各种东西。这项技能被称为穿插均匀法,它给需求收集高频率信号以及需求快速收集非均匀通道样本的体系带来了福音。

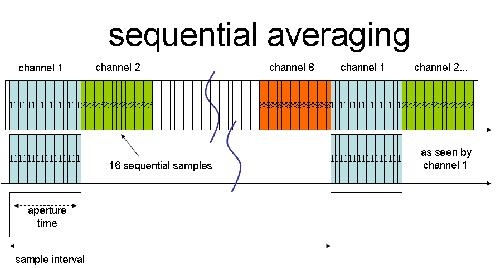

序列均匀和穿插均匀的差异咱们可以从一些图文中得到解说,本文挑选了一个8通道的装备作为示例。原始ADC采样率设置为800 ksps,每个通道中的16个12位样本将被一同均匀。这样会发生一个16位的输出字,而12位样本量化的信噪比奉献量则会把信噪比约束在相对于14位转化器的水平(假定每个样本的量化噪声奉献量不相关)。

因为有8个通道,且每个通道取样16次后取得终究成果,因而ACD需求进行128次转化才干生成各成果组。这一进程需求160微秒,成果组的可用频率为6250次/秒。

这个比方还假定每个通道都有自己的成果寄存器,本示例中所运用的PSoC 4便是如此。但部分混合信号MCU有所不同,它们只要一个成果寄存器,因而不得不在转化通道时进行读取。

图1所示的是伪代码方式的规范序列均匀解决方案,其行为如下:

● 改写累积寄存器

● 挑选通道1

● 以1.25微秒距离进行16次采样,将它们累积在通道1的寄存器中,总耗时20微秒

● 挑选通道2

● 以1.25微秒距离进行16次采样,将它们累积在通道2的寄存器中,总耗时20微秒

● 重复上述进程,完结8个通道的取样

● 搬运8个成果,呈现中止或DMA

图1:序列均匀

每个输入端通过接连16次转化进行采样。一个通道的接连转化需求160微秒,因而每个通道的采样频率为每秒6250个样本。采样孔径(即一个通道的采样时刻)为20微秒。这一孔径会发生低通滤波的作用,但是带宽会十分高,呈现(1/20微秒)50千赫倍数频率响应的零点。这一过滤无法避免混叠。这一输入信号中的任何挨近6250赫兹倍数的频率成分将被混叠下降到挨近DC的水平,然后或许制作显着的丈量噪声。只能通过运用每个通道的防混叠过滤器对其进行预先过滤,以缓解这一现象。

此外,各通道间会呈现20微秒的时刻差错。假如需求核算穿插通道数学函数(比方相关性或功率核算),这一时刻差错会发生严峻差错。

假如在这样一个序列中有未均匀的通道,此类通道的采样频率首要由其他序列采样中需求做均匀的通道决议。因而,虽然ADC的采样频率为800 ksps,但未均匀的通道的采样频率要远低于此。最理想的状况是将这800 ksps频率均匀分摊到8个通道,每个通道频率为100 ksps。

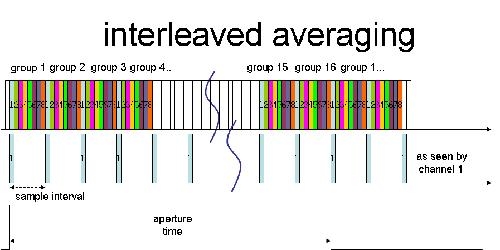

针对这一难题的解决方案穿插均匀规律有用得多(见图2)。定序器与之前相同环绕输入通道,但这一次仅对每个通道收集一个样本。在通道通过N次单次采样后,可以读出一切累积寄存器的输出。

图2:穿插均匀

伪代码方式的穿插均匀序列如下:

● 将硬件循环计数器设置为0

● 改写累积寄存器

● 重复

● 循环计数器+= 1

● 挑选通道 [循环计数器]

● 取一个样本,将它累积到通道 [循环计数器]的寄存器中,总时刻1.25微秒

● 直到循环计数器 ≥8

● 搬运8个成果,呈现中止或DMA

这个均匀进程的信号特征显着不同。现在不会呈现接连转化,取得每个均匀数的16次转化被均匀地分摊,每轮转化耗时160微秒,距离10微秒。换言之,每个通道的采样频率为100 ksps,这是将800 ksps ADC分摊到8个通道时的理论最大值。这一进程的采样孔径为160微秒,因而体系频率响应零点会呈现在终究选用频率的倍数上。其长处在于输入信号中不会呈现混叠下降到DC的高频率噪声。这可大大提高丈量的稳定性,然后明显下降模仿过滤要求。

通道之间仍存在时刻差错,但已削减到1.25微秒,比较160微秒的抽样时刻要小得多,大大削减了跨通道核算的差错。

在本示例中,运用穿插均匀法的转化器子体系以相当于约14位信噪比和6.25 ksps的频率供给8个通道的样本,并有用防备混叠,缩短通道间的延迟时刻。

穿插均匀法正在赛普拉斯半导体的新式可编程芯片体系设备上推广,包含近期推出的Cortex M4-based PSoC 6和赛普拉斯PSo4系列模仿产品PSoC Analog Coprocessor。该设备的ADC中的硬件(可通过PSoC Creator Scan_ADC 组件进行完好装备)还可以在不履行均匀功用的状况下转化序列中的任何通道。这意味着在更前面的比方中,通道仍可以到达100 ksps频率,且不会影响已均匀通道的时刻。

以高分辨率和高采样频率收集多个通道的样本,极大的添加了运用现代混合信号可编程片上体系进行经济而高性能的模仿信号捕捉的或许性。当需求转化多个或许要求进行均匀的模仿通道时,请注意多种均匀方式对设备信号处理才能所发生的影响。