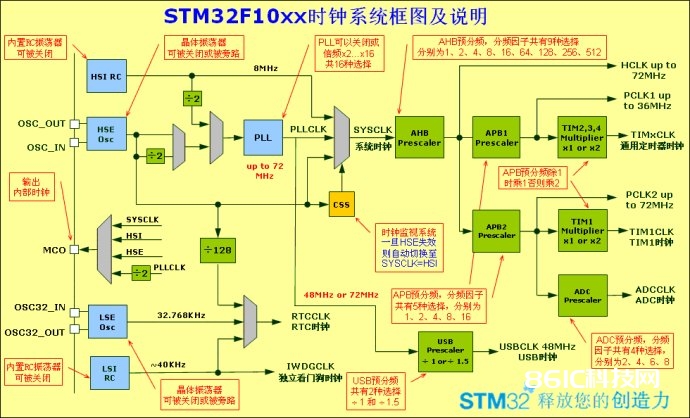

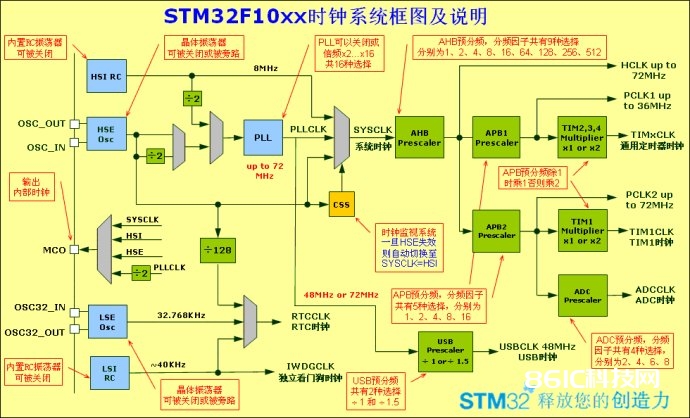

1STM32有五个时钟源:HSI、HSE、LSI、LSE、PLL11HSI:高速内部时钟、RC振荡器、频率为8MHz、时钟精度较差,可作为备用时钟源(时钟安

1

STM32有五个时钟源:HSI、HSE、LSI、LSE、PLL

1.1

HSI:高速内部时钟、RC振动器、频率为8MHz、时钟精度较差,可作为备用时钟源(时钟安全体系CSS)。

1.2

HSE:高速外部时钟、可接外部晶体/陶瓷谐振器(4MHz~16MHz)或外部时钟源(HSE

旁路,Max 25MHz)。

1.3

LSI:低速内部时钟、RC振动器、频率为40kHz,大容量MCU可进行LSI时钟校准。

1.4

LSE:低速外部时钟、接频率为32.768kHz的外部晶体/陶瓷谐振器。

1.5

PLL:锁相环倍频输出,时钟输入源可挑选HSI/2、HSE或HSE/2。倍频可挑选为2~16倍,最大输出72MHz。

用户可经过多个预分频器装备AHB总线、高速APB2总线和低速APB1总线的频率。AHB和APB2域的最大频率是72MHZ。APB1域的最大答应频率是36MHZ。SDIO接口的时钟频率固定为HCLK/2。

40kHz的LSI供独立看门狗IWDG运用,别的它还能够被挑选为实时时钟RTC的时钟源。别的,实时时钟RTC的时钟源还能够挑选LSE,或许是HSE的128分频。RTC的时钟源经过RTCSEL[1:0]来挑选。

STM32中有一个全速功用的USB模块,其串行接口引擎需求一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,能够挑选为1.5分频或许 1分频,也便是,当需求运用USB模块时,PLL有必要使能,而且时钟频率装备为48MHz或72MHz。

别的,STM32还能够挑选一个PLL输出的2分频、HSI、HSE、或许体系时钟输出到MCO脚(PA8)上

体系时钟SYSCLK,是供STM32中绝大部分部件作业的时钟源。体系时钟可挑选为PLL输出、HSI或许HSE,在挑选时钟源前留意要判别方针时钟源是否现已安稳振动。Max=72MHz,它分为2路,1路送给I2S2、I2S3运用的I2S2CLK、I2S3CLK;别的1路经过AHB分频器分频(1/2/4/8/16/64/128/256/512)分频后送给以下8大模块运用:

① 送给SDIO运用的SDIOCLK时钟。

② 送给FSMC运用的FSMCCLK时钟。

③ 送给AHB总线、内核、内存和DMA运用的HCLK时钟。

④ 经过8分频后送给Cortex的体系定时器时钟(SysTick)。

⑤ 直接送给Cortex的闲暇运转时钟FCLK。

⑥ 送给APB1分频器。APB1分频器可挑选1、2、4、8、16分频,其输出一路供APB1外设运用(PCLK1,最大频率36MHz),另一路送给定时器(Timer2-7)2、3、4倍频器运用。该倍频器可挑选1或许2倍频,时钟输出供定时器2、3、4、5、6、7运用。

⑦ 送给APB2分频器。APB2分频器可挑选1、2、4、8、16分频,其输出一路供APB2外设运用(PCLK2,最大频率72MHz),另一路送给定时器(Timer1、Timer8)1、2倍频器运用。该倍频器可挑选1或许2倍频,时钟输出供定时器1和定时器8运用。别的,APB2分频器还有一路输出供ADC分频器运用,分频后得到ADCCLK时钟送给ADC模块运用。ADC分频器可挑选为2、4、6、8分频。

⑧ 2分频后送给SDIO AHB接口运用(HCLK/2)

2 时钟输出的使能操控

在以上的时钟输出中有许多是带使能操控的,如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等。

当需求运用某模块时,必需先使能对应的时钟。

需求留意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,不然它的倍频值就为2。

连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、 Timer2、Timer3、Timer4。留意USB模块尽管需求一个独自的48MHz时钟信号,但它应该不是供USB模块作业的时钟,而仅仅供给给串行接口引擎(SIE)运用的时钟。USB模块作业的时钟应该是由APB1供给的。

连接在APB2(高速外设)上的设备有:GPIO_A-E、USART1、ADC1、ADC2、ADC3、TIM1、TIM8、SPI1、ALL

————————————————————————————————–

下图是STM32F10xx时钟体系的框图,经过这个图能够一望而知地看到各个部件时钟发生的途径,还能够很方便地计算出各部分的时钟频率。

STM32的四个时钟源(HSI、HSE、LSI和LSE)也在图中标出;图中心的时钟监督体系(CSS)是在许多ST7的单片机中就呈现的安全设置。

特别留意:图的右边,输出定时器时钟之前有一个乘法器,它的操作不是由程序操控的,是由硬件依据前一级的APB预分频器的输出主动挑选,当APB预分频器的分频因子为 1时,这个乘法器无效果;当APB预分频器的分频因子大于1时,这个乘法器做倍频操作,行将APB预分频器输出的频率乘2,这样能够确保定时器能够得到最高的72MHz时钟脉冲。

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/fangan/biancheng/258942.html