进步FPGA规划生产力的东西、技巧和办法,影响FPGA规划周期生产力的最大要素是什么?许多规划人员的答案是,时序收敛是影响产品规划走向市场的要害。高效完结时序收敛,取得可信的成果是每一位规划师的愿望。但是,这仅仅是问题的一部分。

要在整个规划周期中实在做到高效率,规划师需求依靠整个规划环境以及其间的多种东西来办理流程杂乱性,并为FPGA规划的共同风格和办法供给实在的解决方案。一个完好有用的规划环境供给了问题的焦点和通明性,最好是供给一个无缝的解决方案。

要供给最大的生产力,一个完好的FPGA规划环境应当包含如下一些首要特性:

·快速确认时序问题—所供给的东西能够为规划师供给要害信息,然后使他们敏捷发现潜在的瓶颈。·运用一系列视图探求成果—规划杰出的东西能够让规划师从多个视角调查有关时序途径的信息。

·以规划为中心,而非东西—能够在不同视图间无缝切换,东西操作通明,但规划问题明晰。

·供给有意义的中心成果—生产力包含能在尽早的阶段监测规划功用。假如尽早解决问题,成果是每天能够有更多的重复时机。

·办理杂乱的源代码结构—规划东西需求便利的源文件的办理,供给兼容规划人员所喜爱的源代码操控机制的才能和办法。

运用支撑更快、更简略的时序收敛而且支撑规划集合的规划东西。下面的比如具体评论了上面的论题。

快速确认时序问题

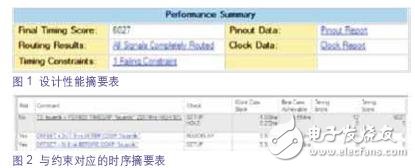

“规划满意时序要求吗?”每次经过布局布线完结规划施行时,一般规划师都会问这个问题。不管答案是什么,规划人员都期望以简练的办法当即取得此类信息,如图1所示。

下一个问题便是“到底有多少满意时序要求,又有多少没有到达?”图2给出了与每一束缚对应的时序成果简表。

运用不同的视图探求成果

一旦以摘要办法呈现时序成果,还能够很简略地调查特定束缚或途径的具体信息。从上面的摘要中,简略地点击一条束缚,规划师就能够看到更具体的时序陈述,如图3所示。

规划人员能够十分快速便利地从高层时序摘要转到具体的文本信息,了解特定的时序途径。

文字信息仅仅了解规划时序特性的一种办法。一般,图形显现更有协助。关于上面的规划,点击超链接能够得到在FPGA器材中时序途径的实践物理完结的图形显现,如图4所示。

图4中的比如显现出时序途径从一个开始块,经过每个中心块,终究停止在途径端点的实践物理布局。视图也给出了这些块之间实践布线的视觉体现。该 视图能够协助答复与时序相关的问题,如:“有没有特别长的途径?”以及“有没有逻辑的布局跨过了多个时钟区域?”跟着规划师逐步扩大视图到特定点,应当可 以看到如图5所示的片内部装备。

上面的物理器材视图一般很有用,但关于了解规划中不同的时序途径细节来说,其它表明办法也相同有用。一种根据原理图技能的视图如图6所示。

在这一时序途径视图中,很简略看出数据途径中的逻辑层次数,并了解时序途径怎么穿越规划层次中的不同部分。还能够逐步扩大显现的原理图,显现其它逻辑连接到构本钱途径的单元的状况。

以规划为中心,而非东西

经过同一规划问题的多种视图,规划师能够以不同的办法考虑时序问题,并定制针对问题的最适合的解决方案。当一切这些调查点都集成在单个规划环境中时,在不同视图之间的切换就只需点击一下鼠标就能够了。有时还能够将多个视图并排显现,如图7所示。

供给有意义的中心成果

在FPGA规划进程的中心,运转多个施行是很往常的。关于有许多时序要求的大型规划来说,能够查看中心成果是很有用的。经过便利的办法暂停、检测和康复施行进程,规划师能够在规划编译的进程中取得更好的规划可视性,如图8所示。

幻想一下,过度的时序束缚或许需求更多时刻才能够完结规划施行的布局和布线阶段。经过暂停流程,有些规划师或许以为规划时序现已“满意挨近”, 然后能够将规划提交到实验室继续进行功用调试。一起,做完这一步后,还能够康复布局布线,继续进行优化处理以满意终究时序要求。

更重要的是,经过查看中心成果,规划师能够更快地确认是否存在任何时序要害区域并尽早采纳举动。

办理杂乱的源代码结构

跟着规划杂乱性的添加,源代码结构的杂乱性也在添加。许多规划师选用第三方源代码操控东西来办理杂乱性并确保源代码文件的一致性。这些文件不只限于HDL源文件,还包含束缚文件、仿真测验基准等。

每位规划师都有处理这些问题的特有风格和办法,因而并没有适用于一切用户的全能解决方案。经过供给便利的机制来确认并有挑选地输出FPGA规划项目中的一切源代码/文件,规划师能够选用最适合自己需求的外部源代码操控东西。输出进程还包含输出ASCII 办法的项目信息,今后可运用这一信息重建这一项意图前期阶段。

结语

对FPGA规划生产力来说,快速完结时序挨近确实是一项要害要素。能否快速了解规划时序状况是衡量FPGA规划环境有用性的要害。因为导致时序途径呈现时序失利的原因许多,因而规划师需求从多种不同视点(文字和图形)把握便利调查时序信息的才能。这样他们才能够做出怎么改善规划时序的最佳决议计划。无缝且通明的归纳东西将可协助快速完结时序收敛