1 导言

一切的无线电发射机都含有某种程度上非线性的射频功率扩大器。假如被扩大信号的包络对错稳定的,那么功率扩大器非线性最首要的成果是发生交调失真(IMD)。现在有多种功率扩大器线性化办法,前馈便是其间一种。在实践运用中,扩大器特性不光与本身有关.并且还与温度、输入信号的频率以及元件老化程度等要素有关,所曾经馈扩大器有必要具有自习惯才能。

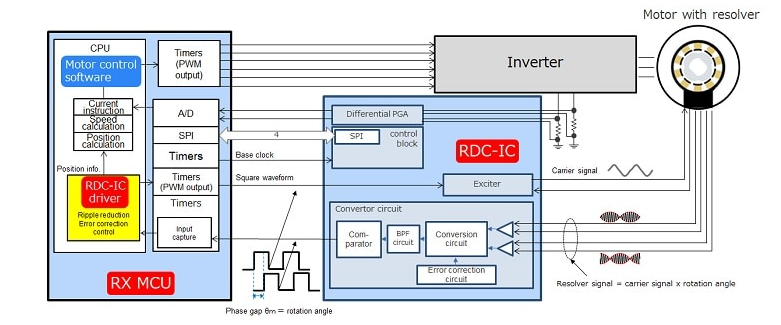

自习惯前馈功率扩大器由两个模块组成:射频模块和自习惯操控模块。其体系全体框图如图1所示。

运用梯度信号的自习惯算法在文献[1]中进行了充沛证明和阐明,本文首要评论该自习惯算法所需信号依据软件无线电的数字接纳技能,并以运用于WCDMA体系的前馈线性功率扩大器的规划为例,完结了依据软件无线电的数字中频信号的接纳。由于软件无线电规划的灵活性,替换本规划的少数硬件与初始化程序设置即可完结其他无线通信体系中的信号接纳功用。

2 模块完结

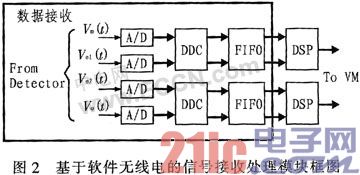

自习惯前馈功率扩大器的原理如图1所示,信号的数字接纳模块需求完结Vm、Ve1、Ve2和Vo四路信号的接纳;DSP处理模块分别对Vm、Ve1和Ve2、Vo进行相关运算,得到成果经过D/A改换后,分别对矢量调制器VM1和VM2进行自习惯操控。依据软件无线电的自习惯操控模块中多路信号数字接纳处理框图如图2所示。

WCDMA体系作业频段为2 110 MHz~2 170MHz,单载波的WCDMA信号带宽为5 MHz,码片速率为3.84 Mc/s,与本文所评论内容相关的技能方针为:谐波起伏低于-40 dBc;邻信道功率比(ACPR)优于-45 dBc(榜首邻信道)、优于-50dBc(第二邻信道)。要到达上述方针,需求对A/D采样和DDC电路进行优化规划。

2.1 高速A/D采样

2.1.1 采样率f s与位数N的挑选

要到达上述的谐波起伏和ACPR的方针,A/D采样所带来的噪声功率要低于技能方针。关于一个N位的ADC,信噪比SNR可近似由公式(1)给出:

SNR=6.02N+1.76+101g( fs/2B) (1)

体系处理单载波WCDMA信号为5 MHz的带宽,可以挑选10~14 bit,采样率高达80 MHz的ADC。挑选fs=76.8 MHz=3.84 Mc/s×20,其间,3.84Mc/s是3GPP中规则的码片速率。由公式(1)可得,SNR为73.82 dB~97.90 dB,即便考虑实践中温度等影响,也能满意上述方针。

2.1.2 中心频率fo的挑选

中频采样由高速ADC完结,由于对信号在中频进行数字化。因而选用带通欠采样,用相对较低的采样速率反映信号特性,不只可以大大下降采样速率,一起还可以完结频谱下搬移的进程嘲。

带通采样中心频率fo的挑选有必要满意:

fo= fs(2n+1)/4 (2)

其间,n取满意 fs≥2B(B为频带带宽)的正偶数(若n为奇数,会呈现频谱反褶)。

由于选用f s=76.8 MHz,所以由公式(2)可得,取n=2时,中心频率fo为96 MHz。依据带通采样原理剖析可得,对中心频率fo为96 MHz,带宽B为5MHz的单载波WCDMA信号进行fs为76.8 MHz的采样,频谱散布如图3所示。

由图3可知,带通采样后,中心频率为19.2MHz的信号与中心频率为96 MHz的信号是等效的,因而,后续的DDC电路只需对中心频率为19.2MHz的带通信号进行处理即可。

值得注意的是,将信号带宽为5 MHz的射频信号模仿下变频至中心频率96 MHz,需经过抗混叠滤波器,滤除搅扰后,再进行高速A/D采样,以避免带通采样带来的频谱混叠。

2.2 数字下变频(DDC)

经高速ADC采样后的信号,以现有的芯片工艺水平,还无法及时进行运算处理,所以需求经过数字下变频(DDC)进行降速处理。

数字下变频由数字混频器、数字操控振动器(NCO)和抽取滤波部分组成。NCO发生的正交本振信号输入到数字混频器,与输人信号进行混频.经混频后的信号输出到抽取滤波器以滤除倍频重量和带外信号,并进行抽取处理。

2.2.1 数字操控振动器(NCO)

数字操控振动器在DDC中相对比较复杂。也是决议其功用的首要要素之一。NCO的方针是发生一个抱负的正弦波或余弦波,也便是发生一个频率可变的正弦波样本:

S(n)=cos[2nπ(fLO/fs)] (n=0,1,2……) (3)

其间,fLO为本振频率,fs为DDC输入信号的采样率。

如图4所示,NCO发生的正弦波样本与信号样本相乘,即可完结数字下变频功用,将数字中频信号下变频到零中频。

AD6634的NCO结构中的频率改换部分包括两个乘法器和一个32 bit复数数字操控振动器(NCO)。NCO作为正交本振,可发生fs/2至fs/232的振动信号,分辨率达fs/232。

操控字NCO_FREQ是一个32 bit无符号整数,为了将中心频率为fo的信号数字下变频到DC,该操控字NCO_RFEQ=232×mod(fo/fs),在本体系规划中,由带通采样的定论可知,挑选fo=19.2MHzfs=76.8 MHz, 所以得出NCO_FREQ=0x40000000。

2.2.2 积分梳状滤波器(CIC)及系数可编程滤波器(RCF)的设置

数字混频后的信号具有较高的数据速率。需求进行降速抽取处理,若要完结无失真的抽取。有必要规划高效的抽取滤波器以避免频率混叠。由各滤波器特性及本体系规划所需的抽取率D=76.8 MS/s/7.68 MS/s=10,选用rCIC2、CIC5和RCF三级级联抽取,完结总抽取因子D=10的降速处理。

榜首级rCIC2是一个二阶CIC抽取滤波器,作为重采样滤波器,rCIC2答应主时钟和输出速率有非整数倍联系。速率变化为分数方式:RrCIC2=L/M,对rCIC2,L/M应小于或等于1,即RrCIC2≤1。可选取抽取因子M=5,刺进因子L=2,因而,榜首级总的抽取因子D1=5/2。

第二级CIC5是一个比rC%&&&&&%2滤波特性更为峻峭的抽取滤波器,选取抽取因子D2=2。

RCF滤波器是乘积求和可编程系数抽取滤波器,数据存储器I-RAM、Q-RAM存储256个最新的分辨率为20 bit的复采样值。系数存储器C-RAM最多可以存储256个分辨率为20 bit的系数。每一个时钟用相同的系数分别对I和Q的一个抽头进行核算。最大的抽头数NTAPS可按下式核算:

NTAPS≤min[(fCLK×D3/fSAMPS),160] (4)

式中fSAMPS为输入RCF的数据速率,抽取因子D3为8 bit,可选1~256之间的恣意整数,本体系规划挑选D3=2。

上述级联滤波器的起伏呼应如图5所示,总的阻带衰减为60 dB左右,可以满意体系要求。

3 结束语

本文评论了自习惯前馈功率扩大器中依据软件无线电的数字接纳技能,构建了一个ADC+DDC+DSP硬件渠道(实践运用中,可用ARM替代DSP),以WCDMA体系中单载波的前馈功率扩大器的规划为例,依据要求对数字下变频及多级抽取滤波器进行优化规划,并经过仿真验证高速A/D采样和抽取滤波器的各项方针,已完结两路数字接纳通道的调试。规划中选用ADC+DDC的结构,既统筹了数据处理速度和精度,又提高了体系的适用性和扩展性。根本到达了自习惯前馈功率扩大器的自习惯操控算法所需信号接纳的要求。