现在正在研制、将来终将成为干流射频收发器的CMOS射频电路的体系结构和电路规划,规划实例将展现CMOS射频电路的杰出功能,并预示CMOS射频集成电路替代砷化镓和SiGe电路完成体系集成。

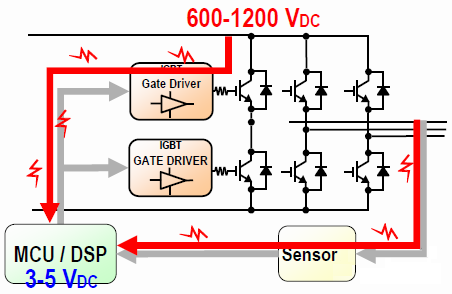

CMOS射频收发器原理:传统的射频收发电路遍及选用超外差结构,这种老练的体系结构需求选用二级混频和片外声外表滤波器,本钱高。正在研制的CMOS低中频或直接转化体系结构只需求选用一级混频,一起能节约片外声外表滤波器。可是直接转化的体系结构需求战胜直流失调等问题。选用CMOS射频收发电路的最大长处是可以和基带处理器(数字电路)及A/D、D/A转化器(混合信号电路)集成于一个芯片。单片集成的含射频、基带及模数、数模转化电路使电路可靠性好,功耗低和本钱低。单片集成CMOS无线通信电路是现在研讨热门,正走上商业化。

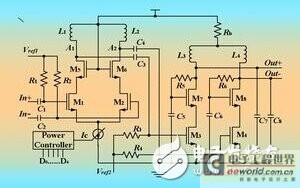

CMOS射频IC电路:选用直接转化的CMOS射频IC主要有低噪声扩大器、混频电路、功率驱动电路和频率归纳电路等射频单元组成。在射频范畴,咱们更多留意的是功率传输和扩大,其间低噪声扩大器的电路图如图所示。

它的核心技术是输入阻抗匹配和输出负载的规划,片上电感作为负载可以获得较高的增益和频率特性,为了按捺共模电平,差分结构的低噪声扩大器也常常选用。国内已有CMOS混频器报道选用吉尔布特乘法单元的混频电路如图3所示,混频器的功能主要是线性度,在进步线性度方面,现在有人选用电感负载和共源极电流耦合输入。功率驱动电路一般会选用二级功率扩大的电路,为了满意不同射频体系的需求和确保输出功率,功率驱动电路需求考虑增益控制电路和封装、连线及引脚的散布参数。为了得到低噪声时钟和低相位噪声的正交信号,选用片上电感和变容二极管的LC信频压控器及二分频正交信号发生器是一种好的挑选。

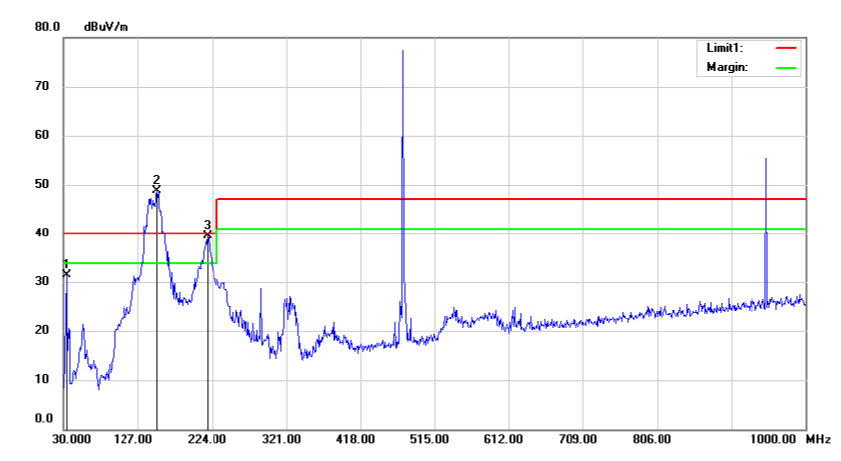

选用倍频VCO可以削减射频信号对VCO的牵引和VCO对信号的走漏。Sigma-Delta分数分频可以进一步下降VCO的相位噪声。低中频(2MHz中心频率)体系结构和直接转化的蓝牙、无线局域网和WCDMA射频电路。图6是单片集成的CMOS射频收发电路芯片相片,芯片左上角是正交时钟发生电路,右下角是功率扩大电路,右上角是复数滤波器。在深亚微米CMOS工艺线流片后,对各功能块进行测验,电路达到了规划的要求,可以满意蓝牙接纳芯片有必要的功耗和功能。