1、导言

跟着电子商务的开展,网络安全越来越重要。病毒和黑客进犯形成的丢失无法预算,防火墙、杀毒软件等防范办法都是依据软件的维护,并不能彻底牢靠地阻挠外界的进犯,因而迫切需求比传统产品更为牢靠的技能防护办法。GAP技能是一种依据硬件的维护技能。

2、体系作业原理

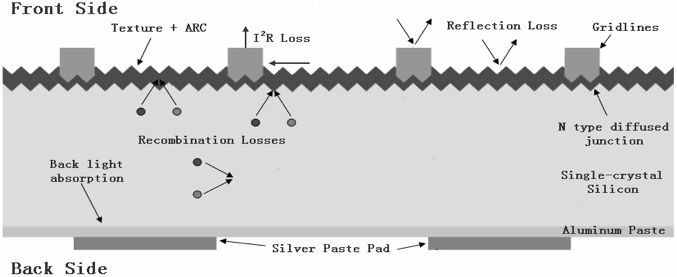

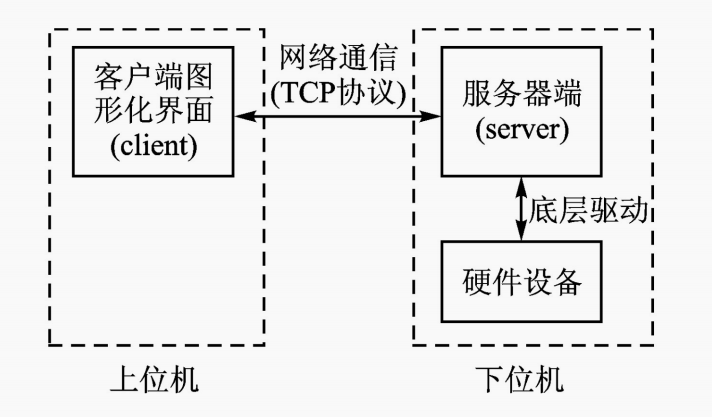

国内外快速开展的GAP技能以物理阻隔为根底,在确保安全性的一起,处理了网络之间信息交流的困难,然后突破了因安全性形成的运用瓶颈。GAP技能是经过专用硬件使2个或许2个以上的网络在不连通的状况下完结安全数据传输和资源共享的技能。它选用共同的硬件规划,确保在恣意时间网络间的链路层断开,阻断TCP/IP协议及其他网络协议,能够显著地进步内部用户网络的安全强度,与防火墙、侵略检测有很大的差异:防火墙、IDS技能从正面抗击黑客侵略,而GAP产品以进犯技能的物质根底即网络介质完结阻隔,使黑客技能无用武之地。2个网络(内部网络和外部网络)物理断开,但逻辑相连。GAP的结构如图1所示。

专用阻隔硬件与内外网处理单元构成一个GAP体系,阻隔硬件由纯电路构成,阻隔硬件中添加暂存区的规划,满意了数据传输的实时性和传输功率要求。笔者在GAP原理的根底上提出依据FPGA的专用阻隔硬件规划的新计划,并对关键技能进行了深入研究。

3、体系计划规划

3.1 体系结构

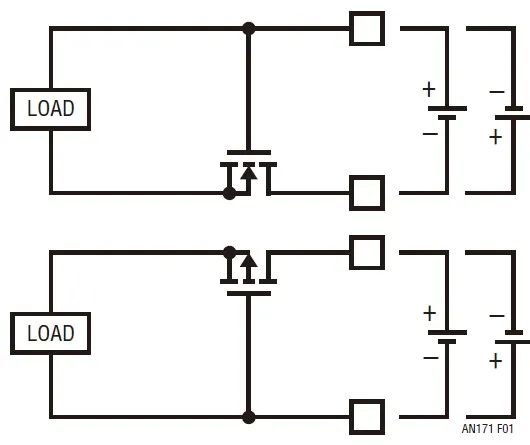

该体系首要由1个超大规模逻辑器材、2个68针P电缆SCSI接口和2个SDRAM构成,体系全体硬件结构如图2所示。

在该体系中,FPGA要集成中心操控器、SCSI协议操控器、SDRAM操控器模块,中心操控器从SCSI协议操控器取得二端处理单元的指令,履行相应的动作,如查看设备、读写数据等,并且将SCSI协议操控器与存储器阻隔,在任何时候,1个SCSI协议操控器只能与1个存储器构成通路。体系中的缓冲区由两片SDRAM构成,中心操控器经过调用SDRAM操控器IP核对其进行同步操作,从一片读数据的一起向另一片写数据,能够完结读写乒乓机制功用,有助于进步传输速度。专用阻隔硬件进行内外网之间许多数据的传输,为了确保高速和实时,选用68针的P电缆线,支撑16位宽SCSI。为了满意功用的需求,FPGA选用ALTERA公司的EPlK5OQC208-3,其逻辑门和引脚资源丰富,速度大于50 MHz。其首要特性如下:2.5 V中心电压,低功耗规划;208引脚,171个可用I/O口;内有l 728个逻辑单元和6个嵌入式RAM块。

3.2 SCSI协议操控器的规划

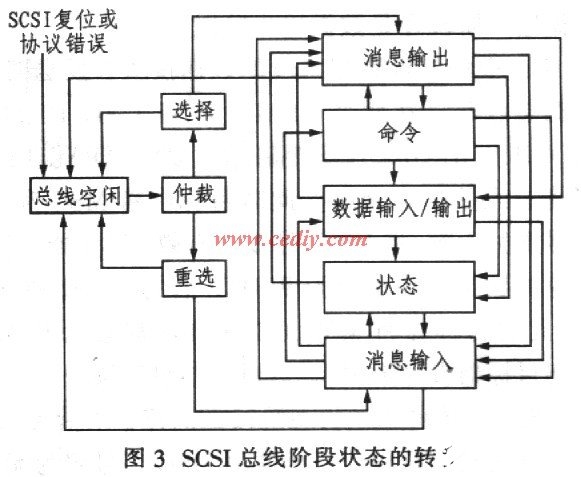

在SCSI总线上进行任何处理都需求8个总线阶段:闲暇阶段、裁定阶段、挑选阶段、重选阶段、音讯输入/输出阶段、数据输入/输出阶段、指令阶段、状况阶段。在任何时候,SCSI总线只能处于一个确认的总线阶段。阶段之闻的前后相关遭到严厉约束,也就是说并不是每个阶段后边都能够跟着任何阶段。图3示出了SCSI总线阶段状况的转化,如指令和数据阶段只能在音讯阶段之后呈现,相同,音讯阶段的后边有必要紧跟这两个阶段,而不是其他阶段。

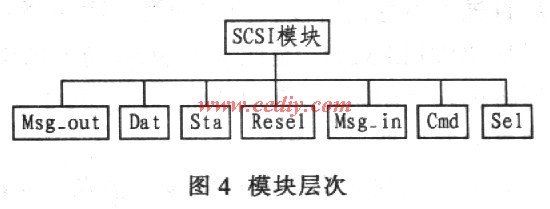

该协议操控器的规划严厉依照SCSI总线阶段转化进程,由以上剖析提出SCSI协议操控器的FP-GA完结计划:因为闲暇、裁定这两个总线阶段的机理简略,故将其直接放在SCSI模块中完结,其他每个阶段都有相对应的模块,整个体系软件由1个顶层模块和7个平行的底层模块构成。模块层次如图4所示。

SCSI模块有1个有限状况机,每个状况对应底层的1个模块,并用寄存器S_MODE的不同取指来表明不同模块,经过这个状况机完结阶段转化、音讯处理、指令解说、数据处理和状况处理等功用。

Sel模块处理挑选阶段的时序。启动器将信号BSY、SEL、ATN和启动器的ID号以及方针器的ID号置为有用,启动器随后开释BSY信号,经过200ms之后方针器将BSY信号置为有用,再过2个延

迟周期后启动器开释SEL信号并进入音讯阶段。

Resel模块处理从头选阶段的时序。启动器将信号BSY、SEI I/O和启动器的ID号以及方针器的ID号置为有用,启动器随后开释BSY信号。最多200ms之后方针器有必要将BSY信号置为有用作为呼应。

Msg_out模块处理音讯出阶段的时序。启动器将ATN置为有用,方针器将信号MSG和C/D信号置为有用,I/O信号为无效。这意味着接下来要进入的是音讯出相序,启动器将宣布16位宽传输音讯。发送完信息字节后,启动器将开释ATN信号,依据宣布的信息确认下一个阶段。

Cmd模块处理指令阶段的指令接纳时序。方针器在接纳到启动器80H的音讯后进入指令阶段。方针器需将MSG和I/O置为无效,将C/D置为有用,接纳完指令后,将依据指令判别接下来要进入的是数据输入阶段仍是数据输出阶段。

Dat模块处理数据阶段的数据接纳和发送时序。数据接纳时,在指令READ、TESI UNIT READY、INQUIRY、REQUEST、SENSE、READ CAPACITY后都将进入数据进相序。此刻方针器将MSG和C/D信号置为无效,将I/O信号置为有用。方针器将发送相应的数据。在指令为WRITE后将进入数据出阶段,此刻方针器将MSG、C/D和I/O都置为O,启动器向方针器发送数据,之后进入音讯阶段。

Status模块处理状况阶段的时序。在指令完结后将进入状况阶段,方针器将MSG信号置为无效,将C/D和I/O信号置为有用,并发送指令履行的状况是GOOD仍是CHECK CONDITON。状况阶段完毕后将进入音讯进阶段,向启动器阐明一个COM-MAND COMPLETED。至此一个SCSI拜访完毕。方针器将进入闲暇阶段,启动器将能够经过1个80 H的音讯触发别的一个拜访。

Msg_in模块处理音讯进阶段的音讯发送时序。方针器接纳到16位宽传输的音讯后将进入音讯进时序。方针器将MSG、C/D以及I/O都置为有用,并发送重复的信息。发送完后方针器将开释MSG信号,并依据音讯确认下一个阶段。

3.3 SDRAM IP核的运用

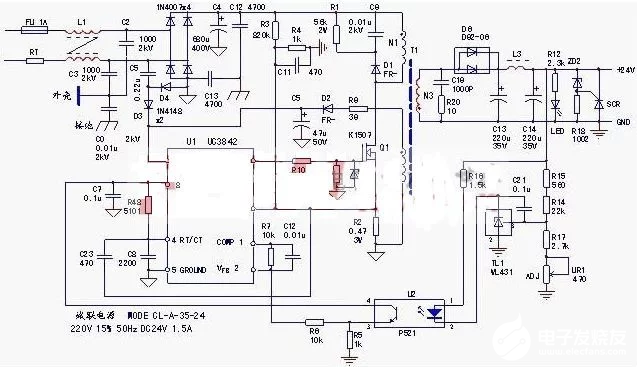

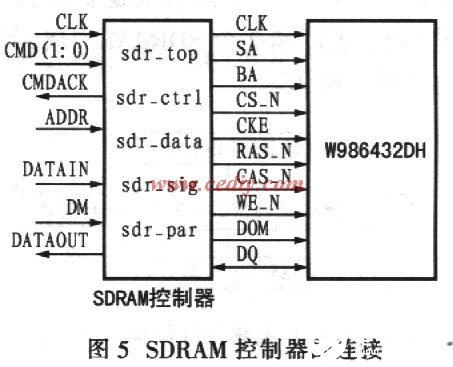

SDRAM是一种高速同步动态随机存储器,在嵌入式体系中,SDRAM因其价格低、体积小、速度快,容量大等长处而逐步成为一种干流器材,但SDRAM的操控逻辑杂乱,时序严厉,运用不方便,需求操控器供给正确指令来完结其初始化、读写和改写等作业。SDRAM操控器依据SDRAM的内部状况转化图进行规划,并且许多大公司都供给规范SDRAM操控器的IP核参阅规划。笔者选用了WINBOND公司的W986432DH型SDRAM,它选用512 Kx4x32位架构,由4个BANK构成,每个BANK对应4 M字节,按行和列寻址,W986432DH的引脚分为操控、地址和数据信号三类。其操控器选用Lattice公司的规范SDR SDRAM IP核,由4个底层模块sdr_ctrl、sdr_sig、sdr_data、sdr_par和顶层模块sdr_top组成,如图5所示。

8dr_ctrl模块依据SDRAM内部状况转化联系树立2个有限状况机和1个计数器,能发生正确的中间状况作为sdr_sig模块输入。sdr_sig模块发生面向SDRAM的操控、地址信号。sdr_data模块完结FPGA与SDRAM之间的数据传输。sdr_par模块完结猝发长度,延时节拍等参数设置,经过在该模块中设置不同的参数来满意不同的运用体系。

sdr__top将底层4个模块整组成1个能够调用的体系。整个IP核类似于黑匣子,不必详细了解其内部完结细节,只需了解左面操控信号的意义,对SDRAM的不同操作经过改动左面操控信号的状况即可。

4、 完毕语

本文提出了依据GAP技能的网络维护设备规划新计划,论述了首要模块的完结办法,限于篇幅不能给出详细细节和源代码。选用1个FPGA代替单片机和SCSI协议操控器,可削减电路数量,降低成本,便于晋级。

责任编辑:gt