在规划一个高功能数据收集体系时,勤勉的工程师细心挑选一款高精度ADC,以及模仿前端调理电路所需的其他组件。在几个星期的规划作业之后,履行仿真并优化电路原理图,为了赶工期,规划人员迅速地将电路板布局布线组合在一起。一个星期之后,第一个原型电路板被测验。出乎预料,电路板功能与预期的不一样。

这种情形在你身上发生过吗?

最优PCB布局布线关于使ADC到达预期的功能非常重要。当规划包括混合信号器材的电路时,你应该一直从杰出的接地组织下手,而且运用最佳组件放置方位和信号路由走线将规划分为模仿、数字和电源部分。

参阅途径是ADC布局布线中最要害的,这是因为一切转化都是基准电压的一个函数。在传统逐次迫临寄存器 (SAR) ADC架构中,参阅途径也是最灵敏的,其原因是基准引脚上会有一个到基准源的动态负载。

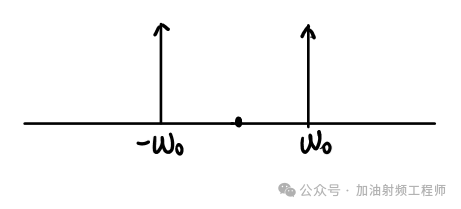

因为基准电压在每次转化期间被数次采样,高电流瞬变呈现在这个终端上,其间的ADC内部电容器阵列在这个方位位时被敞开和充电。基准电压在每个转化时钟周期内有必要坚持安稳,而且安稳至所需的N位分辨率,不然的话会呈现线性差错和丢码过错。

图1显现典型12位SAR ADC基准终端上的转化阶段期间的电流瞬变。

图1.12位SAR ADC基准引脚上的电流瞬变

因为这些动态电流,需求运用高质量旁路电容器(CREF)对基准引脚进行去耦合操作。此旁路电容器被用作一个电荷存储器,在这些高频瞬变电流期间供给瞬时充电。你应该将基准旁路电容器放置在尽量接近基准引脚的方位上,并运用较短的低电感衔接将他们衔接在一起。

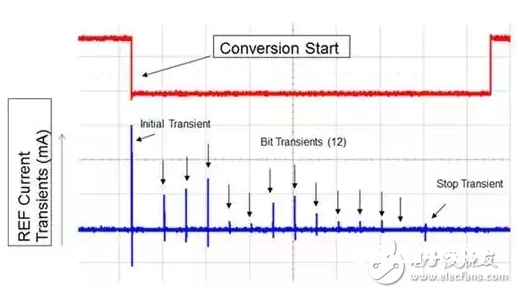

图2 显现了针对ADS7851,14位双ADC(具有两个独立电压基准)的电路板布局布线示例。

图2.具有两个独立内部电压基准的双ADC布局布线示例

在这个四层PCB电路板示例中,规划人员运用了一个坐落器材正下方的巩固接地平面,而且将电路板划分为模仿和数字部分,以使灵敏输入和基准信号远离噪声源。他用10μF,X7R级,尺度0805的陶瓷电容器 (CREF-x)来旁路REFOUT-A和REFOUT-B基准输出,以完成最优功能,而且将他们衔接至运用小型0.1 ?串联电阻的器材上,以坚持整体低阻抗和高频时的安稳阻抗;他还运用宽迹线来削减电感。

我强烈建议把CREF与ADC放置在同一层上。你还应该防止在基准引脚和旁路电容器之间放置导孔。ADS7851的每一个基准接地引脚都具有一个独自的接地衔接,而每个旁路电容器都有独自到接地途径的电感衔接。

假如你正在运用需求一个外部基准源的ADC,你应该尽量削减参阅信号途径中的电感-这个途径的起点为基准缓冲器输出到旁路电容器,直到ADC基准输入。

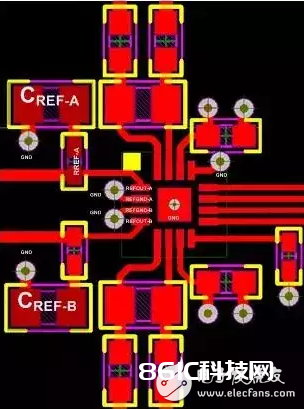

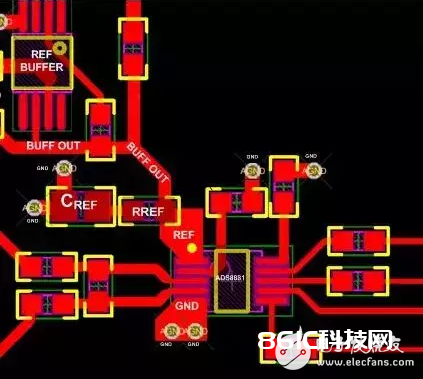

图3显现了运用外部基准和缓冲器的一个18位SAR ADC ADS8881的布局布线示例。

图3. 具有一个外部基准和缓冲的ADC布局布线示例

经过将电容器放置在引脚的0.1英寸规模以内,而且将其与宽度为20密耳的迹线和多个尺度为15密耳的接地导孔相连,规划人员将基准电容器和REF引脚之间的电感坚持在少于2nH的水平上。我引荐运用一个额外电压至少为10V的单个、10uF,X7R级,尺度0805的陶瓷%&&&&&%器。

基准缓冲器电路到REF引脚的迹线长度被坚持尽可能的短,以保证快速安稳呼应。

REF引脚的正确去耦合关于完成最优功能非常要害。此外,在参阅途径中坚持低电感衔接使得基准驱动电路在转化期间坚持安稳,使你向取得所需的作用又迈进了一步。