相似嵌入式 C/C++/OpenCL 运用开发的体会

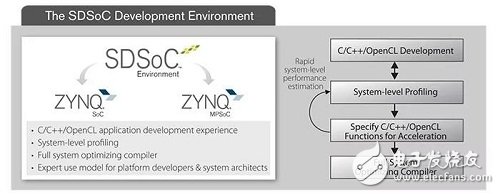

SDSoC 开发环境可为异构 Zynq SoC 及 MPSoC 布置供给相似嵌入式 C/C++/OpenCL 运用的开发体会,其间包含简略易用的 Eclipse IDE 和归纳规划环境。SDSoC 供给业界首款 C/C++/OpenCL 全体系优化编译器,可完结体系级的特性描绘、可编程逻辑中的主动软件加快、主动体系衔接生成以及可加快编程的各种库。此外,它还可协助最终用户及第三方渠道开发人员快速界说、集成和验证体系级解决方案,为其最终用户完结定制化编程环境。

Xilinx OpenCV 库现已推出,包含 50 多项硬件优化 OpenCV 功用,包含 Gausian、 Median、Bilateral、Harris corner、 Canny edge detecTIon、HoG、ORB、SVM、LK OpTIcal Flow 及更多;

简略易用的 Eclipse IDE 可用于开发支撑嵌入式 C/C++/OpenCL 运用的完好 Zynq SoC 和 MPSoC;

只需一点按钮,就可对可编程逻辑 (PL) 中的功用进行加快;

支撑作为方针 OS 的裸机、Linux 与 FreeRTOS。

体系级的特性描绘

快速功用预算与面积预算可在几分钟内完结,包含 PS、数据通信以及 PL

高速缓存、存储器以及总线利用率的主动运行时外表

可完结最佳整体体系架构的快捷生成与探究

全体系优化编译器

可将 C/C++/OpenCL 运用编译成全功用 Zynq SoC 与 MPSoC 体系;

可在生成 ARM 软件与 FPGA 比特流的可编程逻辑中完结主动功用加快;

不仅可优化体系衔接,并且还支撑吞吐量、时延以及面积权衡的快速体系探究。

面向渠道开发人员的专家级运用模型

经过业经验证办法完结的方针定制电路板可将现有的 Vivado 项目及软件项目转换成 SDSoC;

面向 Zynq 开发板的开发板支撑包 (BSP) 现已开端供给,包含 ZC702、ZC706 以及第三方开发板和体系级模块 (SoM)(包含 Zedboard、Microzed、Zybo、Avnet 嵌入式视觉套件、视频和成像套件以及 SDR 套件等)。请单击“开发板与模块”检查全面的 BSP 列表。