去耦电容是电路中装设在元件的电源端的电容,此电容能够供应较安稳的电源,一起也能够下降元件耦合到电源端的噪声,直接能够削减其他元件受此元件噪声的影响。

在电子电路中,去耦电容和旁路电容都是起到抗搅扰的效果,电容所在的方位不同,称号就不相同了。关于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除目标,把前级带着的高频杂波滤除,而去耦(decoupling)电容也称退耦电容,是把输出信号的搅扰作为滤除目标。去耦电容用在扩大电路中不需求沟通的当地,用来消除自激,使扩大器安稳作业。

去耦电容

去耦电容主要是去除高频如RF信号的搅扰,搅扰的进入方法是经过电磁辐射。而实践上,芯片邻近的电容还有蓄能的效果,这是第二位的。你能够把总电源看作密云水库,咱们大楼内的家家户户都需求供水,这时分,水不是直接来自于水库,那样间隔太远了,等水过来,咱们现已渴的不行了。

实践水是来自于大楼顶上的水塔,水塔其实是一个缓冲器的效果。假如微观来看,高频器材在作业的时分,其电流是不接连的,并且频率很高,而器材VCC到总电源有一段间隔,即使间隔不长,在频率很高的状况下,阻抗Z=i*wL+R,线路的电感影响也会十分大,会导致器材在需求电流的时分,不能被及时供应。而去耦电容能够补偿此缺乏。

这也是为什么许多电路板在高频器材VCC管脚处放置小电容的原因之一(在vcc引脚上一般并联一个去耦电容,这样沟通重量就从这个电容接地。)

去耦电容的容值核算和布局布线

有源器材在开关时发作的高频开关噪声将沿着电源线传达。去耦电容的主要功能便是供应一个部分的直流电源给有源器材,以削减开关噪声在板上的传达,和将噪声引导到地。 去耦电容的容值核算

去耦的初衷是:不管IC对电活动摇的规则和要求怎样都要使电压限值保持在规则的答应差错规模之内。 运用表达式:

C·⊿U=I·⊿t

由此可核算出一个IC所要求的去耦电容的电容量C。 ⊿U是实践电源总线电压所答应的下降,单位为V。 I是以A(安培)为单位的最大要求电流; ⊿t是这个要求所保持的时刻。

xilinx公司引荐的去耦电容容值核算方法: 引荐运用远大于1/m乘以等效开路电容的电容值。

此处m是在IC的电源插针上所答应的电源总线电压改变的最大百分数,一般IC的数据手册都会给出详细的参数值。 等效开路电容界说为:

C=P/(f·U^2) 式中:

P——IC所耗散的总瓦数; U——IC的最大DC供电电压; f——IC的时钟频率。

一旦决议了等效开关电容,再用远大于1/m的值与它相乘来找出IC所要求的总去耦电容值。然后还要把成果再与衔接到相同电源总线电源插针的总数相除,最终求得装置在每个衔接到电源总线的一切电源插针邻近的电容值。 去耦电容挑选不同容值组合的原因:

在去耦电容的规划上,一般选用几个不同容值(一般相差二到三个数量级,如0.1uF与10uF),根本的起点是涣散串联谐振以取得一个较宽频率规模内的较低阻抗。

电容谐振频率的解说:

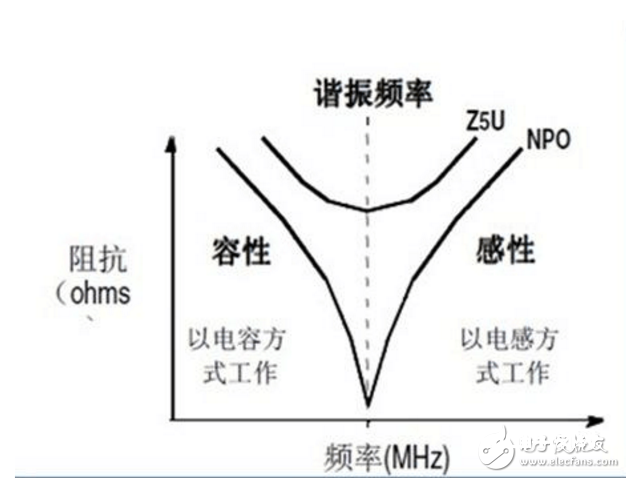

由于焊盘和引脚的原因,每个电容都存在等效串联电感(ESL),因而本身会构成一个串联谐振电路,LC串联谐振电路存在一个谐振频率,跟着电力的频 率不同,电容的特性也随之改变,在作业频率低于谐振频率时,电容整体呈容性,在作业频率高于谐振频率时,电容整体呈理性,此刻去耦电容就失掉了去耦的效 果,如下图所示。因而,要进步串联谐振频率,就要尽或许下降电容的等效串联电感。

电容的容值挑选一般取决于电容的谐振频率。

不同封装的电容有不同的谐振频率,下表列出了不同容值不同封装的电容的谐振频率:

需求留意的是数字电路的去耦,低的ESR值比谐振频率更为重要,由于低的ESR值能够供应更低阻抗的到地通路,这样当超越谐振频率的电容出现理性时仍能供应满足的去耦才能。 下降去耦电容ESL的方法

去耦电容的ESL是由于内部活动的电流引起的,运用多个去耦电容并联的方法能够下降电容的ESL影响,并且将两个去耦电容以相反走向放置在一起,从 而使它们的内部电流引起的磁通量彼此抵消,能进一步下降ESL。(此方法适用于任何数目的去耦电容,留意不要侵略DELL公司的专利)

IC去耦电容的数目挑选

在规划原理图的时分,常常遇到的问题是为芯片的电源引脚规划去耦电容,上面现已介绍了去耦电容的容值挑选,可是数目挑选怎样确认呢?理论上是每个电源引脚最好分配一个去耦电容,可是在实践状况中,却常常看到去耦电容的数目要少于电源引脚数目的状况,如freescale供应的iMX233的PDK原 理图中,内存SDRAM有15个电源引脚,可是去耦电容的数目是10个。 去耦电容数目挑选依据:

在布局空间答应的状况下,最好做到一个电源引脚分配一个去耦电容,可是在空间缺乏的时分,能够恰当削减电容的数目,详细状况应该依据芯片上电源引脚的详细散布决议,由于厂家在规划IC的时分,常常是几个电源引脚在一起,这样能够共用去耦电容,削减去耦电容的数目。

电容的装置方法

电容的摆放

关于电容的装置,首先要说到的便是装置间隔。容值最小的电容,有最高的谐振频率,去耦半径最小,因而放在最接近芯片的方位。容值稍大些的能够间隔稍 远,最外层放置容值最大的。可是,一切对该芯片去耦的电容都尽量接近芯片。别的的一个原因是:假如去耦电容离IC电源引脚较远,则布线阻抗将减小去耦电容 的效能。

还有一点要留意,在放置时,最好均匀散布在芯片的四周,对每一个容值等级都要这样。一般芯片在规划的时分就考虑到了电源和地引脚的摆放方位,一般都是均匀散布在芯片的四个边上的。因而,电压扰动在芯片的四周都存在,去耦也有必要对整个芯片所在区域均匀去耦。

电容的装置

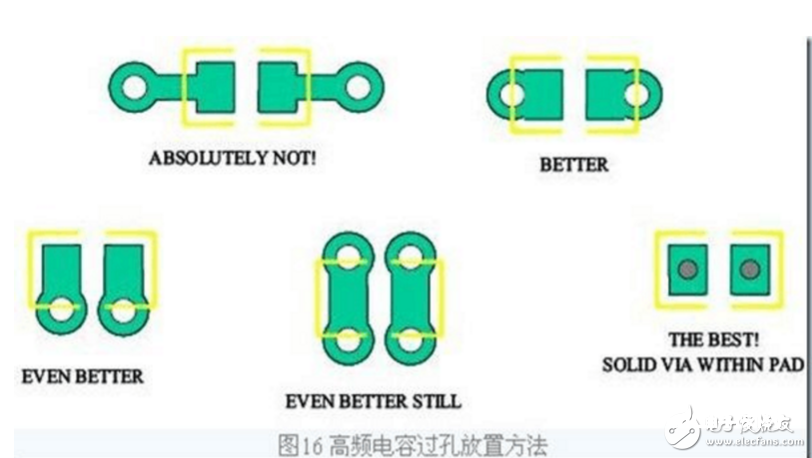

在装置电容时,要从焊盘拉出一小段引出线,然后经过过孔和电源平面衔接,接地端也是相同。放置过孔的根本原则便是让这一环路面积最小,进而使总的寄生电感最小。图16显现了几种过孔放置方法。

榜首种方法从焊盘引出很长的引出线然后衔接过孔,这会引进很大的寄生电感,必定要防止这样做,这时最糟糕的装置方法。

第二种方法在焊盘的两个端点紧邻焊盘打孔,比榜首种方法路面积小得多,寄生电感也较小,能够承受。

第三种在焊盘旁边面打孔,进一步减小了回路面积,寄生电感比第二种更小,是比较好的方法。 第四种在焊盘两边都打孔,和第三种方法比较,相当于电容每一端都是经过过孔的并联接入电源平面和地平面,比第三种寄生电感更小,只需空间答应,尽量用这种方法。

最终一种方法在焊盘上直接打孔,寄生电感最小,可是焊接是或许会出现问题,是否运用要看加工才能和方法。

引荐运用第三种和第四种方法。

需求着重一点:有些工程师为了节约空间,有时让多个电容运用公共过孔。任何状况下都不要这样做。最好想方法优化电容组合的规划,削减电容数量。

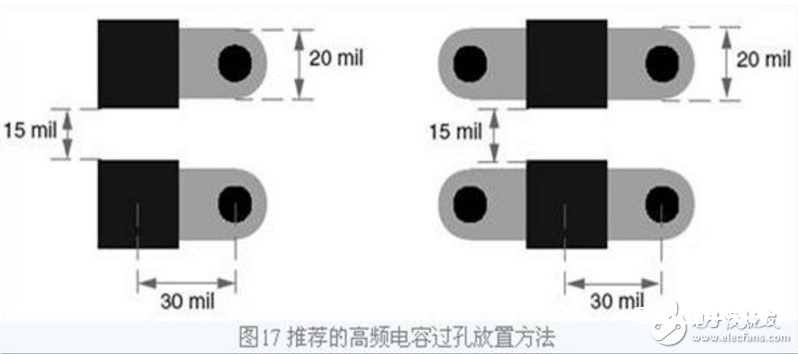

由于印制线越宽,电感越小,从焊盘到过孔的引出线尽量加宽,假如或许,尽量和焊盘宽度相同。这样即使是0402封装的电容,你也能够运用20mil宽的引出线。引出线和过孔装置如图17所示,留意图中的各种尺度。

关于大尺度的电容,比方板级滤波所用的钽电容,引荐用图18中的装置方法。留意:小尺度电容制止在两个焊盘间打孔,由于简单引起短路。

电容的去耦半径

电容去耦的一个重要问题是电容的去耦半径。大大都材料中都会说到电容摆放要尽量接近芯片,大都材料都是从减小回路电感的视点来谈这个摆放间隔问题。 的确,减小电感是一个重要原因,可是还有一个重要的原因大大都材料都没有提及,那便是电容去耦半径问题。假如电容摆放离芯片过远,超出了它的去耦半径,电 容将失掉它的去耦的效果。

了解去耦半径最好的方法便是调查噪声源和电容补偿电流之间的相位联系。当芯片对电流的需求发作改变时,会在电源平面的一个很小的部分区域内发作电压 扰动,电容要补偿这一电流(或电压),就有必要先感知到这个电压扰动。信号在介质中传达需求必定的时刻,因而从发作部分电压扰动到电容感知到这一扰动之间有 一个时刻推迟。相同,电容的补偿电流抵达扰动区也需求一个推迟。因而必定形成噪声源和电容补偿电流之间的相位上的不一致。

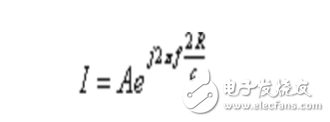

特定的电容,对与它自谐振频率相同的噪声补偿效果最好,咱们以这个频率来衡量这种相位联系。设自谐振频率为f,对应波长为λ,补偿电流表达式可写为:

其间,A是电流起伏,R为需求补偿的区域到电容的间隔,C为信号传达速度。

当扰动区到电容的间隔到达λ/4时,补偿电流的相位为π,和噪声源相位刚好差180度,即彻底反相。此刻补偿电流不再起效果,去耦效果失效,补偿的 能量无法及时送达。为了能有用传递补偿能量,应使噪声源和补偿电流的相位差尽或许的小,最好是同相位的。间隔越近,相位差越小,补偿能量传递越多,假如距 离为0,则补偿能量百分之百传递到扰动区。这就要求噪声源间隔电容尽或许的近,要远小于λ/4。实践使用中,这一间隔最好控制在λ/40-λ/50之间, 这是一个经历数据。

例如:0.001uF陶瓷电容,假如装置到电路板上后总的寄生电感为1.6nH,那么其装置后的谐振频率为125.8MHz,谐振周期为 7.95ps。假定信号在电路板上的传达速度为166ps/inch,则波长为47.9英寸。电容去耦半径为47.9/50=0.958英寸,大约等于 2.4厘米。

本例中的电容只能对它周围2.4厘米规模内的电源噪声进行补偿,即它的去耦半径2.4厘米。不同的电容,谐振频率不同,去耦半径也不同。关于大电 容,由于其谐振频率很低,对应的波长十分长,因而去耦半径很大,这也是为什么咱们不太重视大电容在电路板上放置方位的原因。关于小电容,因去耦半径很小, 应尽或许的接近需求去耦的芯片,这正是大大都材料上都会反复着重的,小电容要尽或许近的接近芯片放置。

综上所述,在挑选去耦电容时,需求考虑的要素有电容的ESR、ESL值,谐振频率,布局时要留意依据IC电源引脚的数目和周围布局空间决议去耦电容数目,依据去耦半径决议详细的布局方位。