在比如核磁共振成像 (MRI)、超声波、CT 扫描仪、数字 X 射线等医疗运用中,常常需求运用有许多通道的模数转换器 (ADC) 对许多数据采样。用串行接口来获取采样数据可削减 ADC 与 FPGA 的引脚数。此外,高速串行接口布线可节约电路板空间。由于电路板资源十分稀缺,FPGA 引脚也是十分名贵的资源,所以与并行接口比较,串行数据转换器接口的优势是明显的。今日,有两种适用于高速数据转换器的串行接口可供挑选。第一种挑选是串行时钟-数据-帧 (CDF) 接口,该接口整合了串行化 LVDS (低压差分信号) 数据流以及差分时钟和帧时钟,其间差分时钟用于精确地搜集数据,帧时钟用于树立数据采样的边缘。第二种挑选是选用 JESD204 标准,在该标准中,时钟嵌入到 Gbps 级高速两线串行数据流中。这两种接口均有各自的优缺陷。由于用来驱动高速 JESD204 接口的电流形式逻辑 (CML) 对需求较大的功率,所以串行 LVDS 是完结功率较低且有许多通道的便携式规划的首选。但是在串行 LVDS 不适用的场合,JESD204 接口就可以发挥作用。

串行LVDS 的优势

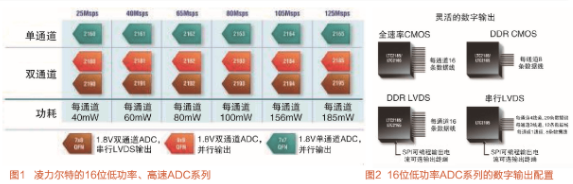

串行 LVDS 输出格局削减了 ADC 和 FPGA 之间所需的数字 I/O 数量,节约了 FPGA 引脚、电路板面积和本钱。此外,经过在数据转换器上选用串行接口,数据转换器所需的引脚数量也大大削减了,然后可完结尺度小得多的封装尺度。这种优势在有许多通道的规划中得到了充沛的闪现。选用串行 LVDS 接口仍是选用并行接口则取决于运用能否接受较大的功耗,以及 FPGA 是否有才能处理高速数据流。LTC2195 是一款 16 位、125Msps 双通道 ADC,具串行 LVDS 输出,每通道功耗仅为 216mW。不过,与运用双通道并行输出版别 LTC2185 (参见图 1 中的完好产品系列图) 比较,串行 LVDS 接口每通道多耗费 31mW 功率。这个 16 位高速 ADC 系列供给了杰出的 76.8dB 基带 SNR 功用以及 90dB SFDR,一同在运用 1.8V 电源时,功耗十分低。

图 1:凌力尔特的 16 位低功率、高速 ADC 系列

就高速 ADC 而言,和谐数据时钟、帧时钟和数据时,一般发送器和接收器均需求一个锁相环 (PLL),以正确和谐数据时钟。在 GHz 速率时,这种和谐十分困难,并且数据传输速率首要遭到接收器的约束。终究,在高于 1GHz 时,一般不选用这种 6 线串行发送办法,然后约束了 ADC 的速率或说约束了 ADC 的分辨率。

就一个 16 位高速 ADC 而言,这就将采样频率约束到 62.5Msps。为了完结更高的采样频率,每个 ADC 通道可以选用两个或 4 个“线道”。运用两“线道”时,串行数据速率折半,奇数位和偶数位分隔,进入两个串行数据流差分对。选用双“线道”形式时,16 位 125Msps ADC 将供给 1Gbps 的串行输出数据速率。LTC2195 串行 LVDS 系列多供给一种 4“线道”形式,答应低得多的 500Mbps 数据传输速率,在该形式时,每通道运用 4 个差分对,总共有 20 条线,其间包含差分帧和时钟对 (参见图 2)。这答应与较贱价、较低速的 FPGA 衔接。为了正确理解所需的数字输出线数量,再看一下选用并行 LVDS 输出的状况,这时每通道将需求 32 条线。今日,市面上现已有具双数据速率 (DDR) LVDS 输出的 ADC 了,这类 ADC 每通道仅需求 16 条线。运用这种器材,输出端的数据速率将是采样频率的两倍。比如 LTC2185 等双通道 16 位 ADC 还供给可供挑选的 DDR CMOS 输出,这将所需数据线的数量削减到每通道仅为 8 条。当考虑运用比如 16 位 125Msps LTC2165 这类单通道高速 ADC 时,供给串行 LVDS 接口就不再有含义了,由于在所需数据线的数量上没有不同。DDR CMOS 选用 8 条并行输出线,而两“线道”串行 LVDS (由于采样率高于 62.5Msps,所以需求) 也选用 8 条线 (4 条线用于数据,4 条线用于数据时钟和帧时钟)。此外,串行 LVDS 增大了设备的功耗,这是便携式运用忧虑的一个问题。

就高通道密度医疗运用而言,凌力尔特现在供给 8 通道 14 位 125Msps ADC LTM9011-14,这款新的低功率器材选用紧凑型 140 引脚 11.25mm x 9mm BGA 封装,供给 73.1dB 的信噪比 (SNR) 功用以及高于 -90dBc 的通道阻隔。为了完结最佳功用,也为了节约空间,该器材还接近芯片集成了一切必要的旁路电容。在 125Msps 时,功耗仅为每通道 140mW。80Msps (LTM9009-14) 和 105Msps (LTM9010-14) 版别每通道别离耗费 94mW 功率和 113mW 功率,更低采样率、更低功耗的版别正在开发之中。针对便携式运用,LTM9011 系列供给可将功耗降至仅为 2mW 的休眠形式。LTM9011 供给串行 LVDS 格局,并面向高于 62.5Msps 的采样率供给双“线道”输出形式。LTM9011 8 通道系列以低功率、14 位和 12 位、25Msps 至 125Msps 串行 LVDS 4 通道 (LTC2175) 及双通道 (LTC2268) ADC 系列为根底,具相似的功用特色 (参见图 3)。新的美国出口管理法令现已改变了这些器材的分类,这些器材的出口操控分类号 (ECCN#) 现已从3A001 改为不那么严厉的 ECCN# 3A991 了。这些器材以每 Msps 仅超越 1mW 的超低功耗,供给了无与伦比的功用,可坚持许多医疗运用的便携性。如需取得不受美国出口控制法令约束的高速 ADC 产品完好列表,请拜访:www.linear.com.cn/hsadc_nolicense。

图 3:具串行 LVDS 输出的 14 位 / 12 位、25Msps 至 125Msps 四通道 / 双通道 ADC 系列

关于在 ADC 和逻辑器材之间布设高速数字线的应战,数字规划师或许太了解了。规划师有必要极端小心肠保证在高速走线之间有满足的距离,以及保证数字信号不跨过模仿鸿沟。布局欠安会导致数字开关噪声反应回 ADC 的模仿输入,然后引起体系整体功用下降。LTM9011 系列供给了直通式引出脚装备,然后削减了布设数据 I/O 线所需占用的电路板面积,并简化了布局,可最大极限地削减与数字反应相关的问题 (参见图 4)。其他选项包含下降数字反应的数据输出随机函数发生器、7 个可编程 LVDS 输出电流值、内部 100Ω LVDS 输出终端电阻器、以及数字输出测验码型。这些装备可以十分容易地经过 SPI 或硬连线设定,以完结更小的操作形式组。

图 4:14 位、 80Msps 至 125Msps、 8 通道 ADC 供给直通式引出脚,以易于布设至 FPGA 的走线

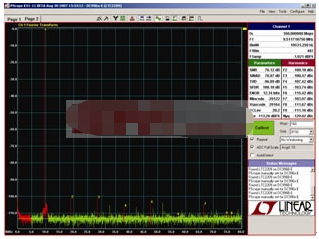

凌力尔特公司供给的一切这些串行 LVDS ADC 都可用装备了 VITA-57 FPGA Mezzanine 衔接器 (FMC) 的演示版进行评价。运用强壮的 PScopeTM QuikEvalTM II 软件,工程师还能评价多个并行输入通道的功用。PScope 软件是凌力尔特公司的高速 ADC 评价软件。就一个简略的程序而言,它用几秒钟就能完结杂乱的核算。PScope 软件使工程师能快速和容易地评价信噪比 (SNR)、无寄生动态规模 (SFDR)、总的谐波失真 (THD) 以及高速 ADC 的其他要害参数。PScope 这一东西还可以履行更杂乱的核算,如核算两个单音测验的互调失真,或许核算按动按钮时扩展频谱信号的相邻通道功率比 (ACPR)。它还支撑比如 LTM9011 等多通道 ADC,然后答应一同丈量 8 个 ADC 通道。

图 5 是一个屏幕截图,显现了 PScope 数据搜集与剖析软件东西的强壮功用。

图 5:凌力尔特的 PScope 数据转换器剖析软件

JESD204 高速串行接口

8B/10B 编码最初是由 IBM 于 1980 年创造的,该编码无需帧时钟和数据时钟,这使得在高于 2GHz 的串行数据速率时,能完结单条传输线对通讯。8B/10B 编码的共同特性答应将数据时钟嵌入于数据自身之中,并经过初始帧同步,用 COMMA (逗号) 字符与帧一同坚持。为了以标准化方法完结这种编码的数据转换器接口,JEDEC 标准 JESD204 界说了所需的协议和电特性,这使得新一代更快、更精确的串行 ADC 得以完结,如凌力尔特公司具 77.6dB SNR 和 100dB SFDR 的 16 位、105Msps ADC LTC2274。JESD204 接口使用许多高功用 FPGA 上供给的 SerDes 端口,腾出了通用 I/O 用于其他功用。缺陷是 ADC 上的电流形式逻辑驱动器耗费比 LVDS 驱动器大得多的电流。别的,还有必要有满足的 SerDes 端口可用,以包容一切 ADC 接口。

与典型 6 线串行传输比较的优势

8B/10B 编码数据因其行程长度有限,故而适合于时钟恢复电路。别的,由于它选用 DC 平衡,因而还可习惯 AC 耦合。8B/10B 编码需求进行从一个 8 位组至一个 10 位代码组的改换。在每个代码组中,“1”和“0”的数量之差从不超越 2。经过监督接连代码组中的“1”和“0”的数量,可以核算出运转差异。发送器和接收器使用该差异对数据编码和解码。关于每个输入八位组,存在两种或许的 10 位输出代码。挑选哪种代码进行传送取决于运转差异,并旨在坚持“1”与“0”的均匀数量持平。8B/10B 编码的这种特性可保证信号的 DC 偏移为零。当数据被编码时,将对其进行串行化和传送 (始于第一个代码组的“0”位)。JESD204 标准要求第一个代码组对应于数据的最高有用字节。第二个代码组对应于数据的最低有用字节。这两个代码组组合起来构成一个数据帧,然后构成一个样本。一个 16 位 ADC 将被编码为两个 10 位代码组,然后与采样速率相乘以确认两线式串行数据流的位速率。16-bit 105Msps LTC2274 在编码之后可发生一个以 2.1Gbps 速率进行传输的串行数据流。在此速度下,8B/10B 编码及其共同特性使得可以经过一个两线式接口可靠地传输串行数据。

JESD204串行接口关于本钱灵敏型运用最有含义,在这类运用中,FPGA 引脚数量决议了规划的本钱。医疗成像等多通道运用将从引脚数量削减中获益,由于易于布线并额定节约了空间。

定论

挑选串行 LVDS 仍是挑选 JESD204 接口标准,将取决于 FPGA上 SerDes 端口的功耗要求和可用性。假如考虑到便携性,那么串行 LVDS 最适合采样率高达 125Msps、分辨率高达 16 位的多通道 ADC。

责任编辑:gt