FPGA工程师都知道,Verilog代码绝大部分都是always句子,结构基本上都是共同的,为了削减重复性的作业,让工程师专心于规划完成,明德扬精心制作了常用模板,只需你安装好明德扬供给的GVIM,就能运用这些模板了。

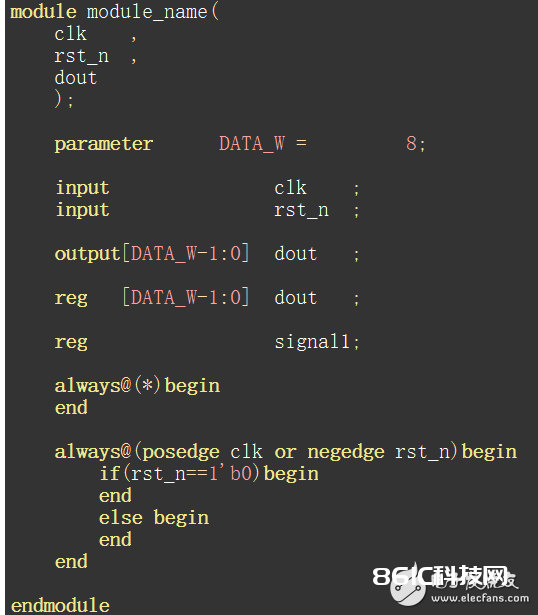

1.时序逻辑的模板

在GVIM输入“Module”并回车,如下图所示

就能得到下面的时序逻辑的模板。

模块的模板包含了输入输出信号列表、信号界说,组合逻辑和时序逻辑等,这是一个模块常用的组件。学员只需求了解各个部分的含义,按要求来填空就可以,彻底没有必要去记住。我看许多学员刚开始学习时,花费很多的时刻去记住、背熟模块,这是没有含义的。

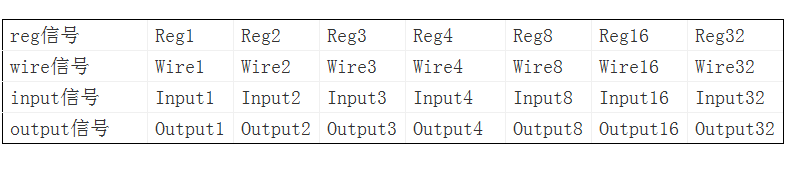

2.输入“Reg”并回车。

就能得到单比特的reg信号界说

![]()

3.输入“Reg2”并回车

![]()

就能得到2比特的reg信号界说

![]()

4.输入“Reg8”并回车

![]()

就能得到8比特的reg信号界说

![]()

相似的方便指令有:

要运用上面方便指令,需求明德扬的配置文件,欢迎重视明德扬大众号“fpga520”,或群97925396讨取。标语:多用模板,削减回忆,专心规划。