飞控核算机是现代导弹制导与操控体系的中心设备,其功用的好坏直接联系到准确制导的精度和杀伤方针的概率。近年来舵机、扶引头、惯导等弹载设备日益向着数字化方向开展,因而规划一种能兼容多数字式设备的通用飞控核算机渠道尤为重要。传统的单处理器中心飞控核算机难以在多通道异步数据收发的一起确保数据处理速度,难以满意现代导弹的要求。本文提出了一种依据DSP+FPGA结构,对外接口为422的通用数字飞控核算机渠道。此渠道能充分发挥DSP的运算速度,完结飞控算法。选用依据FPGA的双RAM缓冲机制,能很好地处理异步串行数据实时同步数据处理问题,满意飞控体系需求。

1 规划思维和作业原理

1.1 规划思维

关于单DSP中心的飞控核算机,要收发多路异步串行数据就会占用多路中止,导致中止呼应不及时形成数据丢掉。一起多路中止也会影响到数据传输的实时性。飞控核算机对数据的完好性和实时性要求较高,传统单DSP中心不能满意弹上多数字式设备的要求。因为FPGA具有强壮的并行处理才能,所以选用添加一片FPGA用于异步串行数据的收发的办法补偿单DSP中心的缺点。DSP+FPGA的结构能将DSP从繁琐的外部接口办理中解放出来,充分发挥DSP的运算优势,进步运算功率的一起易于保护和扩展。

1.2 飞控核算机作业原理

飞控核算机的一般作业进程如下:飞控核算机上电之后进行自检,向载机宣布“导弹存在”指令。飞控核算机接纳载机的装订信息,完结初始对准,而且向载机宣布“答应发射”指令。当扶引头探测到方针向飞控核算机宣布扶引数据时,飞控核算机向载机宣布“方针截获”指令。载机经过判别决议计划,向飞控核算机给出“发射”指令。发射之后,飞控核算机进行飞翔时刻计时,并开端依照已有的操控率,结合惯导和扶引头输入进行飞控解算,得出四路舵机操控信号信号,操控导弹运动;并将接纳到惯导数据、扶引头数据、舵控量等内容组成遥测信息,发送给观测人员。

2 结构和硬件规划

依据飞控核算机作业原理,它具有以下功用:

能够收发装订、惯导、扶引头和遥测等数据;

能够完结扶引率,完结导航数据解算功用;

能够操控执行机构——舵机。

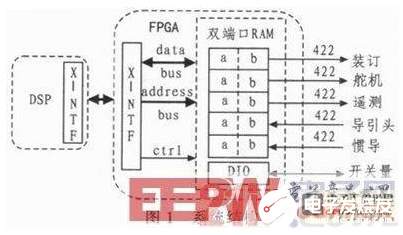

RS422通讯协议具有抗搅扰才能强,传输间隔远,完结简略的特色,现已被各种数字设备广泛选用。本弹载机对外通讯接口均选用422通讯协议。依据飞控核算机的功用能够得出,此体系至少应该包含装订、惯导、扶引头、遥测数据的收发和舵机操控5路数据通讯。因为弹载机作业时收发“导弹存在”、“方针截获”、“答应发射”等开关量,还需求开关量的输入输出。故FPGA对外的接口共包含5路RS422和8位DIO通讯接口。体系结构简图如图1所示(图中XINTF接口和双端口RAM的阐明见本文第4部分)。

DSP选用TI公司的高功用浮点处理器,150 MHz主频,功用比较于2812有大幅提高,广泛运用于操控体系。FPGA选用ALTERA的Cyclone II系列,彻底满意运用需求。DSP+FPGA组成的最小体系首要由电源、复位电路、晶振、烧写接口等部分组成。电源芯片选用TPS7 67D301PWP,能够为DSP供给3.3 V的作业电压和1.9 V的内核电压;FPGA的内核电压由ASM1117-1.2稳压得到。DSP复位芯片选用MAX809S,晶振选用30 MHz的有源晶振;FPGA用50 MHz的有源晶振。装备芯片选用EPCS1,容量为1M bits,用AS形式烧写。

对外的RS422接口选用MAX3491协议芯片完结。MAX3491将FPGA的TTL电平转化成422差分电平,和弹上设备通讯。因为FPGA引脚的驱动才能弱,因而对外的8位DIO选用74LN244芯片,增强驱动才能。

3 软件规划

DSP经过XINTF接口与FPGA通讯。DSP将地址传递给FPGA,FPGA经过地址译码操作对应外部设备数据。

3.1 FPGA软件规划

FPGA首要功用是完结5路RS422串口数据的一起收发操作开关量的输入和输出,并和DSP交流数据。FPGA可运用进程句子完结并行运转,对各外设的操作都是实时并行的,相互之间没有影响。

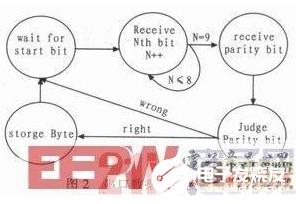

3.1.1 串口通讯

先将时钟经过分频得到8倍于波特率的串口时钟。数据接纳时,依据串口通讯的特色,首要判别低电平开始位。检测到开始位之后,依照严格地每八个时钟一位的联系收集一个字节8位的电平。因为噪声的存在或许会导致收集到的瞬时电平有误,此刻选用表决机制,即在8个时钟期间采样3次,以其间2次相同的电平为准。试验证明,表决机制能极大扫除随即噪声搅扰,下降串行通讯的误码率。接纳到数据之后存储在对应的双端口RAM中,等候DSP读取。串口数据承受流程如图2所示。

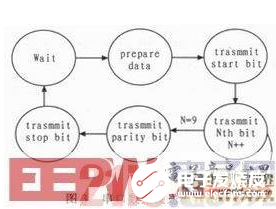

数据发送时先从双端口RAM中读出需求发送的数据,依照串口时钟,先发送开始位(低电平),再顺次经过移位寄存器将8位的数据转化成串行的‘0’/‘1’宣布。首要由下面句子完结:

txd《=txd_buf(0);

txd_buf(6 downto 0)《=txd_buf(7 downto 1);

其间txd是要发送的1位逻辑电平,txd_buf中存储着即将发送的数据。发送流程如图3所示。

将依照上述流程规划的程序在FPGA中进行测验。将FPGA串口和PC机衔接,选用115 200波特率接连作业3分钟,收发均无过错字节。

3.1.2 双RAM缓冲机制

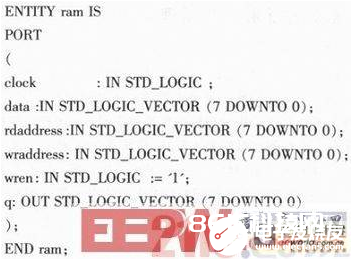

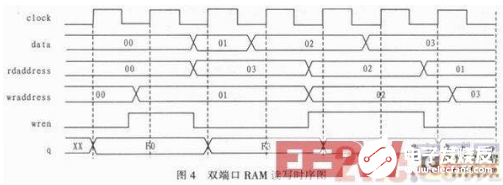

因为串口外设的波特率是115 200,归于低速外设,因而在串口数据和DSP之间选用双端口RAM作为缓冲区。因为此FPGA上自带片上RAM,因而能够运用开发环境自带的IP核生成片上双端口RAM,不必额定添加片外RAM器材(图1)。双端口RAM的实体界说和读写时序:

将每个RAM中的最终一个字节作为反映RAM存储状况的状况字。RAM的状况字代表的意义如下:

bit0:1-串口接纳到新数据帧 0-无新数据帧;

bit1:1-数据现已被读取 0-数据未被读取;

惯导和扶引头向弹载机每6 ms传输一帧数据,将数据存储到双端口RAM中,一起将bit0置‘1’,bit1清零,即RAM状况为“新数据帧未被读取”。因为惯导和扶引头的数据不同步,因而DSP每1ms就查询一次RAM的状况字。若接纳到新的数据帧(bit0=1),则读取RAM数据,并将“数据被读取”方位1(bit1=1)。这样,惯导和扶引头给DSP发送的数据推迟不超越1 ms,能够以为惯导和扶引头的数据是实时同步的。

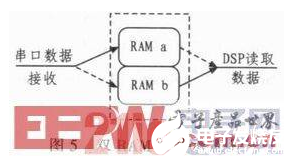

在串口接纳数据期间,假如串口和DSP在同一时刻操作RAM,或许导致DSP读取到帧紊乱的数据。为了确保数据帧的完好,不使两者一起读取RAM,选用双RAM缓冲机制,即为每个串口装备2个双端口RAM的作为缓冲,如图5所示。串口数据接纳程序经过查询RAMa和RAMb的状况字,若bit1=1,则将接纳到的数据帧存储到对应的RAM中,完结之后将bit0置1,bit1清0,这个周期为6 ms。与此一起,DSP每1 ms查询一次RAMa和RAMb,若bit0为1,则读取对应RAM中的数据帧,一起将bit0清0。bit1置1。串口数据发送进程与接纳相似,数据传输方向相反。

选用双RAM缓冲机制,使得串口和DSP不在同一时刻拜访同一RAM区,避免了错帧和丢帧,一起确保了数据传输的实时性。

3.2 DSP软件规划

DSP软件规划选用模块化规划办法,分为运用层和底层软件两部分。运用层软件首要完结飞控流程和飞控算法;底层软件首要完结数据格式的转化,以便经过DSP总线和FPGA进行数据交流。

3.2.1 运用层软件规划

外部的惯导和扶引头6 ms发生一次数据,DSP敞开1ms的定时器中止,在中止中每1 ms查询一次双端口RAM的状况字,判别是否有新数据发生,这样收集的数据推迟不会超越1 ms。飞控解算的周期为6 ms,遥测数据发送的周期为12 ms,在定时器中止程序中完结飞控解算和遥测数据发送。

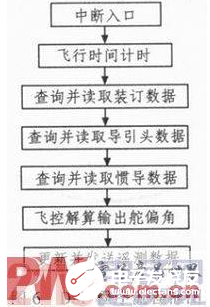

中止服务程序每1 ms运转一次,每次首要查询扶引头和惯导有没有更新数据,再读取新数据存储在大局结构体里。每6ms用大局结构体里得到的新数据解算一次飞控指令,得到舵机的输出视点,输出舵控指令,操控舵机。流程如图6所示。

3.2.2 底层软件规划

DSP底层软件首要完结外部数据交流和数据格式的转化。DSP经过XINTF发生读写时序(图2图3所示时序),FPGA也规划与之相匹配的时序完结两者之间的数据交流。

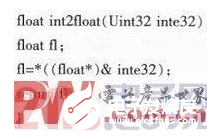

DSP运用层软件运用的是浮点数,而DSP和FPGA之间只能传递二进制数,因而需求依照IEEE规范进行浮点数和二进制数之间的转化。依据IEEE规范,能够用32位,即8个字节表明一个浮点数。假如将代表浮点数的4个字节组组成32位的整型数inte32,进行强制类型转化皆能够得到浮点数,转化函数如下:

将浮点数转化成整型数的办法与此相似。底层软件依照上述办法完结数据转化,供运用层调用。

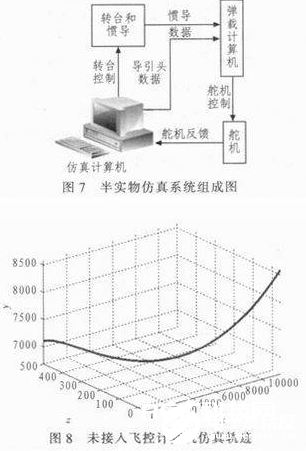

4 体系验证

弹载机什物设汁制造完结之后能够运用半什物仿真渠道进行测验,该半什物仿真渠道由上位机、惯导、舵机和三轴转台组成。如图上位机的作用是模仿导弹动力学模型和扶引头信息,并操控三轴转台运动模仿导弹姿势。导弹的运动信息由惯导丈量之后发送给飞控核算机,飞控核算机依据运动信息解算出舵机操控量操控舵机滚动,一起将遥测数据发送给上位机。上位机收集舵机反应的实践视点,将其代入导弹动力学模型,核算导弹姿势,操控三轴转台,这样就形成了完好的半什物仿真回路。

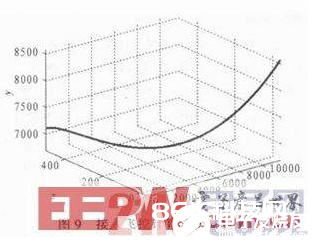

仿真试验中,首要不接入飞控核算机,由仿真核算机中的操控体系数学模型直接完结操控算法,所得导弹运动轨道如图8所示;将飞控核算机接入仿真回路,由飞控核算机完结制导操控算法所得运动轨道如图9所示。

由图8和图9的比照能够看出,飞控核算机接入之后飞控体系作业正常,导弹飞翔轨道根本共同,飞控核算机操控作用抱负。

5 定论

文中提出了一种依据DSP+FPGA的飞控核算机规划办法,在半什物仿真体系中验证了其功用,满意规划要求。处理了在多数字弹上设备存在情况下的数据帧实时同步问题。因为FPGA能够经过编程完结各种时序,所以此飞控核算机能够扩展为除了RS422外部接口外的其他多种数字设备接口,满意模块化、通用化的实践运用需求。