跟着计算机技能的迅速发展,电子信息技能越来越快地遍及到各行各业的运用中去。传统的物流信息收集作业办法是经过作业人员将票物进行核对,然后将票上的数据输入到计算机中。这一进程费时吃力,并且或许由于各种人为过错形成各式各样过错数据的存在,影响所收集信息的可靠性。而主动辨认技能运用计算机进行主动辨认,增加了输入的灵活性与准确性,使人们脱节冗杂的计算辨认作业,并且大大进步了物流信息收集的作业效率。现在,由沃尔玛、麦德隆等大超市一手推进的RFID运用,为零售业带来包括下降劳动力本钱、产品的可视度进步,下降因产品断货形成的丢失,削减产品偷盗现象等优点。其可运用的进程包括:产品的出售数据实时计算,补货,防盗等。本文运用RFID技能,用FPGA芯片与NRF905树立了无线通讯体系,成功的完结了无线收发数据。

1 体系规划

1.1 RFID简介

RFID(Radio Frequency IdentificaTIon,射频辨认技能)是运用无线电波对记载媒体进行读/写。射频辨认的间隔可达几十厘米至几米,且依据读/写的办法,可以输入数千字节的信息,一起,还具有极高的保密性。射频辨认技能适用的范畴:物料盯梢、运载东西和货架

辨认等要求非触摸数据收集和交流的场合,要求频频改动数据内容的场合尤为适用。如香港的车辆主动辨认体系驾易通,选用的首要技能便是射频技能。射频技能在其他物品的辨认主动化办理方面也得到了较广泛的运用。

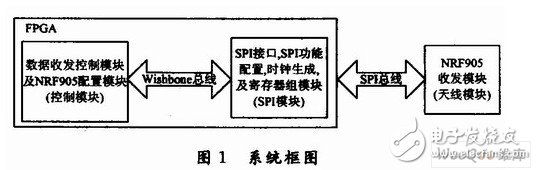

如图1所示即为本无线体系的整个构架,由操控模块,SPI模块以及天线模块构成。其间对SPI模块的装备由操控模块经过Wishbone总线来完结,并且对天线模块的装备,形式转化,收发数据等操作均由操控模块经过SPI总线来完结。下面迁就各个部分进行阐明。

1.2 天线模块(NRF905收发模块)

1.2.1 NRF905介绍

NRF905是挪威Nordic公司推出的单片射频发射器芯片,作业电压为1.9~3.6 V,32引脚QFN封装,作业于433/868/915MHz三个ISM频道。可以主动完结处理字头和CRC(循环冗余码校验)的作业,可由片内硬件主动完结曼彻斯特编码/解码,运用SPI接口与微操控器通讯,装备便利,功耗低,以-10 dBm的输出功率发射时电流只要11 mA,在接纳形式时电流为12.5 mA。

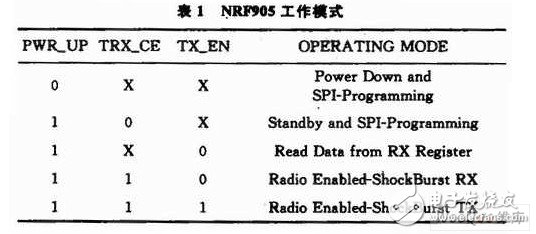

NRF905有ShockBurst接纳与ShockBurst发送两种作业形式;掉电和SPI编程与Standby和SPI编程两种节电形式。其ShoekBurst作业形式的特点是主动发生前导码和CRC,可以经过SPI接口进行编程装备。NRF905的作业形式由对TRX_CE,TX_EN,PWR_UP的设置来设置,见表1。

1.2.2 NRF905装备与作业进程

nRF905的一切装备都经过SPI接口进行。SPI接口由5个寄存器组成,一条SPI指令用来决议进行什么操作。SPI接口只要在掉电形式和Standby”形式是激活的。

其间SPI接口的5个寄存器别离为:

(1)状况寄存器:寄存器包括数据安排妥当DR和地址匹配AM状况。

(2)RF装备寄存器:寄存器包括收发器的频率、输出功率等装备信息。

(3)发送地址:寄存器包括方针器材地址,字节长度由装备寄存器设置。

(4)发送有用数据:寄存器包括发送的有用Shock Burst数据包数据,字节长度由装备寄存器设置。

(5)接纳有用数据:寄存器包括接纳到的有用ShockBurst数据包数据,字节长度由装备寄存器设置。在寄存器中的有用数据由数据准备安排妥当DR指示。

ShoekBurst技能使nRF905可以供给高速的数据传输,而不需求高速操控器来进行数据处理或时钟掩盖。经过将与RF协议有关的高速信号处理放到芯片内,nRF905供给给运用操控器一个SPI接口,速率由微操控器自己设定的接口速度决议。nRF905经过ShockBurst作业形式在RF以最大速率进行衔接时下降数字运用部分的速度来下降在运用中的均匀电流耗费。在ShockBurst RX(接纳)形式中,地址匹配AM和数据准备安排妥当DR信号告诉操控器一个有用的地址和数据包现已各自接纳完结。在ShockBurst TX(发送)形式中,nRF905主动发生前导码和CRC校验码,数据准备安排妥当DR信号告诉操控器数据传输现已完结。

1.3 SPI模块

1.3.1 SPI总线介绍

SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU与各种外围接口器材,以串行办法进行通讯。它运用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有用的使能信号线(SS)。这样,仅需3~4根数据线和操控线即可扩展具有SPI接口的各种I/0器材。

SPI总线形式的数据是以字节为单位进行传输的(一次传输可以传多个字节),每字节为8位,每个指令或许数据块都是字节对齐的(8个时钟的整数倍)。数据按位传输,高位在前,位置在后,为全双工通讯,数据传输速度整体来说比I2C总线要快,速度可到达每秒几兆比特。SPI接口是以主从办法作业的,这种形式一般有一个主器材和一个或多个从器材。在本文规划的无线通讯体系中,由FPGA完结的SPI总线接口模块为主机,NRF905的SPI模块为从机。

SPI时序形式的挑选:

SPI接口有4种不同的数据传输时序,取CPOL和CPHL这两位的组合。CPOL是用来决议SCK时钟信号闲暇时的电平;CPOL=O,闲暇电平为低电平,CPOL=1时,闲暇电平为高电平。CPHA是用来决议采样时间的,CPHA=0,在每个周期的第一个时钟沿采样;CPHA=1,在每个周期的第二个时钟沿采样。

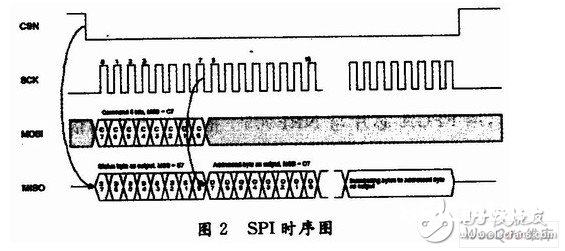

图2为NRF905的SPI接口的时序图,由此本文规划的SPI作业形式是在CPOL=O,CPHA=O这种时序下。

1.3.2 SPI硬件规划

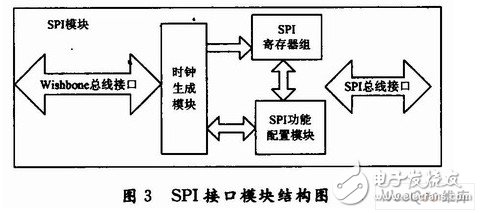

图3是本文无线通讯体系中SPI模块的结构图,该体系中的SPI首要由时钟生成模块,SPI寄存器组,SPI功用装备的模块组成,并且经过Wishbone总线与操控器相连,详细规划如下:

时钟生成模块:由于SPI模块是根据FPGA来完结的,而FPGA外部供给的时钟较快(50 MHz或100 MHz),不适合与NRF905的SPI接口进行通讯(1 Hz~10 MHz),所以需求分频来使时钟慢下来。可是至于几分频是由SPI功用装备模块来完结的。其次由于SPI协议指出数据可在上升沿或下降沿触发,所以还需求对时钟的上升沿或下降沿进行辨别(也称抓沿程序),这个功用也由这个模块完结。

SPI寄存器模块:这个模块完结的是一个由16个8位寄存器组成的128位的寄存器组,也便是说经过SPI接口一次性可收发8~128位的串行数据。详细操作由SPI功用装备模块来完结。

SPI功用装备模块:这个模块相当于一个SPI操控器,经过对其寄存器的装备来决议时钟的分频数,收发数据位数,时钟上升沿或下降沿传输数据等,而对这些寄存器的装备是由操控模块完结的。下面就装备寄存器做一些扼要阐明。

首要介绍操控寄存器:

操控寄存器第O位go:是否开端发送。

操控寄存器第1位rx_negedge:接纳数据是下降沿仍是上升沿。

操控寄存器第2位tx_negedge:发送数据是下降沿仍是上升沿。

操控寄存器第3~9位char_len:发送数据的位数(由于SPI是全双工的,所以这实际上也是接纳数据的位数)。

操控寄存器第10位lsb:是从高位发送仍是位置发送。

操控寄存器第11位ie:读写完结之后是否发送中止信号。

操控寄存器第12位ass:是否主动发生片选信号。

分频寄存器:spi_divider_sel。

状况寄存器:spi_ctrl_sel。

数据寄存器O:spi_tx_sel[0]。

数据寄存器1:spi_tx_sel[1]。

数据寄存器2:spi_tx_sel[2]。

数据寄存器3:spi_tx_sel[3]。

片选信号寄存器:spi_ss_sel。

1.4 操控模块

关于操控模块来说,其完结办法是运用根据Verilog言语的有限状况机来完结,相当于一条一条的指令来操控SPI模块接纳发送数据。操控模块分红三个独立的部分即接纳操控模块、发送操控模块及NRF905装备模块。其间接纳与发送操控模块别离包括对SPI进行装备的状况。下面对接纳操控模块的规划进行阐明。图4即为Debussy归纳出的状况机转化图。

为了完结无线通讯而规划的状况较多,比较复杂,故只对比较重要的状况做些扼要阐明。idle闲暇状况,完结对端口进行初始化寄存器清零;config_div状况,对时钟进行分频(界说sclk);configwb_in状况,界说传输数据的位数以及是上升沿收发仍是下降沿收发,wb_inl,wb_in2,wb_in3,wb_in4,这四个状况便是经过Wishbone总线接口对SPI装备要写的数(每一个状况对应一个寄存器);configspi_out状况,开端传送数据;done状况,片选置高数据传送完结;readeonfigreg_prel状况,设定发送数据位数;readconfigreg(读寄存器操控字位数)状况,经过Wishbone总线接口对SPI装备读指令字;readconfigreg_out状况,设定发送/接纳数据位;alldone状况,片选置高完结装备数据读取的进程。

该规划考虑到验证装备进程的正确性,故特意设定了读寄存器装备数据的状况,ehangemode便是接纳状况,当接纳完结后(DR=1)进入eh-angmodee状况,把收到的数据读出来。然后再回到readeonfigreg_prel状况,等候新的传输数据。

2 体系验证

该规划终究进行了板级验证,FPGA开发板与NRF905的PCB板构成这个验证体系。FPGA芯片的选用Xilinx公司的XC2V1000,所用的归纳东西是Synplify,前仿真与后仿真用来检查波形的东西是Modelsim,所用到的布局布线东西与下载东西是ISE10.1集成的iMPACT,而板级测验用来检查波形的东西是Chipseope。

在下载之前对本规划进行了足够的功用仿真,用Verilog编写了SPI从机仿照NRF905的SPI接口与SPI主机进行通讯,保证可以完结预先设定的功用。

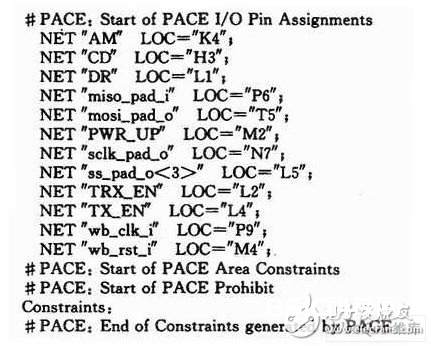

下载是将装备文件下载到详细的FPGA芯片中。本文体系中选用的是JTAG下载办法,下载东西运用Xilinx ISE的集成东西iMPACT。在下载之前进行了管脚绑定其意图就在于可以将规划的输入/输出端口束缚在FPGA芯片的适宜的引脚上,以便利对其进行剖析和调试并与外界I/O进行相连。下面即为本规划中相应的管脚束缚文件中的相关内容。

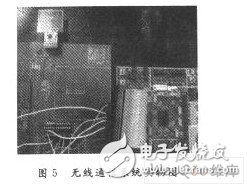

下载完结后,按照管脚绑定将FPGA开发板与NRF905的PCB相连,图5即为无线收发的PCB衔接图。

这仅仅其间一端,在这里假定为接纳端,那么别的还有相同的互连PCB板作为发送端。右边的PCB板为FPGA用来完结SPI模块与操控模块。左上倒凸字形的小PCB板即为NRF905,左面的PCB板起到了衔接FPGA与NRF905的左右,并给NRF905供给电源。

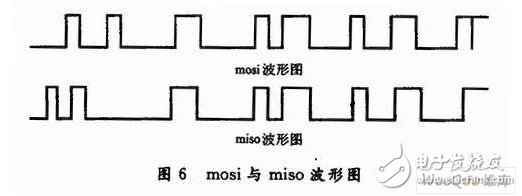

体系树立起来后,下一步是终究的板级验证。图6为用Chipscope得到的波形图。mosi与miso别离是发送端与接纳端SPI总线上的信号。从图中可以看出数据根本符合,由此标明规划的以FPGA操控NRF905的无线通讯体系可以正常作业。

3 结语

本文完结了以FPGA操控NRF905的无线通讯体系,经过对体系的树立与仿真测验以及板级验证,证明了无线通讯体系可以正常作业,并且无线体系通讯间隔可达100 m,根本完结了无线体系通讯的要求,充分阐明该规划体系的实用性。