当今许多手持电子设备都在LCD、照相机和键盘的接口电路中选用串行器/解码器(SerDes)技能。SerDes能够削减穿过铰链或滑动设备的信号数量,然后答应选用新的铰链或滑动设备,并能够下降成本。从并行传输线转换成串行传输线将发生差分阻抗的问题,差分阻抗将严峻影响差分信号的完整性,导致LCD屏幕闪耀、射频搅扰以及器材的容限问题。本文评论手持电子设备中高速信号的差分阻抗效应,并评论怎么丈量、调试和处理这些问题。

SerDes器材一般都选用差分阻抗为100Ω的传输线,但在手持设备中完结100Ω传输线十分困难。例如,在翻盖或滑盖手机上,传输线必需通过基带PCB、铰链的柔性PCB、LCD PCB或许软硬复合板。在通过这些介质后仍坚持100Ω的差分阻抗是十分困难的。

有许多要素会影响差分阻抗,比方走向宽度、附近的地线及介电常数。但最主要的影响来自地平面,即一个地平面(微带线)或两个地平面(带状线)以及传输线与地平面之间的间隔。这在射频环境中是个大问题,因为这类运用都要求在大多数电子器材外表进行阻隔接地,以屏蔽EMI。这种接地会大幅下降传输线的差分阻抗,使其降到50Ω或以下。

低差分阻抗

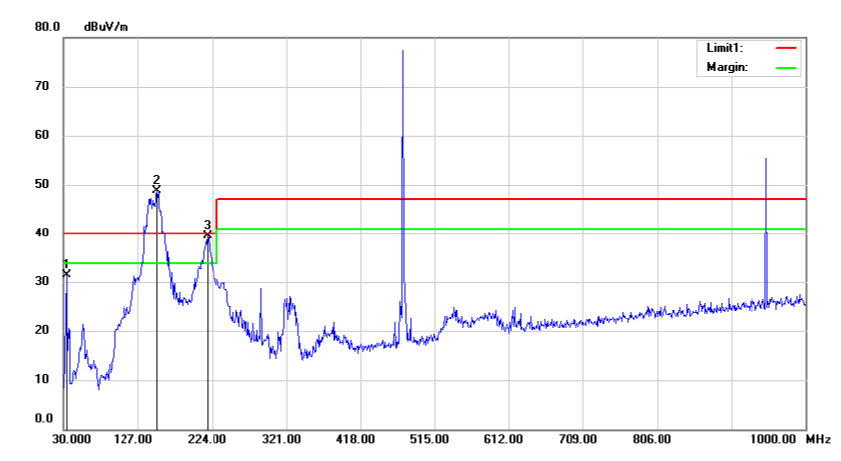

差分阻抗下降会给信号传输带来许多问题,第一个问题是阻抗失配将导致信号发生反射,其它两个问题则在射频环境下更为杰出。较低的差分阻抗意味着传输线出现更强的电容性,这会给信号传输添加负荷并下降阶跃信号(如时钟信号)的起伏。信号起伏下降会影响无线电体系的RF鲁棒性,例如在GSM手机中,信号起伏下降会严峻影响串行数据。GSM接收机的最大发送信号强度一般为32.5dBm,在这个信号强度下,很多的射频信号会耦合到串行线路上。假如SerDes信号的起伏因为传输差分阻抗下降而减小,就会发生数据位过错,导致LCD闪耀。

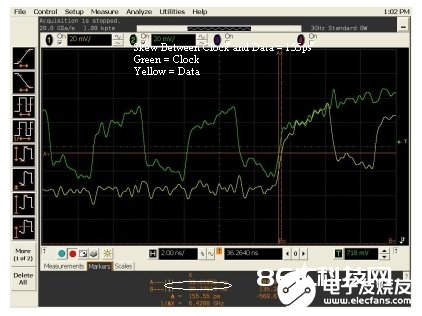

第三个问题是时钟和数据间出现倾斜失真。在图1中,时钟信号一直在跃变,因而其起伏会因差分阻抗下降而下降,但数据并不必定一直在跃变。当有2到3个数据位坚持不变时,数据信号起伏就会到达其满起伏。当数据信号跃变时,就会因差分阻抗下降而导致时钟和数据之间的倾斜失真。这看起来问题好像不大,但典型的SerDes倾斜失真的容限为±150ps,差分阻抗降到39Ω时,倾斜失真就会超出这个容限。此外,时钟和数据间的倾斜失真还会导致数据过错,并下降数据对RF搅扰的抵挡才能。为保证串行传输计划在射频环境下正常作业,就必须处理差分阻抗下降的问题,并挑选倾斜失真容限最大的SerDes器材。

图1:当差分阻抗降到39Ω时,时钟和数据之间出现倾斜失真。

高差分阻抗

差分阻抗下降是因为接地效应过度,阻抗升高则是因为接地效应缺乏。接地屏蔽并非影响差分阻抗的仅有要素,走线宽度和介电常数也可引起阻抗升高,但接地屏蔽是主要要素。阻抗升高多见于那些无接地屏蔽的线缆(如带状线缆)或许带有气隙的柔性线缆。一般,相对于坐落外层的接地屏蔽来说,串行走线坐落内层,串行线与接地屏蔽之间的间隔对阻抗升高的奉献较大。较低的差分阻抗意味着传输出现较强的电容性,较高的差分阻抗意味着传输出现较强的电感性。

阻抗升高后会带来两个问题。第一个问题是因阻抗失配而发生的信号反射,第二个问题是因阻抗添加而形成过冲和下冲失真(图2)。严峻的过冲或下冲失真将使信号超出共模规模,导致数据过错。这种失真也会下降抵挡串扰和RF搅扰的才能。比方,假如串行信号强度挨近共模规模,那么,即便强度不大的串扰也会使串行信号超出共模规模。在射频运用中,导致阻抗升高的最大潜在要素是选用带气隙线缆的规划。

图2:高差分阻抗将导致过冲和下冲失真。

电磁搅扰

在处理差分阻抗下降问题的时分,或许需求选用单端接地屏蔽。许多RF工程师都忧虑这会影响接地阻隔的作用,:一是忧虑高速信号的RF辐射会给电话无线通道带来问题,二是忧虑高速信号简单遭到RF搅扰。为处理这些问题,SerDes器材制作商选用差分信号技能来防止反射信号的发生,进步信号抗搅扰才能,并尽力找到能避开无线电频带的传输频率。接地太多或太少都会引起问题。如前所述,过多的接地会下降串行信号的起伏,削弱信号抗RF搅扰的才能,导致数据位过错。接地太少则或许使更强的射频信号耦合到串行信号上。平衡这两个问题的办法是选用单端接地(选用微带线)和网格状接地。选用微带线和网格状接地可使差分阻抗挨近100Ω,一起也能到达必定的阻隔作用。

规划100Ω差分阻抗的过程

假如因为接地屏蔽太多而形成差分阻抗下降,或许因接地屏蔽太少而形成差分阻抗增大,那么应该怎么规划?什么样的产品能支撑这种运用环境?首要,要挑选差分阻抗匹配规模大的SerDes器材(比方飞兆半导体的μSerDes器材)。许多串行技能都要求100Ω±10%的匹配容限,但事实上这是不或许完结的。uSerDes技能根据恒流型I/O而不是电压型I/O,而且答应差分阻抗在70到120Ω规模。在PCB或FPCB板规划串行传输线时,运用差分阻抗核算器十分有用。现在市面上已有能结合附近接地和磁场要素的专业级核算器,能够完结最准确的模仿。假如没有这类设备,也可求助于网络,许多网站都能根据业界已知的一些根本公式来核算差分阻抗。这些公式的作用一般都挨近专业核算器,只要不超出它们的运用极限。

完结板卡和柔性线缆的规划、制作和安装后,主张选用时域反射计(TDR)丈量。TDR是一个十分有用的处理差分阻抗问题的测验东西。在测验一对差分线时,TDR发送差分信号到传输线上,并丈量阻抗失配引起的反射。做此测验时,最好处理好差分阻抗的下降问题。如前所述,差分阻抗下降一般源于接地屏蔽,处理此问题最直接的办法是查看Gerber文件,找出问题接地址地点。一般最需求注意的区域是PCB上连接器处的内层串行走线,以及带双接地屏蔽的线缆的可动部分。请注意以下几点:内层串行走线的上基层一般都有阻隔接地;连接器处的走线难度很大,40条以上的线路都要连接到连接器上,一般会在串行线上基层都进行额定的屏蔽;柔性线缆的活动部分一般都十分薄,串行线上基层的接地会大幅减小差分阻抗。

处理这些问题的第一个保存办法是去除接地屏蔽,或许添加串行线与接地屏蔽之间的间隔。假如去除接地屏蔽不可行,能够选用其他办法略微进步差分阻抗。例如,假如走线宽度本来为4mil,则将其改为3mil,那么差分阻抗将进步约10Ω。另一种或许见效的办法是运用网格状接地屏蔽,而不是选用实心覆铜。网格状屏蔽有助于将差分阻抗进步约10Ω,一起还能完结屏蔽阻隔。

跟着越来越多的手持电子设备选用串行传输技能,差分阻抗的问题越来越杰出。在PCB和柔性PCB布线之初就找出这些问题十分要害。在信号起伏、抗搅扰才能和电磁辐射间进行权衡,就能构建出鲁棒的串行传输处理计划。

责任编辑:gt