在对Virtex系列FPGA进行充沛了解和研讨的基础上,结合对XC4000系列FPGA和DSP背板开发规划经历,研发出了依据XCV200/300PQFP240和TMS320C40的可编程嵌入式高速信号处理背板。背板选用了针对体系需求自行开发的XPCI总线,背板可脱离实践运用体系进行独立的面向运用的规划和调试,也可依照XPCI总线规范便利地嵌入到实践运用体系中,成为体系的一部分进行联合调试。

对可编程嵌入式信号处理背板进行全面综合测验的成果标明,背板功用到达了预期规划要求,作业状况安稳。咱们还针对实践运用开发了一些FPGA模块和DSP程序。

1Virtex系列FPGA功用简介

在前几代FPGA开发的基础上,Virtex系列FPGA结合了多种可编程体系的特征,选用了快速灵敏的层次性互连布线资源和先进的处理技能,供给了高速度、大容量的逻辑解决方案,进一步缩短了数字信号处理体系的开发周期。与前几代FPGA比较,Virtex系列FPGA的特性首要体现在以下几个方面:

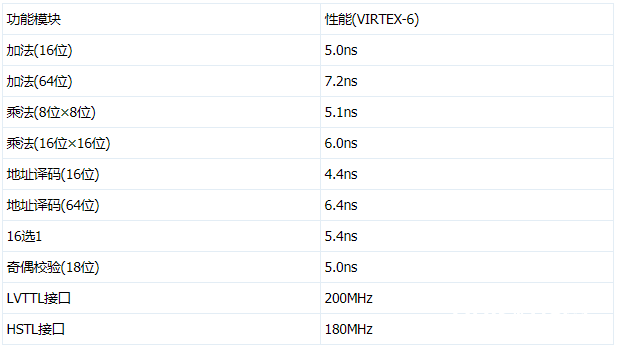

(1)更高的处理速度和更高的逻辑门密度。Virtex系列最大体系门数高达100万门,体系功用可达200MHz,其间比较常用的几个功用模块功用如表1所示。

表1Virtex系列FPGA几个常用功用模块的功用

(2)更多可兼容的I/O接口规范。Virtex系列可兼容16种高功用接口规范,可直接与ZBTRAM器材接口,且其共同的I/O分组方法可使多种不同电压规范接口在同一片FPGA上完结。

(3)片内时钟办理电路。Virtex系列内部包括4个灵敏的延时锁相环用于高档时钟办理,可完结倍频、分频、锁相等功用,此外还有4个主大局时钟网络和24个从本地时钟网络,以完结高速时钟的传输。

(4)层次性存储办理体系。Virtex系列内部查找单元可装备为16bit和32bitRAM、16bitDPRAM或16bit移位寄存器,其BlockRAM资源可装备为4kbitDPRAM或FIFO、CAM等存储器件,且供给了高速外部RAM接口。

(5)愈加灵敏的体系结构。杂乱的进位逻辑链进步了算术逻辑功用,杂乱的乘法器支撑,级联链支撑宽位输入模块,丰厚的带时钟使能的寄存器和锁存器,支撑异步和同步复位及置位,支撑IEEE1149.1鸿沟扫描逻辑。

(6)依据SRAM的在体系可重构技能。可无限次重复编程,包括主串、从串、SelectRAM和JTAG四种装备形式,支撑部分重构。

2依据Virtex系列FPGA的可编程嵌入式信号处理背板的规划

因为对Virtex系列FPGA进行了充沛了解和了解,咱们研发了依据自行开发的XPCI总线的可编程嵌入式信号处理背板。因为Virtex系列FPGA内部结构相同,外部引脚兼容,只是在体系门数上有所区别,咱们选用了XCV200PQ240-4作为可编程嵌入式信号处理背板的主处理芯片,与FPGA接口的DSP选用功用强大、接口灵敏的TMS320C40DSP。背板中DSP的运用意图是对FPGA进行办理和操控、对FPGA处理成果进行剖析、经过DSP软件完结其他相关功用,以进步体系规划的灵敏性。C40DSP具有两组外部总线资源和6个高速通讯口,能便利灵敏地完结体系扩展。背板中FPGA可依据规划需求挑选不同规划的芯片。

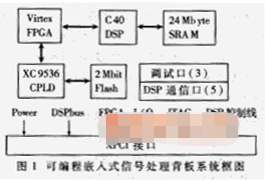

可编程嵌入式信号处理背板结构如图1所示。背板上首要包括1片XCV200PQ240FPGA、1片TMS320C40DSP、1片XC9536CPLD、1片EDI8L512SRAM(512K×32bit)、1片AT49020Flash?2Mbit、DSP调试JTAG接口、FPGA调试X_Checker接口、CPLD调试JTAG接口、自行开发XPCI接口及5个独立DSP通讯口。背板一切器材除DSP外均选用贴片封装、双面装焊,使得背板的尺度较小(76mm×127mm×12mm),DSP外围512K×32bitSRAM使得背板体系能够满意大部分运用程序的要求。2MbitFlash用于固化FPGA装备和DSP运用程序代码。背板体系既能够独立作业(Standalone方法),也能够经过XPCI总线嵌入体系作业(Plug_in方法)。

背板体系以40MHz晶振输出作为时钟,C40DSP作业在40MHz时钟下,XCV200FPGA以40MHz时钟作为输入,在内部经过DDL电路可将内部作业时钟倍频到180MHz。DSP经过本地总线(LA0..30、LD0..31)以TTL兼容方法与FPGA接口,占用FPGA65biTI/O资源;DSP经过本地总线对FPGA进行装备、参数设置及数据交换,完结软硬件之间的协同处理。

Virtex系列FPGA内部供电电压为2.5V,I/O经过VCCO和VREF操控完结与各种电平接口之间的兼容;与TTL兼容的VCCO操控电压为3.3V,VREF作为一般I/O运用;Virtex的I/O分组方法完结使得不同电平接口得以在同一芯片规划中共存。

背板经过168线XPCI总线与外部体系接口,XPCI总线首要包括三大部分:电源接口、FPGA的可编程I/O口、DSP接口。电源接口包括给DSP、CLPD、SRAM及其他TTL逻辑供电的5V电源,给XCV200PQ240等Virtex系列FPGA内部作业逻辑供电的2.5V电源,I/O接口供电电平VCCO和分组参阅电平VREF(Bank0~Bank7FPGA可编程I/O接口首要供给了64个从Virtex系列FPGA引出的可编程I/O引脚,用于规划特定逻辑;DSP接口供给了TMS320C40DSP主总线接口、中断口和通讯端口0及TCLK0和TCLK1,用于体系扩展及与用户程序之间的数据交换。

背板有丰厚的装备及调试接口。Virtex系列FPGA在板上可完结三种装备方法:从串方法(经过Xlinx专用X_Checker接口)、JTAG方法(经过XPCI接口供给给用户)、Select_RAM方法(经过DSP和XC9536CPLD完结);DSP调试经过专用14芯JTAG接口完结;CPLD逻辑可经过规范JTAG电缆实时修正装备。DSP其他5个通讯口经过5个IDC14插座输出,可依据体系实践需求选用。

3依据Virtex系列FPGA的可编程嵌入式信号处理背板的调试

在信号处理背板制造完结之后,咱们对背板进行了调试,并开发了一些背板专用装备程序。

在调试进程中咱们运用了WhiteMount公司的CodeComposerDSP开发调试软件和Xilinx公司的FoundaTIon2.1IFPGA&CPLD开发调试软件。为全面验证咱们预期的规划作用,调试按以下进程进行:

(1)使用FoundaTIon2.1I经过X_Checker接口向FPGA下载测验装备,FPGA呼应成果正确。

(2)使用CodeComposer经过JTAG电缆对DSP内部RAM和外部SRAM进行测验,测验标明硬件规划正确。

(3)使用FoundaTIon2.1I经过规范JTAG电缆对XC9536下载测验装备,CPLD呼应成果正确。

(4)使用Foundation2.1I经过规范JTAG电缆对XC9536下载自行规划的FPGA专用装备,使用CodeComposer经过JTAG电缆对DSP加载专用装备程序,使得DSP完结对Flash烧录FPGA装备数据和DSP的Bootloader数据。

(5)脱离开发体系,背板上电经过Flash内的装备数据自行FPGA装备和DSP的Bootloader?运转成果正确。

4运用规划实例

为进一步验证背板的通用性,咱们依据实践课题需求,在背板上开发了两个运用规划实例。一个是320MHz32bit高速计数器。咱们在曾经开发的200MHz高速计数器的基础上,依据多路均匀相差时钟信号在TOA时刻进行逻辑译码取得高速计数作用的原理,经过外部40MHz输入时钟,使用VirtexFPGA内部DDL电路发生4路相差90°的80MHz信号,构成320MHz32bit高速计数器,使得时刻丈量精度到达3ns左右。该规划可用于高精度TOA、PW、RF等参数的丈量。

另一个是依据内容可寻址存储器(CAM)的相关比较器。咱们在充沛剖析Xlinx供给的CAM_Core规划的基础上,自行规划了一种依据CAM的可编程相关比较器。该比较器选用中值比较法,可经过操控线操控比较规模,并规划了一种专门抵挡捷变参数的多值比较逻辑。咱们使用XCV200PQ240完结了上述规划,经过测验母板上的UART从操控台微机上接纳模仿辐射源数据。测验成果标明,在辐射源参数空间堆叠不太严峻的情况下,该规划可一起处理80个以上的装定辐射源参数(128bitPDW可包括捷变参数),且能到达较好的分选作用,可见它在侦查信号处理范畴的运用远景是十分宽广的。

责任编辑:gt