为什么说单片机会成为深度学习最肥沃的土壤-除此之外,皮特有个新的想法要和大家分享 他坚定地相信,未来的深度学习能够在微型的、低功耗的芯片上自由地奔跑。 换句话说,单片机 (MCU) ,有一天会成为深度学习最肥沃的土壤。 这里面的逻辑走得有些绕,但好像还是有点道理的。

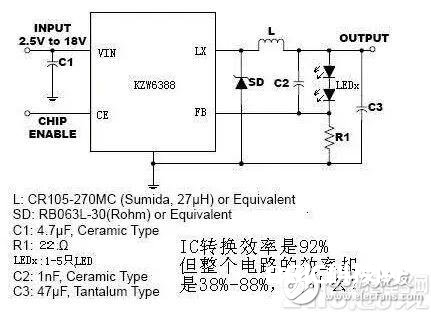

LED恒流驱动电路设计(KZW3688和CE9908)-其实每款DC/DC的IC(无论升压或降压)都能接成恒流的LED的驱动,现在分别以KZW3688和CE9908为例介绍一下接法及特点。 1、KZW3688降压IC,其接法如下: 原理非常简单,大家一看便知这里不再赘述;其中R1的值的算法是3.3V/所需电流.上图中接的是2-5只,也可以多路并联使用,并且这里有个问题问大家:C2是否需要呢?看一下下图中的接法: 去掉了C2,并联了一路甚至几路LED串,感到效果如何?有兴趣回答吗? 适合这种接法的电路太多了,除3688外,还有PT1102、1101、l

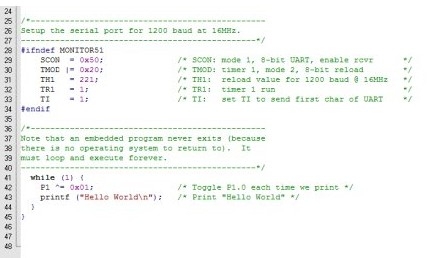

如何使用单片机中printf-1. 如c语言同:printf(“”);在控制台就会输出“”中的内容;

2. 通过串口输出:只需要在初始化串口后,直接使用printf(“”)即可通过串口输出“”中的内容(参考keil的安装文件夹里有个EXAMPLE目录,里面HELLO的例子)。

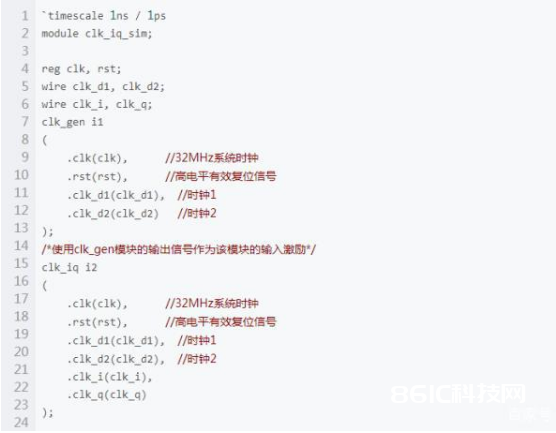

关于testbench在FPGA编程中的技巧-定义信号类型:原来模块中的输入信号,定义成reg 类型,原来模块中的输出信号,定义为wire类型,但这里有个问题,如果在testbench中本身有一个模块需要,如用来产生时钟,送给要仿真的模块,那怎么定义信号类型呢?

FPGA工程开发中仿真的重要性-很多初学者入门FPGA的时候所学习的编程例子都是很简单的,比如流水灯、数码管点亮之类的。这种入门级别的例子有个特点,代码量少,逻辑简单,分析容易。而且大家刚开始都是照着书本抄一遍的,基本上都是没有什么问题的。一上板子就发现效果出来了。

FPGA设计怎么化繁为简-有个笑话说,有个病人感冒了,于是去看医生,医生诊断后说,你得了感冒,但是我只会治疗肺炎,不如你回家再浇点凉水,把病恶化成肺炎,那我能治了。这个笑话展示了庸医误人。但是另一方面,从逻辑上来讲,医生则是一个把未知问题转化成已知问题的高手。

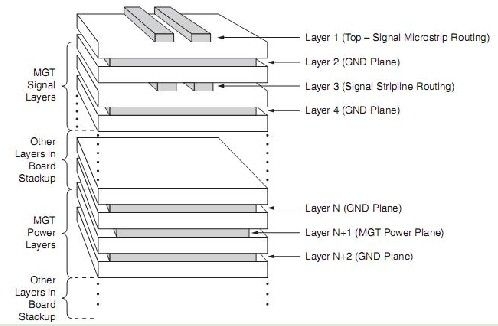

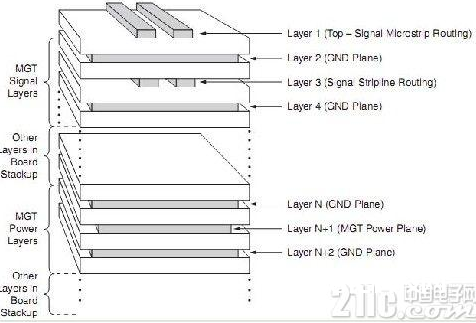

针对FPGA的GTP信号 PCB设计过程中需要考虑到以下因素-千兆位级串行I/O技术有着极其出色的优越性能,但这些优越的性能是需要条件来保证的,即优秀的信号完整性。例如,有个供应商报告说,他们第一次试图将高速、千兆位级串行设计用于某种特定应用时,失败率为90%。为了提高成功率,我们可能需要进行模拟仿真,并采用更复杂的新型旁路电路。

xilinx的axi4-stream-slave接收数据模式-xilinx官方实例代码如下,其实大概意思就是一个高电平之后,变成低电平。然后再高电平,等待tlast信号再拉低。这样做的为了时序紧凑型,xilinx为了方便在第一个valid和ready信号得到头部信号,这个有个短暂的停留时间去分析头部数据。