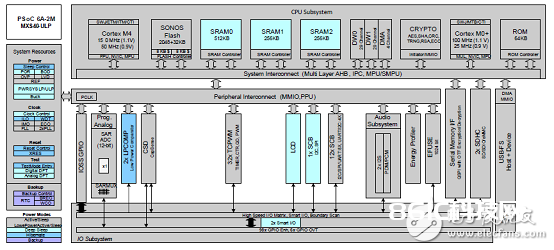

可升级和可配置的PSoC62系列MCU平台架构-Cypress公司的PSoC 62系列MCU是可升级和可配置的平台架构,采用超低功耗40nm技术,组合了双核MCU(150-MHz Arm Cortex-M4F CPU和100-MHz Cortex M0+ CPU)和低功耗闪存(多达2MB)以及1MB SRAM,数字可编逻辑,高性能模数和数模转换器,低功耗比较器以及其标准通信和定时外设.器件可提供多达104 GPIO,工作电压1.7V-3.6V,主要用在可爱穿戴,智能家居,工业IoT,手持医疗设备等.

关于Virtex和Kintex UltraScale架构的FPGA和Vivado开发工具的机构要点- 基于UltraScale架构的FPGA实现数据传输机制是通过将高性能的并行专用IO接口和高速的串行收发器结合起来实现的,UltraScale架构的串行收发器传送数据的速率能够达到16.3Gbps,满足主流的串行协议要求,当然传输速率也能够达到32.75Gbps,允许25G+比特位的地板设计,而且相对以前的收发器而言,能够大大降低每比特位传输的功耗。UltraScale架构的FPGA芯片中的收发器都兼容PCIe3.0和PCIe4.0,专用的PCIe集成模块支持PCIe3.0 X8型端口和根端口的设计需求。

赛灵思业界20nm技术首次投片标志着UltraScale架构时代来临-在28nm技术突破的基础上,赛灵思又宣布推出基于20nm节点的两款业界首创产品。赛灵思是首家推出20nm商用芯片产品的公司。此外,该新型器件也是赛灵思将向市场推出的首款采用UltraScale技术(可编程产业的首款ASIC级架构)的产品。UltraScale架构充分发挥Vivado设计套件中尖端EDA技术的优势,使客户能够快速开展新一代All Programmable创新。在28nm节点上,赛灵思在业界率先推出Zynq-7000 All Programmable SoC 和 Virtex-7 3D IC两款产品。

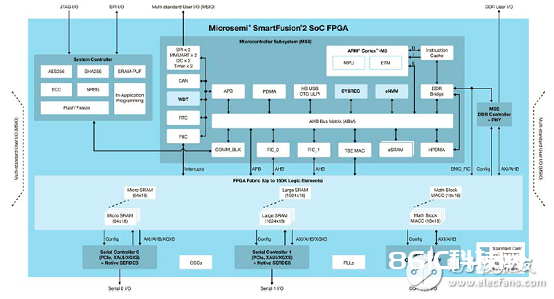

Microsemi 基于闪存FPGA架构低功耗SmartFusion2 SoC FPGA开发方案-Microsemi公司的SmartFusion2 SoC FPGA是低功耗FPGA器件,集成了第四代基于闪存FPGA架构,166MHz ARM Cortex-M3处理器和高性能通信接口,是业界最低功耗,最可靠和最高安全的可编逻辑解决方案.高速串行接口包括PCIe,10Gbps附加单元接口(XAUI)/XGMII)以及SerDes通信,主要用在数据安全,马达控制,系统管理,工业自动化,高速串行I/O应用,PCIe,,SGMII以及用户定义的串行接口.

设计FPGA系统时通常需要考虑的问题分析-许多工程师认为,只要定义了 FPGA 的功能,工作就算完成了。但实际上将 FPGA 插入 PCB 时也会面临一系列挑战。 对于许多工程师和项目经理来说,在 FPGA 中实现功能并实现时序收敛是主要目标,但实际上在印刷电路板上设计 FPGA 的硬件级工作也会出现很多有趣的挑战,只有解决了这些挑战才能实现成功设计。 一切的起点均在于架构。硬件开发第一步就是定义解决方案的架构。架构应该对应于系统要求,并具体明确它们如何在硬件中得到实现。