在装备完s3c2440的体系时钟后,咱们来操控串口.之所以将串口放在这么靠前,是因为串口会给咱们带来更多的信息.在没有串口的时分,uboot发动阶段只能靠led来显现一些信息.那么有了串口,debug就便利很多了.在作业中,一般情况下,很少有机会用jtag口加上贵重的codeviser东西进行debug,也很少用gdb进行长途debug的,用的最多的仍是翻开debug的define来剖析确认问题.

仍是从s3c2440的datasheet开端:

s3c2440A的UART供给3个独立的异步串行IO口,每一个都支撑中止和DMA.换句话来说,UART能够发生中止恳求或DMA恳求来在CPU和UART之间传输数据.UART在体系时钟下最高支撑115200的波特率.假如运用UEXTCLK的话,UART能够作业在更高速的时钟下.每个UART通道都有来年各个64字节的FIFO,一个是接纳用的,一个是发送用的.

UART包含可编程的波特率,IR发送/承受,一或两个中止位,5/6/7/8个数据位和奇偶校验.

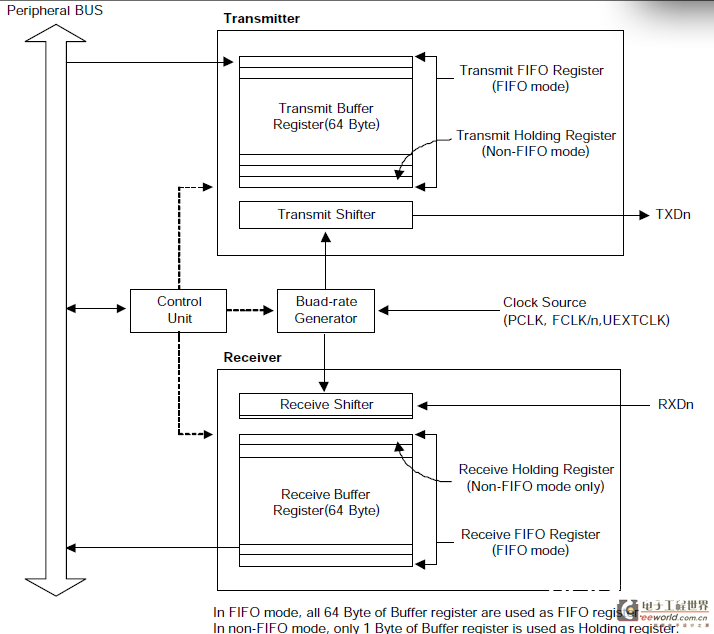

每个UART包含一个波特率发生器,发送器,接纳器和一个操控单元.波特率发生器能够由PCLK FCLK/n 或许UEXTCLK来确认.发送器和接纳器包含64字节的FIFO和数据移位器.数据首要写到FIFO中,然后在发送之前复制到发送器的移位器.最终数据移位经过TxDn数据发送管脚发送出去.相同的,接纳的数据经过RxDn接纳数据管脚移位进来,然后从移位器拷贝到FIFO中.

UART的框图如下:

值得说的是:在FIFO形式下,buffer寄存器的一切64个字节都被用作FIFO寄存器.而在非FIFO形式下,buffer寄存器只要一个字节被用于Holding寄存器.

串口的操作:

串口操作包含如下:数据发送,数据接纳,中止发生,波特率发生,loopback形式,IR形式和主动流操控.

数据发送:

发送的数据帧是可编程的.它包含一个开端位,5到8个数据位,一个可选的校验位和1到2个中止位,这些都在ULCONn寄存器中操控.发送器能够发生中止条件,能够在一个数据帧的发送时刻内强制串口输出为逻辑0.在当时的传输数据发送完结后会发送一个中止信号,在中止信号发送后,它会持续发送数据到Tx FIFO(而在非FIFO形式下是Tx holding寄存器).

数据接纳:

和发送相同,接纳的数据帧也是可编程的.它包含一个开端位,5到8个数据位,一个可选的校验位和1到2个中止位(ULCONn中设置).接纳器能够勘探overrun过错parity过错frame过错和中止条件,每一个都会设置一个过错符号.

overrun过错:在旧的数据被读完之前新的数据覆盖了旧的数据

parity过错:接纳器勘探到一个不知道的校验条件

frame过错:接纳数据没有有用的中止位

中止条件:RxDn输入在善于一个帧传输时刻的期间内坚持为逻辑0

中止/DMA恳求发生

每个UART有7个状况信号(Tx/Rx/error):overrun error,parity error,frame error,break,接纳缓冲数据预备,发送缓冲空和发送移位器空.一切都由对应的UART状况寄存器(UTRSTATn/UERSTATn)来指示.

overrun过错,parity过错,frame过错和中止条件都是接纳过错状况.假如UCONn的接纳过错状况中止使能位被置位,每一个过错都能够引起接纳过错状况中止恳求.当一个接纳过错状况中止恳求被勘探到,能够经过读UERSTSTn来辨认.

当在FIFO形式下接纳器将数据从接纳器的移位器发送到接纳器的FIFO寄存器,接纳的数据达到了Rx FIFO的触发线,Rx中止发生.假如在操控寄存器(UCONn)接纳形式被选为1(中止恳求或轮循形式).在非FIFO形式下,将数据从接纳器的移位器发送到接纳holding寄存器会引起Rx中止(中止恳求和轮循形式下).

当发送器从发送器的FIFO寄存器发送数据到移位寄存器时,发送器的FIFO中存留的数据数量小于Tx FIFO的触发线时,Tx中止发生,假如操控寄存器的发送形式被选为中止恳求或许轮循形式.在非FIFO形式下,在中止恳求和轮循形式下从发送器的Holding寄存器发送数据到发送器的移位器会引起Tx中止.

假如操控寄存器的接纳形式和发送形式选为DMA恳求形式,在上面说到的条件下DMA恳求会替代Tx或许Rx中止恳求.

UART过错状况FIFO

UART除了有Rx FIFO寄存器外还有过错状况FIFO.过错状况FIFO会指明在FIFO寄存器中哪个数据在接纳时是过错的.当有错的数据被读出时,过错中止就发生.为了铲除过错状况FIFO,有过错的URXHn和UERSTATn就必须被读出.

波特率的发生:

每个UART的波特率发生器为发送器和接纳器供给特定的时钟.波特率发生器的时钟源能够选为内部体系时钟或许UEXTCLK.换句话说,被除数由UCONn寄存器的时钟挑选确认.波特率的时钟由源时钟(PCLKFCLK/nUEXTCLK)除以16和UART波特率除数寄存器(UBRDIVn)中的16bit除数.

公式如下:

UBRDIVn = (int)( UART clock / ( buad rate x 16) ) –1

( UART clock: PCLK, FCLK/n or UEXTCLK )

接下来看各个寄存器的描绘:

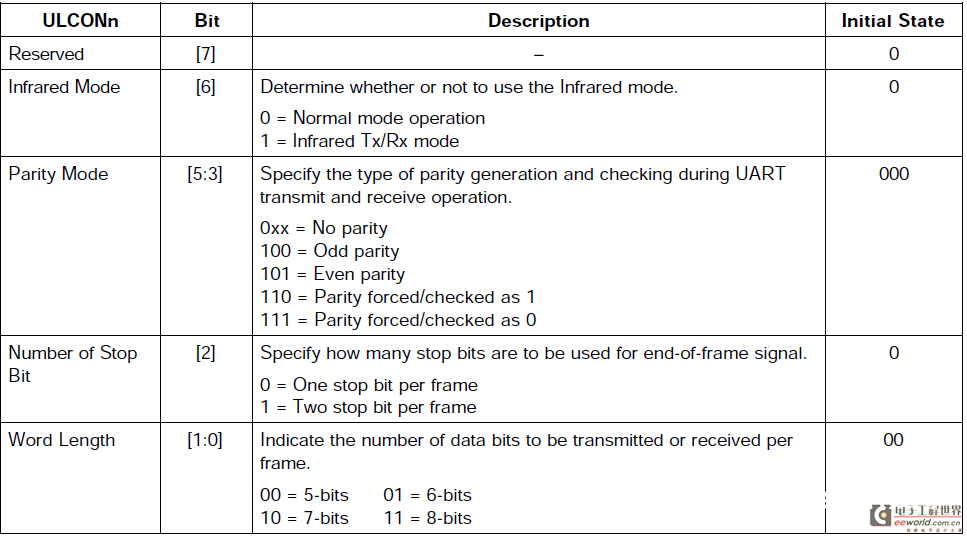

UART LINE CONTROL REGISTER

ULCONn用来装备每一帧数据的格局的:

依据上图,装备如下:

IR mode[6] = 0(一般形式) Parity Mode[5:3] = 0xx(无校验) Number of Stop Bit[2] = 0(一个中止位)

word Length[1:0] = 11(8-bits)

UART CONTROL REGISTER

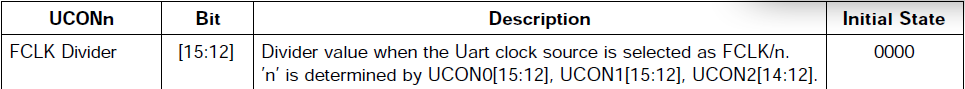

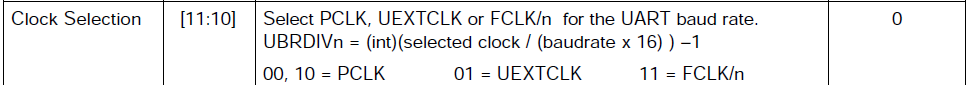

假如Uart的时钟源用FCLK/n,那么FCLK Divider便是装备这个n的

这个当地便是装备Uart的时钟源

Tx Interrupt Type [9] 中止恳求类型:0是Pulse 1是Level

Rx Interrupt Type [8] 中止恳求类型:0是Pulse 1是Level

Rx Time Out Enable [7] 在FIFO使能的情况下,是否翻开Rx Time Out中止 0是封闭 1是翻开

Rx Error Status Interrupt Enable [6] 使能Uart对反常发生中止,比方各种过错 0是封闭 1是翻开

Loopback Mode [5] 回环形式 0是一般形式 1是回环形式

Send Break Signal [4] 是否发送中止信号 0是正常 1是发送中止信号

Transmit Mode [3:2] 决议运用哪种功用来写数据到发送缓冲寄存器 01中止恳求或轮循形式

Receive Mode [3:2] 决议运用哪种功用来从接纳缓冲寄存器读数据 01中止恳求或轮循形式

UART FIFO CONTROL REGISTER