好久没来博客了。一向忙考试了,不过一切都完毕了,暂时能够持续做自己想做的作业了。今日来实验室持续玩ARM了,学习了2103的PLL部分。总的来说,仍是比较简单。当然关于PLL这个硬件的详细完成我还不是很清楚,最初高频没学好喃。。

PLL的概述:

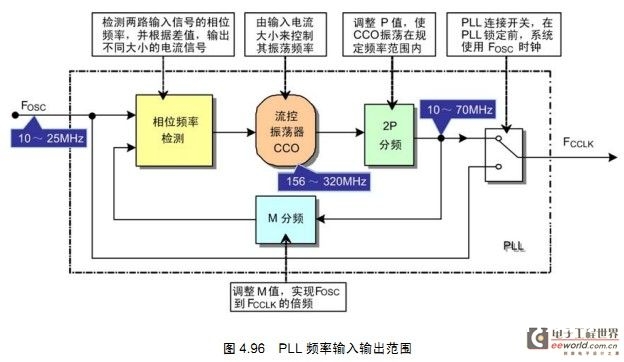

PLL它原本接纳的输入时钟频率规模仅为10MHz~25MHz,然后能够经过一个振荡器(CCO)倍增到规模10MHz~70MHz。倍频器能够是1到32的一个整数,不过实际上没那么多,因为跟LPC2103详细的最大作业频率相关。最高频率为70MHz。CCO的操作频率为156MHz~320MHz。故在PLL内部还有一个额定的分频器在PLL供给所需求的输出频率时使CCO坚持在其频率规模。输出分频器能够设置为2、4、8、16分频发生输出时钟。下图展现了PLL的内部逻辑原理。

PLL激活由PLLCON寄存器操控,PLL倍频器和分频器的值由PLLCFG寄存器操控。因为芯片的一切操作都依赖于PLL(包含看门狗),假如操作PPL过错的话,将引起后续的履行过错。所以咱们需求对它进行维护,维护的操作类似于操作看门狗定时器的馈送序列来完成。PLL在芯片复位时和进入掉电形式后封闭并旁路。PLL的使能只能经过软件完成。程序有必要在装备并激活PLL后等候其确定,然后作为时钟源衔接到PLL。

下面便是PLL的相关寄存器,不多,只要4个。

1。挑选需求操作的处理器操作频率(CCLK),依据处理器的全体要求等各方面来设定。外围器材的时钟频率能够低于处理器频率。

2.挑选振荡器频率(Fosc)。CCLK一定是Fosc的整数倍。

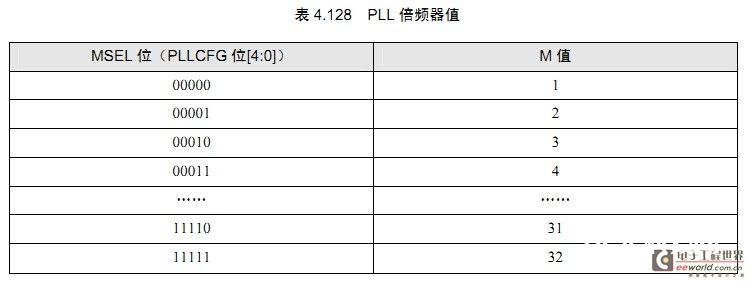

3.核算M值匹配MSEL位。M = CCLK/Fosc。M的取值规模为1~32,在PLLCFG中,写入MSEL的值为M-1.

4.挑选P值以装备PSEL位,使Fcco在界说的约束频率规模内。P有必要是1、2、4或8其间的一个。写入PPCFG中PSEL的值见下表。

PLL的操作也有两种方法。

一是.查询方法

1.PLLCON=1,设定PLL之前,需使能PLL,但不能衔接PLL。

2.设定P和M的值(PLLCFG)

3.发送PLL馈送序列。

4.等候PLL确定–PLLSTAT.10 = 1.

5.PLLCON=3,设定P和M之后,衔接PLL。

6.发送PLL馈送序列,把P和M的值写入硬件。

二是中止方法

1.PLLCON=1,设定PLL之前,需使能PLL,但不能衔接PLL。

2.设定P和M的值(PLLCFG)

3.发送PLL馈送序列。

PLL中止服务程序:

4.PLLCON=3,设定P和M之后,衔接PLL。

5.发送PLL馈送序列,把P和M的值写入硬件。

6.制止PLL中止,回来。