UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种运用广泛的短距离串行传输接口。常常用于短距离、低速、低成本的通讯中。8250、8251、NS16450等芯片都是常见的UART器材。根本的UART通讯只需求两条信号线(RXD、TXD)就可以完结数据的彼此通讯,接纳与发送是全双工方式。TXD是UART发送端,为输出;RXD是UART接纳端,为输入。

UART的根本特点是:(1)在信号线上共有两种状况,可分别用逻辑1(高电平)和逻辑0(低电平)来区别。在发送器空闲时,数据线应该坚持在逻辑高电平状况。(2)开端位(Start Bit):发送器是经过发送开端位而开端一个字符传送,开端位使数据线处于逻辑0状况,提示接受器数据传输行将开端。

(3)数据位(Data Bits):开端位之后便是传送数据位。数据位一般为8位一个字节的数据(也有6位、7位的状况),低位(LSB)在前,高位(MSB)在后。(4)校验位(parity Bit):可以以为是一个特别的数据位。校验位一般用来判别接纳的数据位有无过错,一般是奇偶校验。在运用中,该位常常撤销。

(5)中止位:中止位在最终,用以标志一个字符传送的完毕,它对应于逻辑1状况。(6)位时刻:即每个位的时刻宽度。开端位、数据位、校验位的位宽度是共同的,中止位有0.5位、1位、1.5位格局,一般为1位。(7)帧:从开端位开端到中止位完毕的时刻距离称之为一帧。

(8)波特率:UART的传送速率,用于阐明数据传送的快慢。在串行通讯中,数据是按位进行传送的,因而传送速率用每秒钟传送数据位的数目来表明,称之为波特率。如波特率9600=9600bps(位/秒)。

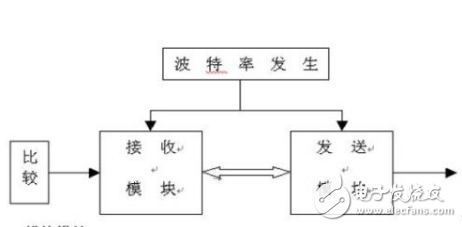

FPGA UART体系组成 :如下图所示,FPGA UART由三个子模块组成:波特率发生器;接纳模块;发送模块;

模块规划:体系由四部部分组成:顶层模块;波特率发生器;UART接纳器; UART发送器.

异步收发器的顶层模块由波特率发生器、UART接纳器和UART发送器构成。UART发送器的用处是将预备输出的并行数据依照根本UART帧格局转为TXD信号串行输出。UART接纳器接纳RXD串行信号,并将其转化为并行数据。

波特率发生器便是专门发生一个远远高于波特率的本地时钟信号对输入RXD不断采样,使接纳器与发送器坚持同步。波特率发生器实际上便是一个分频器。可以依据给定的体系时钟频率(晶振时钟)和要求的波特率算出波特率分频因子,算出的波特率分频因子作为分频器的分频数。波特率分频因子可以依据不同的运用需求更改。

因为串行数据帧和接纳时钟是异步的,由逻辑1转为逻辑0可以被视为一个数据帧的开端位。但是,为了防止毛刺影响,可以得到正确的开端位信号,有必要要求接纳到的开端位在波特率时钟采样的过程中至少有一半都是归于逻辑0才可确定接纳到的是开端位。因为内部采样时钟bclk周期(由波特率发生器发生)是发送或接纳波特率时钟频率的16倍,所以开端位需求至少8个接连bclk周期的逻辑0被接纳到,才以为开端位接纳到,接着数据位和奇偶校验位将每隔16个bclk周期被采样一次(即每一个波特率时钟被采样一次)。假如开端位的确是16个bclk周期长,那么接下来的数据将在每个位的中点处被采样。