PCI-E规范自从推出以来,1代和2代规范已经在PC和Server上逐步遍及,用于满意高速显卡、高速存储设备关于高速数据传输的要求。出于支撑更高总线数据吞吐率的意图,PCI-SIG安排在2010年拟定了PCI-E 3.0,即PCI-E 3代的规范,数据速率到达8Gbps。现在,PCI-E 3.0已经在Server和PC上广泛使用,而下一代PCIE4.0的推出也是指日可下。

那么PCI-E 3.0总线终究有什么特色?关于其测验有什么特别的当地呢?咱们这儿就来讨论一下。

拟定PCI-E 3代规范的意图首要是要在现有的廉价的FR4板材和接插件的基础上供给比PCI-E 2代高一倍的有用数据传输速率,一起坚持和原有1代、2代设备的兼容。别看这是个简略的意图,但完成起来可不简单。

咱们知道,PCI-E 2代在每对差分线上的数据传输速率是5Gbps,相关于1代数据速率的两倍;而PCI-E 3代要相关于2代把速率也进步一倍,天经地义的是把数据传输速率进步到10Gbps。可是便是这个10Gbps带来了很大的问题,因为PC和Server上出于本钱的考虑,遍及运用廉价的FR4的PCB板材以及廉价的接插件,假如不替换板材和接插件,很难确保10Gbps的信号还能在本来的信号途径上牢靠地传输很远的间隔(典型间隔是15~30cm)。因而PCI-SIG终究决议把PCI-E 3代的数据传输速率定在8Gbps。可是8Gbps比着2代的5Gbps并没有高一倍,所以PCI-E协会决议在3代规范中把在1代和2代中运用的8b/10b编码去掉。

咱们知道,在PCI-E 1代和2代中为了确保数据的传输密度、直流平衡以及内嵌时钟的意图,会把8bit数据会编码成10bit数据传输。因而,5Gbps的实践有用数据传输速率是5Gbps×8b/10b=4Gbps。这样,假如在PCI-E 3代中假如不运用8b/10b编码,其有用数据传输速率就能比 2代的4Gbps进步1倍。可是这样问题又来了,数据假如不经编码传输很难确保数据传输密度和直流平衡,接纳端的时钟康复电路也很简单失锁。为了处理这个问题,PCI-E 3代里边选用了扰码的办法,即数据传输前先和一个多项式进行异或,这样传输链路上的数据就看起来就比较有随机性,到了接纳端再用相同的多项式把数据康复出来。

通过上述办法,PCI-E 3代就能够用8Gbps的传输速率完成比2代的5Gbps高1倍的数据传输速率。实践使用中PCI-E 3代的总线上也依然有数据编码,不过选用的是128b/130b的编码,编码功率很高,由此丢失的总线有用带宽比8b/10b编码小多了。

PCI-E 3.0 发送及接纳端的改变

可是问题远没有结束,即便数据速率只要8Gbps,要在原有的廉价PCB和接插件上完成牢靠传输也还要处理一些新的问题。其间最大的问题是信号的损耗,FR4板材对信号高频成分有很大衰减,而信号速率越高,其高频成分越多,所以衰减也就更凶猛。下图是不同速率的信号通过10英寸的FR4板材的PCB传输今后信号的眼图,咱们能够看到8Gbps的信号在接纳端基本上看不到眼图了,更不要说进行有用的数据接纳。

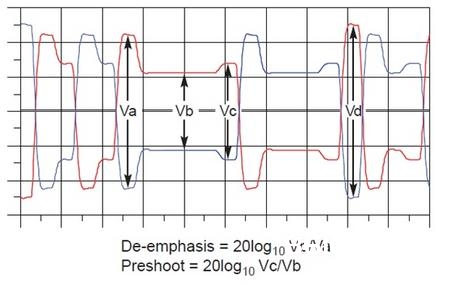

为了处理这个问题,在PCI-E的1代和2代中运用了去加剧(De-emphasis)技能,即信号的发射端(TX)在发送信号时对跳变bit(代表信号中的高频成分)加大起伏发送,这样能够部分补偿一下传输线路对高频成分的衰减,然后得到比较好的眼图。PCI-E 1代中选用了-3.5db的去加剧,PCI-E 2代中选用了-3.5db和-6db的去加剧。而关于3代来说,因为信号速率更高,需求选用愈加杂乱的去加剧技能,因而除了跳变bit比非跳变bit起伏增大发送以外,在跳变bit的前1个bit也要增大起伏发送,这个增大的起伏一般叫做Preshoot。下图是PCI-E 3代中选用的预加剧技能对波形的影响的比方(参考资料:PCI Express® Base Specification 3.0 )。

为了应对杂乱的链路环境,PCI-E 3代中规则了共11种不同的Preshoot和De-emphasis的组合,每种组合叫做一个Preset,实践使用中Tx和Rx端能够在Link Training阶段依据接纳端收到的信号质量洽谈出一个最优的Preset值。下图是11种Preset的组合(参考资料:PCI Express® Base Specification 3.0)。比方P4代表没有任何预加剧,P7代表最凶猛的预加剧。

那做了这些作业就够了吗?通过试验发现,仅仅在发送端对信号高频进行补偿仍是不行,所以PCI-E 3代规范中又规则在接纳端(RX端)还要对信号做均衡(Equalization),然后对线路的损耗进行进一步的补偿。均衡电路的完成难度较大,曾经首要用在通讯设备的背板或长电缆传输的场合,现在也逐步开端在计算机范畴使用,比方USB3.0中和SATA 6G中也选用了均衡技能。下图是PCI-E 3.0里对均衡器的频响特性的要求。咱们能够看到均衡器的强弱也有许多档可选,在Link Training阶段TX和RX端会洽谈出一个最佳的组合(参考资料:PCI Express® Base Specification 3.0)。

通过各种信号处理技能的结合以及很多的试验,PCI-E 3.0总算开始完成了在现有的FR4板材和接插件的基础上供给比PCI-E 2代高一倍的有用数据传输速率。但咱们一起也看到,PCI-E 3代的芯片会变得愈加杂乱,体系规划的难度也也更大。怎么确保PCI-E 3代总线作业的牢靠性和很好的兼容性,就成为规划和测验人员面对的严峻应战。