10多年以来,我一向坚定地支撑根据FPGA的硬件仿真体系,并在2013年一向竭尽全力地宣扬其优势。自那今后,我已成为通晓各类硬件仿真专业知识的参谋,但现在来谈论FPGA硬件仿真体系与定制硅硬件仿真体系之间的差异好像有些缓不济急。

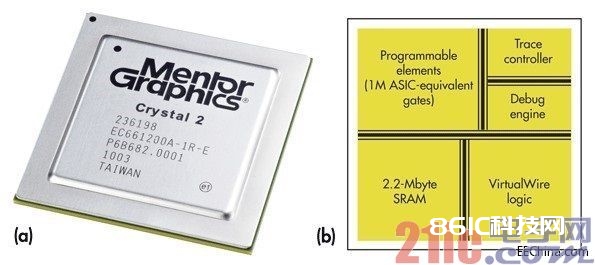

商用FPGA硬件仿真器与定制硅硬件仿真器之间的底子差异在于映射被测规划(DUT)的中心单元。望文生义,定制硅硬件仿真器是根据定制器材而造,不行用于商业用途。定制硅硬件仿真器便是选用两个不同品种傍边的一个来完成的。

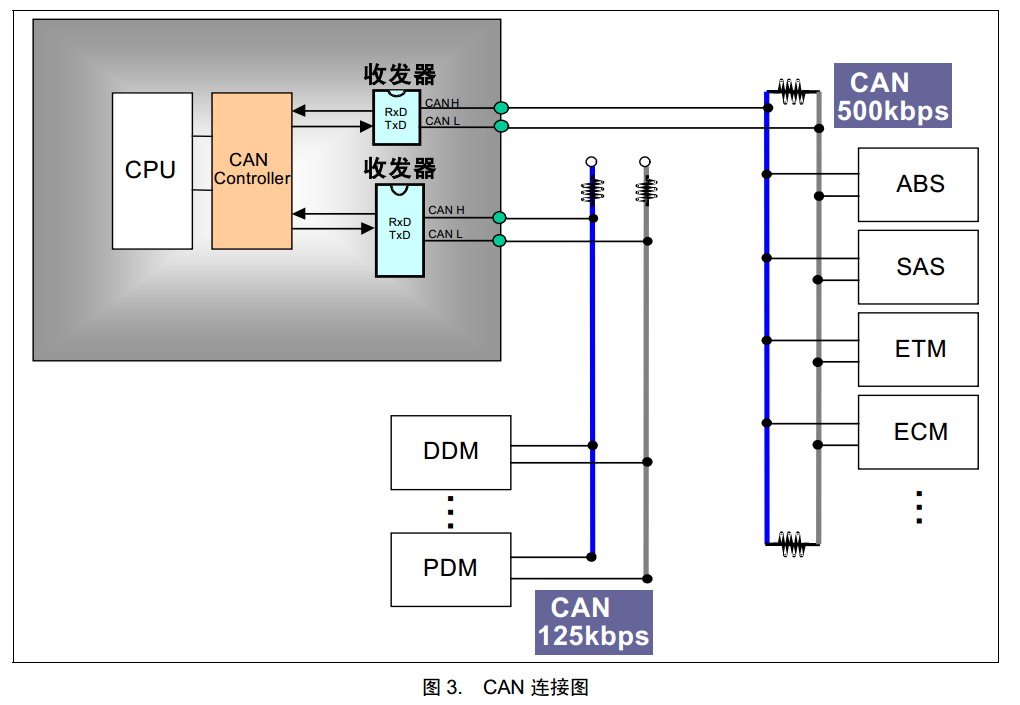

在第一类中,中心单元是专为硬件仿真运用而规划的定制FPGA,但通用FPGA是个糟糕的挑选。Mentor Graphics供给一种称为Crystal2的此类器材,并称之为定制片上硬件仿真器,如图1。在第二类中,中心单元包含很多简略的布尔处理器,此类处理器在巨大的内存中履行规划数据结构存储。Cadence供货商称之为“根据处理器的硬件仿真器”。很显然,定制FPGA硬件仿真器与商用FPGA硬件仿真器具有一些相似之处,但依然具有共同的功用。

图1:Mentor Graphiscs Crystal2“定制片上硬件仿真器”。

定制FPGA硬件仿真器

定制FPGA硬件仿真器由法国草创公司MetaSystems(1996年被Mentor Graphics收买)最早开发并商业化,选用不同于Xilinx和Altera所供给的共同FPGA。该硬件仿真器是根据定制硅上仿真器架构,专为包含整个硬件仿真器(包含可装备单元、部分互连矩阵、嵌入式多端口内存、I/O通道、带勘探电路的调试引擎和时钟发生器)的仿真运用而规划。

这种办法运用了三个立异点,每个立异点都可供给共同的优势:

●可编程单元的内部互连网络;

●定制FPGA的外部互连网络和I/O结构;

●DUT调试引擎。

可编程单元的内部互连网络

可编程单元的互连网络包含两个不同分级层:坐落查找表(LUT)及其集群(Cluster)等级的低层;以及更大块的LUT集群,即所谓的叠块的高层。

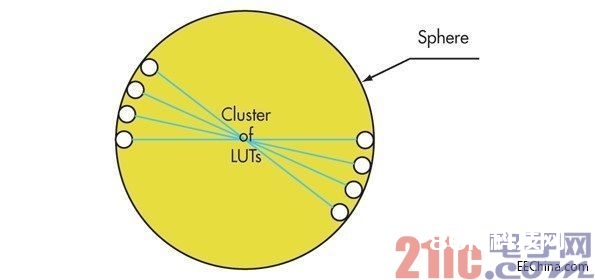

能够用空间类推法来描绘低层。假定一切的LUT都坐落球体表面上,任何两个LUT互连都有必要穿过球体中心,则不管两个LUT坐落何处,互连导线的长度一直相同。(图2)。

图2:描绘低层空间类推法。

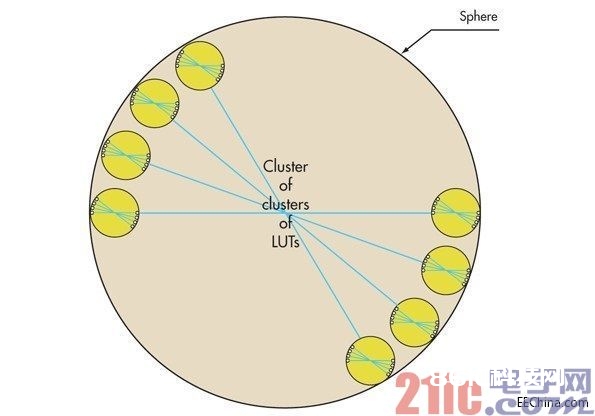

上述类推法延伸到更高层级,LUT集群能够散布在更大球体的表面上,并选用相同的办法互连(图3)。这基本上是一个重复相同形式的分形图,从外到内或从内到外移动。高层经过专利结构互连叠块,供给类似于低层固有的优势。

图3:高层级空间类推法。

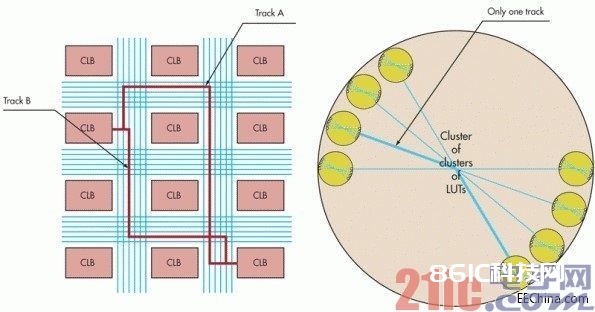

高层经过细小的交互开关矩阵(有些类似于片上网络(NoC)架构)互连叠块,因此使该结构有别于传统网格互连网络。这种办法能够保证布线可猜测、快速和无拥塞。

此外,时钟树经过导线衔接到独立于数据途径的专用途径,因此能够猜测和重复时序,并经过结构防止时序违规行为,由于数据途径比时钟途径更长。不行猜测的时序和坚持时刻违规行为会损坏商用FPGA的可用性。

与商用FPGA的结构比较,定制办法能够保证时序确实定性和可重复性。该办法消除了布局束缚,保证完成简略的布线和快速的编译(图4)。

图4:商用FPGA与定制的比照。

多层互连网络对高容量进行权衡,现可用于最大的FPGA,并支撑快速和无拥塞的FPGA布局和布线(PR)。能够在约五分钟内对一个定制FPGA进行布局布线。即便将最大FPGA的填充率下降至50%或以下,PR仍或许需求几个小时。

毫无疑问,与运用当时市场上最大的商用FPGA比较(例如Xilinx Virtex-7 XC7V2000T),映射10亿ASIC等效门规划将需求更多的定制FPGA器材。实践差异或许会小于经过比较内部资源(例如LUT)预算的成果,由于定制FPGA的使用率挨近100%,而商用FPGA则为50%左右。

以下要素有助于减轻容量距离:内置的VirtualWire逻辑(用于I/O数最大化而不是耗费LUT);内置的调试引擎(节省留给DUT映射的名贵的可装备资源);以及一个有用的布线器。

这两种技能都获益于在多个PC分配PR,但定制办法依然具有优势。在一系列定制FPGA上对10亿AS%&&&&&%等效门规划进行布局和布线(在大型模仿场进行操作)或许需求30分钟。在一系列较小的Xilinx Virtex-7上对相同的规划进行布局和布线将需求几个小时。

具有了该技能,定制FPGA硬件仿真器供货商能够管控运营,优化和定制PR软件,而这是商用FPGA硬件仿真器供货商无法做到的。由于后者受FPGA厂商分配。

片上硬件仿真器的外部互连网络

片上硬件仿真器的外部互连网络是根据所谓的VirtualWire技能。凭借VirtualWire,FPGA集合会主动编译为一个巨大的FPGA,该FPGA不会遭到可损坏经过传统办法互连的一系列等效FPGA的潜在时序问题的影响。该技能在开发时仅可用于选用商用FPGA的硬件仿真器。现在,相同的技能已嵌入到片上硬件仿真器。

VirtualWire是根据多个再归纳流程(时序、存储器、互连),此类流程将DUT转换为映射到一系列定制片上硬件仿真器器材的功用等效的规划。

时序再归纳运用正确性保护转换来从头守时用户的规划,经过引进单个高速时钟来保护其免受不精确的FPGA推迟。此外,还消除了传统硬件仿真体系的坚持时刻问题。

存储器再归纳完成低成本施行各类存储器(包含宽多端口RAM),无需构建定制存储卡或运用FPGA存储器。多路复用和存储器同享支撑运用快速且廉价的常见SRAM芯片进行存储器硬件仿真。

互连再归纳经过在器材固定和有限数量的I/O管脚上添加传输中的I/O信号数,来扩展器材间的通讯带宽,并以最大速度进行衔接。终究成果是,器材使用率明显进步到约100%,防止拥塞并保护DUT完整性。

在每个I/O管脚添加I/O信号类似于在FPGA原型板上施行I/O数最大化的办法。

VirtualWire完成更为杂乱。该技能:

●经过保证部分时序正确性完成大局时序正确性和体系可扩展性;

●供给为一切触发器计时的虚拟时钟,分配单个同步低偏移时钟;

●信号布线和调度受编译器操控,由于信号有必要经过已知数量的FPGA。

VirtualWire完成还扩展了带宽,然后可进步FPGA和导线的使用率。多路复用技能能够扩展各级封装的互连带宽,从FPGA间和板间到机箱间,使得分区更简单。

此外,还供给相同的多路复用技能来访问存储器。经过对数据总线进行多路复用,能够运用常见的SRAM芯片构建宽存储器。能够运用SRAM芯片施行多端口存储器。能够在布线和调度过程中整合存储器调度。

集成规划调试功用

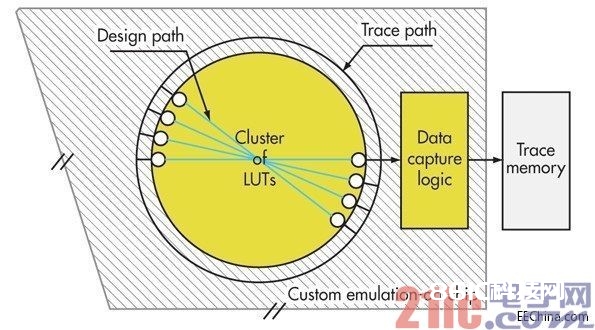

第三个立异触及定制办法的集成规划调试功用。该办法是根据在芯片内部施行的实时智能数据捕获和安装在仿真板上每个芯片周围的盯梢存储器,能够保证监控DUT的一切单元。这是经过结构而非编译内部探头完成的。而且还防止了硬件仿真速度下降。

经过将一切LUT和嵌入式存储器输出衔接到硅中片上信号勘探电路完成全面监控,无需在编译时进行布线。勘探电路顺次将勘探数据定向到快速内存芯片库,该库耦合到安装在仿真板上的定制片上硬件仿真器器材。这样就可预留布线资源来构建规划图片,进步可从头装备硬件的功率(图5)。

图5:预留布线资源来构建规划图片,进步可从头装备硬件的功率。

经过集成触发机制和带图形途径浏览器的内置逻辑分析仪来增强规划调试功用,以加速辨认难以发现的缺陷。默许情况下,片上硬件仿真器启用了触发寄存器、强制与免除(force/release)、内存/寄存器读写以及断点保存与康复。

片上硬件仿真器的缺陷

惋惜的是,与最大的商用FPGA比较,定制办法也有缺陷,由于定制芯片的容量密度较低。一个缺陷是,要映射任何给定的规划尺度,硬件仿真器将需求更多的FPGA,然后导致物理尺度更大、分量更重。

粗略地讲,与具有相同规划容量的商用FPGA硬件仿真器比较,尺度大一个数量级。分量约重5倍。功耗约高4倍以上,尽管份额较低。

商用FPGA硬件仿真器的原始时钟速度更快。据揭露数据显现,好像比片上硬件仿真器快两倍。相同,这源于两种芯片的容量差异。事实上,具有更大容量的现成FPGA能够包容规划的更大部分,并支撑更少的器材以习惯整个规划。终究成果是,互连导线更短,传达推迟更快。

可是,若要使用这种功用,则耗时的手动分区一直是必要的。假如没有优化分区和消除跳距——即组合导线跨过多个FPGA——那么在商用FPGA硬件仿真器中,仿真速度或许会下降。原始速度是一回事。实在环境中的实践功能/带宽则是另一回事。