导言

遥测信号源的首要功用是模仿弹载遥测信息。从技能完结上,可将信号源分为模仿信号源、数字信号源和DDS信号源。其间DDS信号源是现代信号源的开展方向。DDS技能(直接数字频率组成)是近年来敏捷开展起来的一种新的频率组成法,具有可编程、易于完结各种数字化调制(如PSK,FSK等高精度的数字调制),频率分辨率高、转化速度快、安稳度高,相位噪声低以及集成度高级长处。近年来,跟着遥测技能的开展,遥测产品逐步呈现出小型化、标准化、系列化等运用需求。因而,为满意运用需求,遥测信号源有必要可以供给多样的被测信号类型,依据被测模块参数的改动进行实时调整,完结一一对应。而传统的遥测信号源在规划上缺少灵敏性、通用性,被测参数的多样性和实时性差,无法满意遥测产品的开展需求。针对这一点,本文提出了以FPGA(现场可编程门阵列)和DDS专用芯片为中心的可编程遥测信号源。

1、FPGA及DDS根本作业原理

一般传统的信号源都选用谐振法,即用具有频率挑选性的回路来发生正弦振动,取得所需频率。这种信号源输出波形单一,且频率安稳度和准确度较差,因而传统的信号源现已越来越不能满意现代遥测产品的丈量需求。而选用DDS技能规划的遥测信号源可以满意波形多样化,频率、相位灵敏可装备的要求,且频率安稳度高。

1.1 FPGA

FPGA是一种高密度的可编程逻辑器材。经过20多年的开展,FPGA的逻辑规划现已从开端的1000个可用门开展到现在的1000万个可用门,选用Verilog HDL言语进行规划,在写鼓励和建模方面存在很大优势。FPGA的根本组成部分有可编程输入/输出单元、根本可编程逻辑单元、嵌入式块RAM、丰厚的布线资源、底层嵌入功用单元和内嵌专用硬核等。FPGA器材在结构上由逻辑功用块排列为阵列,经过可编程的内部连线衔接这些功用块来完结必定的逻辑功用。因为FPGA器材集成度高,开发和上市周期短,在数字规划和电子出产中得到敏捷遍及和运用,曾在高密度的可编程逻辑器材领域中名列前茅。

Altera公司是现在商场上出产FPGA芯片的首要供货商之一,为用户供给了完善的开发体系和杰出的售后支撑服务,有着老练的系列产品。该公司的可编程逻辑产品可以分为高密度FPGA、低本钱FPGA和CPLD等三类。相关于低本钱FPGA来说,高密度FPGA首要用于中高端的路由器和交换机中,价格相对偏高,CPLD尽管价格较低,但布线资源有限,无法适用于电路杂乱的时序功用规划。Cyclone(飓风)系列是Altera公司推出的一款低本钱FPGA,首要定位在很多且对本钱灵敏的规划中。Cyclone EP1C6是Altera推出的一款高性价比FPGA,作业电压为3.3 V,内核电压为1.5 V,其密度为5980个逻辑单元,包含20个128×36 b的RAM块(M4K模块),总的RAM空间到达92 160 b,内嵌2个锁相环电路和一个用于衔接SDRAM的特定双数据率接口。

1.2 DDS及其芯片

DDS选用了不同于传统频率组成办法的全数字结构。它开端是在20世纪70年代由美国学者J.Tierncy等人提出的,它是继直接频率组成和直接频率组成之后,跟着数字集成电路和微电子技能敏捷开展起来的第三代频率组成技能。DDS是指从相位量化概念动身直接组成所需波形,有效地处理了许多模仿组成技能无法处理的问题。

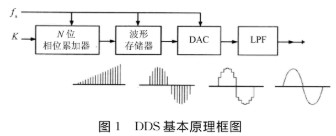

DDS是建立在采样定理基础上,首要对需求发生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后经过查表读取数据,再经D/A转化器转化为模仿量,将保存的波形从头组成出来。DDS根本原理框图如图1所示。

现在AD公司是干流DDS芯片商场的最大供货商,它供给的很多DDS集成芯片以其较高的性价比取得了极为广泛的运用。AD公司的DDS产品首要有AD983X,AD985X和AD995X三大系列。关于AD985X系列来说,其系列产品尽管功用较好可是功耗偏高,而AD995X系列尽管功耗较低,但其价格高于AD983X系列,AD983X系列是低价格低功耗型产品。在AD983X系列中。AD9833的最大功耗仅为20 mW。一起,AD9833还具有外围电路简略、频率和相位可编程等特色。AD9833经过3线SPI串口进行写操作,内部有5个可编程寄存器,其间包含1个16位操控寄存器,2个28位频率寄存器和2个12位相位寄存器。用户可以经过16位操控寄存器设置所需的功用。AD9833的模仿输出为fout:

fout=(fCLK/228)×FREQREG (1)

式中FREQREG为所选频率寄存器中的频率字。

信号相移为pout:

pout=(2π/4 096)×PHASEREC (2)

式中PHASEREC为所选相位寄存器中的相位字。

2、依据FPGA和DDS芯片的可编程遥测信号源

传统的遥测信号源在规划上可编程性差,在很大程度上影响了其灵敏型和通用性,一起也造成了资源的严峻糟蹋。而本计划的规划具有较强的可编程性,可以灵敏装备,通用性较强,大大节省了资源本钱。

该遥测信号源的硬件电路首要由低本钱FPGA和DDS专用芯片构成,软件选用Verilog言语编程。关于软件部分来说,该信号源的操控接口和操控字编程是软件编程的重要部分。FPGA操控接口经过编程完结串口通信协议,预设操控字有必要依照操控接口的通信协议串行输出给DDS专用芯片,DDS芯片才干接纳操控字信息,并依据接纳到的操控字信息输出所需的波形。

2.1 遥测信号源的硬件构成

遥测信号源首要包含以下三个组成部分。

(1)按键电路。它首要是向FPGA部分运送操控信息。一部分按键供给波形挑选信息,另一部分供给需求输出波形的频率信息。

(2)体系FPGA操控中心。FPGA是体系的中心操控部分。当FPGA接纳到按键信息后,发送相应的操控信息给DDS芯片。经过程序规划,FPGA芯片EP1C6T144可完结灵敏装备。

(3)DDS电路。该部分首要选用AD9833芯片来建立外围电路。依据接纳到的FPGA操控信息发生所需波形信号,并将其输出。

体系整体框图如图2所示。

在该体系中,用户可经过波形挑选按键输出默许频率的正弦波、三角波、方波等波形,假如在运用的过程中,需求输出不同频率的波形,则可以经过频率挑选按键来完结。在FPGA操控模块中,当FPGA接纳到数据或状况改动的信息后,所设置的相应的变量赋值会发生相应的改动,然后将相应的操控字输出给AD9833芯片,AD9833接纳到操控字后经过直接数字频率组成,终究输出所需的波形。

2.2 遥测信号源的操控接口

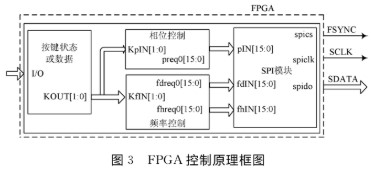

DDS芯片AD9833为3线SPI接口,关于一些微处理器来说可以直接与其衔接,但关于FPGA来说,有必要经过对SPI协议进行编程完结。因而在FPGA操控中,对SPI进行了模块化规划,无论是相位操控字输出仍是频率操控字的输出都需经过SPI模块后,依据SPI协议进行输出。FPGA操控原理框图如图3所示。

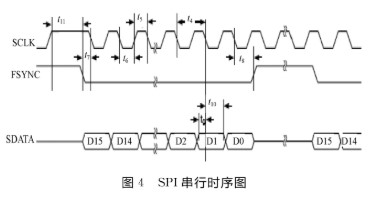

在FPGA中,首要接纳到外部的按键信息,按键状况或数据模块被触发,依据该模块供给的信息,在相位、频率操控模块内,对相应的寄存器(preq0,fdreq0,fhreq0)进行赋值,完结相位及频率操控字的装备,并输入到SPI模块,经过SPI模块进行SPI协议输出给AD9833,操控输出有必要满意AD9833的时序操控,时序如图4所示。

在串行时钟输入SCLK(spiclk)的操控下,SCLK为高,使能信号FSYNC(spics)为低时,SDATA(spido)输出)开端输入数据,数据以16位字的方式写入AD9833。FSYNC可以在多组16个SCLK脉冲期间坚持低电平,传输接连的16位字流,比及数据传输结束后在终究一个字的第16个SCLK下降沿变高。

2.3 遥测信号源的软件操控字

关于灵敏可装备,通用性强的遥测信号源来说,其频率、波形等参数的实时改动是必不可少的。而体系要完结这些参数的实时改动,就有必要将操控字进行相应的改动。如正弦波的操控字为十六进制数0008,三角波的操控字为十六进制数000A,方波的操控字十六进制数0028。

由AD9833模仿输出频率的核算公式(参阅式(1))可知,假如选用20 MHz的晶振作为AD9833的主频时钟来输出10 kHz的正弦波信号,则可核算出频率字FREQREG的十六进制数为20C49,假如软件设计时选用AD9833的频率寄存器0和相位寄存器0,则加上寄存器标识后,FPGA写入AD98 33的频率字高位十六进制数为4008,低位十六进制数为4C49。在给频率寄存器写入数据前,若给操控寄存器写入十六进制数2000,则可将频率寄存器设置成完好的28位来运用,若给写入十六进制数0000,则频率寄存器可以作为两个14位寄存器来运用。相位字可依据式(2)来核算。当相位偏移为0°时,相位字PHASEREC为十六进制数D000(相位寄存器的标明为1101);相位偏移为180°时,相位字PHASEREC为十六进制数D800。

3、 仿真验证

仿真是在QuartusⅡ环境下,运用其自带的仿真软件对整个工程进行功用仿真。

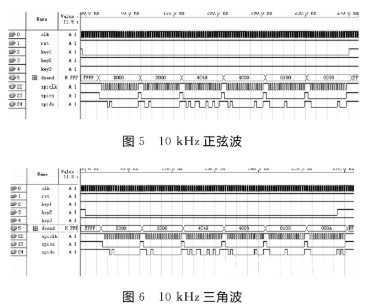

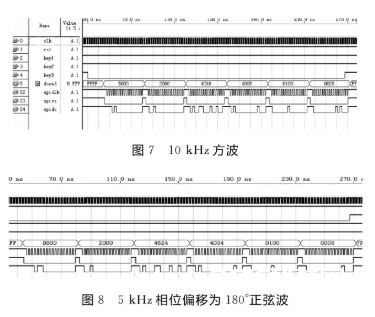

仿真选用20 MHz的晶振作为AD9833的主频时钟来输出相位偏移为零、频率为10 kHz的正弦波、方波、三角波,以及相位偏移为180°的5 kHz的正弦波,成果别离如图5~图8所示。

经过模仿输出频率公式可核算频率为5 kHz时,频率字FREQREG的十六进制数为10624,FPGA写入AD9833的频率字高位十六进制数为4004,低位十六进制数为4624。

4 、定论

本文提出了依据FPGA和DDS芯片的遥测信号源。该信号源首要由Cyclone EP1C6和AD9833芯片来建立硬件电路,选用Verilog言语完结编程,经过对FPGA进行操控使其输出数据给DDS芯片,终究完结所需波形的输出。仿真标明该遥测信号源可以灵敏、方便地输出频率规模为0~12.5 MHz的频率、相位可调的正弦波、三角波、方波信号。此计划的参数化没计,极大方便了对所需波形数据的更改,增强了信号源的灵敏性。尽管该信号源可以输出频率、相位灵敏可变的正弦波、方波、三角波,但没有完结恣意波形的输出。因而今后研讨方向是完结对恣意波形的规划,以添加信号源的灵敏可装备性,进一步增强其通用性。

责任编辑:gt