大约在 40 年前,Comprehensive Computing Systems and Services公司在市场上推出了首个名为 TEGAS 的商业数字软件仿真器,该设备首要用于测验生成和软件仿真体系。这一对门级电路进行仿真的体系由一个小型专家团队开发,而在此之前只需针对晶体管级电路进行仿真的模仿仿真软件。TEGAS 是其专用的描绘言语。这种言语仅用于生成数字电路测验向量。终究,仍须经过原型板进行规划验证。

跟着 20 世纪 80 时代前期核算机辅佐工程 (CAE) 职业的鼓起,数字软件仿真器或逻辑软件仿真也在电子工程界盛行起来,成为规划验证的首要手法。到 20 世纪 90 时代末,数字软件仿真器逐步开展演变为寄存器传输级 (RTL) 软件仿真器,这种软件仿真器支撑两种盛行的硬件描绘言语 (HDLs)—— Verilog 和 VHDL。现有的 EDA(电子规划自动化,CAE 和 CAD 的产品)供货商用了十多年的时刻在同一个东西中支撑这两种言语。现在,Synopsys、Cadence 和 Mentor Graphics这三家大型 EDA 供货商,都供给各自的 HDL 软件仿真器,在市场上出现鼎足之势的状况。

多年来一系列的改善使得 HDL 软件仿真器变得愈加完美。现在,它是一款不可限量的东西,是规划验证和假定剖析中必不可少的东西,但其仍是有本身的局限性,即规划规划不能超过 1 亿个 ASIC 等效门。这种约束较为随意,事实上,依然能够对更大型的规划进行软件仿真,仅仅履行速度奇慢无比。

一个示例

若要运用在 10 Hz 下运转的现代软件仿真器来仿真在 100 MHz 下运转的 1 亿 ASIC 门规划上的一秒钟的实在数据,这绝非易事。在这种规划复杂度下,或许需求花费 1 千万秒的时刻。即 2,778 小时,或许 115 天。一秒钟的 100 MHz 实在数据等于 1 亿个时钟周期,这个数字相当大,或许会超出处理典型测验渠道的要求。在处理典型测验渠道时,一毫秒或许更短时刻就足够了,在大内存装备的最新 PC 上运转时,则会将履行时刻缩短至一天或更短。这是个合理的方针。

HDL 软件仿真器能够在 PC 场中并行运转,每个 PC 会处理功用完善的测验渠道。半导体公司有不计其数台 PC 构成的核算场全天运转。

但 1 亿周期仍不足以处理嵌入式软件规划。因为处理软件在本质上为串行流程,所以关于这项使命来说,有必要按次序履行数十亿周期。但是,带有 HDL 软件仿真答应的 PC 场却力所不及。软件程序无法在子集中进行拆分,再并行运转。

那么,要怎么验证 SoC 规划的嵌入式软件呢?

进入硬件仿真时代

硬件仿真其实由来已久,它给规划人员在流片前供给了一种更为精确的电路行为描绘,因为硬件仿真是经过实在的电路和逻辑来完结规划。硬件仿真始于 20 世纪 80 时代末,在 20 世纪 90 时代末盛行,其时首要是经过商业 FPGA 进行完结,用于验证需求较长测验周期的处理器和图形规划。它们也遇到比如电路建模难度高以及可靠性低一级各种问题。其本钱也较为昂扬,并且作为单用户资源,其出资报答较低。但是,硬件仿真器的超卓履行速度仍使其成为长处理周期的必要东西。

仍是之前的示例,在 1 MHz 下运转的硬件仿真器需求花费 100 秒来履行 1 秒钟的实在数据以及处理 1 亿次周期。硬件仿真器能够在一小时左右的时刻内发动操作体系。并且,硬件仿真器的投入比从头流片廉价得多。

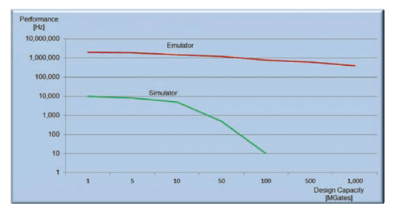

图 1:不同规划规划下软件仿真与硬件仿真功用比照

HDL 软件仿真器因为缓存缺失和内存交流,其履行速度会跟着规划规划添加而急剧下降。不过与之不同的是,在此情况下,硬件仿真器的功用只会遭到细微影响(见图 1)。

因为商用 FPGA 硬件仿真器有必定的约束性,定制芯片硬件仿真器由此应运而生。这种硬件仿真器首要有两种不同类型:由 Mentor Graphics 供给的定制 FPGA 硬件仿真器,又称片上硬件仿真器;以及由 Cadence Design Systems 供给的根据处理器的硬件仿真器。一起,Synopsys 也支撑运用比规范 FPGA 硬件仿真器更为先进且功用有所增强的最新商用 FPGA 硬件仿真器。

直到十年前,硬件仿真器才在电路硬件仿真 (ICE) 形式中被独自布置为物理测验环境。因为当流片供给鼓励和处理响应时,被测规划 (DUT) 将终究驻留在此环境中。因为难以进行设置,%&&&&&%E 形式现在并不常见,而对愈加灵敏的测验环境的需求却在不断添加。运用硬件桥没有可控性/可再现性,并且因为安装时刻和保护本钱的添加,其还会添加测验环境的复杂度。因为可组成的测验渠道能在硬件仿真器内部进行映射,并且无需依靠外部环境便能够硬件仿真器的最高速度履行,因而该测验渠道区域还有其他可行的代替计划。不过惋惜的是,它们不易开发。

根据业务的验证或加快(TBV 或 TBX)是业界最看好的办法,具有两方面的优势。首要,能选用少一个数量级的代码行,在更高笼统层次写入测验渠道,简洁而又不易犯错。其次,因为在硬件仿真器内部映射晶体管的总线功用模型 (BFM) 完结了急剧加快,这些测验渠道比传统 RTL 渠道履行更快。另一个好处是,当用户切换规划或新用户登录时,TBV 或 TBX 不需求人为监督来处理速度适配器。这种方法也合适于长途拜访。

何时运用软件仿真,何时运用硬件仿真

HDL 软件仿真器适用于规划周期前期阶段的硬件调试,前期阶段的规划首要专心于模块等级。凭仗易用、快速设置、极速规划编译等特色,它们能够极端灵敏地调试硬件规划。它们还支撑每天进行屡次规划迭代…只需规划规划合理。但在数千万门等级时会出现问题,这在现在看来仅仅典型的体系级规划验证。如上所述,它们并不合适嵌入式软件验证。

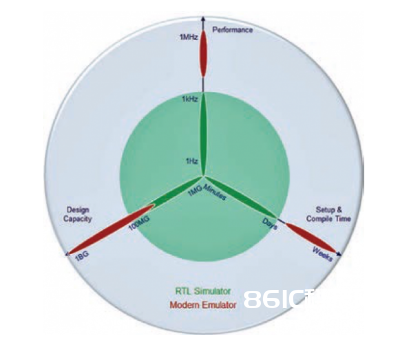

相反,硬件仿真能找到简直一切规划缺点,无论是在硬件中仍是在 SoC 嵌入式软件中。硬件仿真可处理任何规划规划,但需求较长时刻进行环境建立,至少一天,也或许更长时刻。并且,比较软件仿真器,其编译速度相对较慢,大约需求一小时以上才干完结编译(见图 2)。

图 2:根据功用、规划能力和设置/编译时刻的软件仿真与硬件仿真比照

现代硬件仿真器支撑多个并发用户,包含经过长途拜访,因而可添加出资报答。