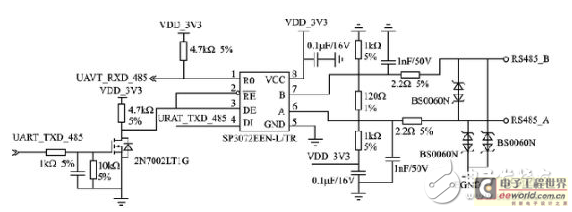

电路原理:图所示为硬件操控RS485的电路图。电路中运用2N7002LT1G MOS场效晶体管把UART_TXD_485这个MCU输出的RS485发送信号逻辑取反后送给RS485芯片的RE/DE PIN脚。操控的原理是,当UART_TXD_485输出低电平时RS485芯片的DE使能;输出高电平时RE使能。默许情况下UART_TXD_485 是高电平,RS485芯片处于接纳状况。发送数据时,UART_TXD_485上面有凹凸电平信号改变,低电平信号经过RS485芯片 SP3072EENL/TR直接输出,高电平信号经过外部上下拉电阻来操控。

这种办法的长处是操控简略,软件不需求做额定的作业,操控RS485像操控RS232相同。可是这种办法的缺陷是驱动才能或许缺乏,因为这种操控办法没有彻底发挥出RS485驱动芯片本身的驱动才能,输出信号依赖于外部上下拉电阻,因此在杂乱环境下,比如许多负载需求操控时,就会存在驱动才能缺乏的问题。可是在一些简略的环境或许软件完成较杂乱的平台下,运用这种办法仍是切实可行的。